# BOSTON UNIVERSITY

# COLLEGE OF ENGINEERING

Dissertation

# CROSS-LAYER DESIGN OF THERMALLY-AWARE 2.5D SYSTEMS

by

# YENAI MA

B.S., University of Alberta, Canada, 2014 M.S., Boston University, 2019

Submitted in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

2020

© 2020 by YENAI MA All rights reserved

## Approved by

First Reader

Ajay J. Joshi, PhD Associate Professor of Electrical and Computer Engineering

Second Reader

Ayse K. Coskun, PhD Associate Professor of Electrical and Computer Engineering

Third Reader

Milos A. Popovic, PhD Associate Professor of Electrical and Computer Engineering

Fourth Reader

Wenchao Li, PhD Assistant Professor of Electrical and Computer Engineering Assistant Professor of Systems Engineering

#### Acknowledgments

First of all, I would like to express my sincere gratitude to my PhD advisor, Prof. Ajay Joshi, for his dedicated support and guidance throughout my PhD study. Prof. Joshi continuously provided encouragement and was always willing and enthusiastic to assist in any way he could on both research and my future career.

I would particularly like to thank Prof. Ayse Coskun for her valuable advice on thermal and EDA related aspects. Discussions with her have always been enlightening and productive. From her, I learned to always keep an eye on the big picture. In addition, I would like to thank the rest of my thesis committee members, Prof. Milos Popovic and Prof. Wenchao Li, and my defense chair Prof. Michel Kinsy, for their precious time, generous support, and insightful feedback.

Many thanks to my collaborators and co-authors for productive collaborations and all the helpful discussions: Prof. Andrew B. Kahng, Dr. Vaishnav Srinivas, Anjun Gu, and John Recchio at University of California San Diego, Prof. Jose L. Abellan at Catholic University of Murcia, Prof. David Kaeli, Dr. Amir K. Ziabari, Yifan Sun, Dana Schaa, and Rafael Ubal at Northeastern University, Prof. John Kim at Korea Advanced Institute of Science & Technology, Prof. Jonathan Klamkin and Warren Jin at University of California Santa Barbara, Dr. Tiansheng Zhang, Furkan Eris, Saiful Mojumder, Aditya Narayan, and Leila Delshadtehrani at Boston University.

I also want to thank all the members of the ICSG research group, the PEACLab research group, and the CAAD research group. They are great collaborators, labmates, and friends, and they made my PhD experience productive and joyful.

Finally, I want to thank my parents and my parents-in-law for their unconditional love and support, expecially my father-in-law. Without his visionary encouragement, I would not start my PhD journey. From the bottom of my heart, I want to say a special thank you to my husband, Dr. Yanchen Lu, who has been a constant source of support and encouragement during the past ten years, especially the last six years of my PhD life. We accomplished many life milestones while pursuing PhD degrees: we engaged, we married, and we have a lovely baby. Thank you to Dr. Yanchen Lu, for making me always optimistic and happy, even during the sleepless nights before deadlines.

# CROSS-LAYER DESIGN OF THERMALLY-AWARE 2.5D SYSTEMS

## YENAI MA

Boston University, College of Engineering, 2020

Major Professor: Ajay J. Joshi, PhD Associate Professor of Electrical and Computer Engineering

#### ABSTRACT

Over the past decade, CMOS technology scaling has slowed down. To sustain the historic performance improvement predicted by Moore's Law, in the mid-2000s the computing industry moved to using manycore systems and exploiting parallelism. The on-chip power densities of manycore systems, however, continued to increase after the breakdown of Dennard's Scaling. This leads to the 'dark silicon' problem, whereby not all cores can operate at the highest frequency or can be turned on simultaneously due to thermal constraints. As a result, we have not been able to take full advantage of the parallelism in manycore systems. One of the 'More than Moore' approaches that is being explored to address this problem is integration of diverse functional components onto a substrate using 2.5D integration technology. 2.5D integration provides opportunities to exploit chiplet placement flexibility to address the dark silicon problem and mitigate the thermal stress of today's high-performance systems. These opportunities can be leveraged to improve the overall performance of the manycore heterogeneous computing systems.

Broadly, this thesis aims at designing thermally-aware 2.5D systems. More specif-

ically, to address the dark silicon problem of manycore systems, we first propose a single-layer thermally-aware chiplet organization methodology for homogeneous 2.5D systems. The key idea is to strategically insert spacing between the chiplets of a 2.5D manycore system to lower the operating temperature, and thus reclaim dark silicon by allowing more active cores and/or higher operating frequency under a temperature threshold. We investigate manufacturing cost and thermal behavior of 2.5D systems, then formulate and solve an optimization problem that jointly maximizes performance and minimizes manufacturing cost. We then enhance our methodology by incorporating a cross-layer co-optimization approach. We jointly maximize performance and minimize manufacturing cost and operating temperature across logical, physical, and circuit layers. We propose a novel gas-station link design that enables pipelining in passive interposers. We then extend our thermally-aware optimization methodology for network routing and chiplet placement of heterogeneous 2.5D systems, which consist of central processing unit (CPU) chiplets, graphics processing unit (GPU) chiplets, accelerator chiplets, and/or memory stacks. We jointly minimize the total wirelength and the system temperature. Our enhanced methodology increases the thermal design power budget and thereby improves thermal-constraint performance of the system.

# Contents

| 1        | Intr              | oduction                                                    | 1                                                                                  |

|----------|-------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------|

|          | 1.1               | Problem Statement                                           | 1                                                                                  |

|          | 1.2               | Thesis Contribution                                         | 4                                                                                  |

|          | 1.3               | Organization                                                | 7                                                                                  |

| <b>2</b> | Bac               | kground and Related Work                                    | 8                                                                                  |

|          | 2.1               | Die-stacking Technologies                                   | 8                                                                                  |

|          | 2.2               | Overview of 2.5D Systems                                    | 9                                                                                  |

|          | 2.3               | Dark Silicon Problem                                        | 11                                                                                 |

|          | 2.4               | Cross-layer methodology                                     | 12                                                                                 |

|          | 2.5               | Thermally-Aware Floorplanning                               | 15                                                                                 |

| 3        | Sing              | gle-Layer Optimization Methodology in Homogeneous 2.5D Sys- |                                                                                    |

|          | tem               | IS                                                          | 16                                                                                 |

|          |                   |                                                             | 10                                                                                 |

|          | 3.1               | Target System                                               | 16                                                                                 |

|          | 3.1<br>3.2        |                                                             |                                                                                    |

|          |                   | Target System                                               | 16                                                                                 |

|          | 3.2               | Target System       Manufacturing Cost Model                | 16<br>18                                                                           |

|          | 3.2<br>3.3        | Target System                                               | 16<br>18<br>21                                                                     |

|          | 3.2<br>3.3<br>3.4 | Target System                                               | <ol> <li>16</li> <li>18</li> <li>21</li> <li>24</li> </ol>                         |

|          | 3.2<br>3.3<br>3.4 | Target System                                               | <ol> <li>16</li> <li>18</li> <li>21</li> <li>24</li> <li>29</li> </ol>             |

|          | 3.2<br>3.3<br>3.4 | Target System                                               | <ol> <li>16</li> <li>18</li> <li>21</li> <li>24</li> <li>29</li> <li>29</li> </ol> |

|   |     | 3.6.1  | Peak Temperature Reduction using 2.5D Integration $\ldots$ . | 31        |

|---|-----|--------|--------------------------------------------------------------|-----------|

|   |     | 3.6.2  | Balancing Performance and Cost of 2.5D Systems               | 32        |

|   | 3.7 | Summ   | nary                                                         | 36        |

| 4 | Cro | ss-Lay | er Co-Optimization Methodology in Homogeneous 2.5D           | )         |

|   |     | tems   |                                                              | <b>37</b> |

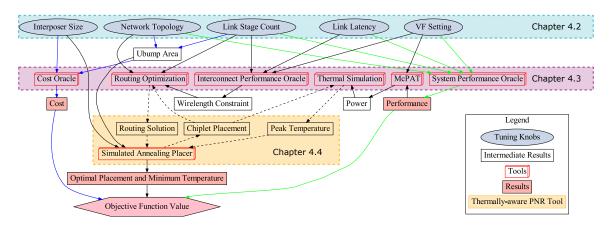

|   | 4.1 | Optim  | nization Problem Formulation and Methodology                 | 38        |

|   | 4.2 | Cross- | layer Optimization Knobs                                     | 42        |

|   |     | 4.2.1  | Logical Layer                                                | 42        |

|   |     | 4.2.2  | Physical Layer                                               | 44        |

|   |     | 4.2.3  | Circuit Layer                                                | 46        |

|   | 4.3 | Evalua | ation Framework                                              | 49        |

|   |     | 4.3.1  | System Performance Oracle                                    | 49        |

|   |     | 4.3.2  | Cost Oracle                                                  | 50        |

|   |     | 4.3.3  | Interconnect Performance Oracle                              | 53        |

|   |     | 4.3.4  | Thermal Simulation                                           | 54        |

|   |     | 4.3.5  | Routing Optimization                                         | 56        |

|   | 4.4 | Thern  | nally-Aware Placement Algorithm                              | 60        |

|   |     | 4.4.1  | Placement Description                                        | 60        |

|   |     | 4.4.2  | Neighbor Placement                                           | 61        |

|   |     | 4.4.3  | Acceptance Probability                                       | 61        |

|   |     | 4.4.4  | Multi-Start and Multi-Phase Techniques                       | 62        |

|   | 4.5 | Evalua | ation Results                                                | 63        |

|   |     | 4.5.1  | Optimal Chiplet Placement Analyses                           | 64        |

|   |     | 4.5.2  | Iso-cost and Iso-performance Analyses                        | 66        |

|   |     | 4.5.3  | Analyses of Different Types of Applications                  | 68        |

|   |     | 4.5.4  | Analyses of Cross-layer Co-optimization Benefits             | 71        |

|          |       | 4.5.5   | Sensitivity Analysis                                        | 73  |

|----------|-------|---------|-------------------------------------------------------------|-----|

|          | 4.6   | Summ    | ary                                                         | 74  |

| <b>5</b> | Cro   | ss-laye | er Optimization Methodology in Heterogeneous 2.5D Sys       | 5-  |

|          | tem   | s       |                                                             | 76  |

|          | 5.1   | Thern   | nal Evaluation                                              | 77  |

|          | 5.2   | Routi   | ng Optimization                                             | 78  |

|          | 5.3   | Therm   | nally-Aware Placement Algorithm                             | 81  |

|          |       | 5.3.1   | Placement description                                       | 82  |

|          |       | 5.3.2   | Initial placement                                           | 83  |

|          |       | 5.3.3   | Neighbor placement                                          | 83  |

|          |       | 5.3.4   | SA cost function                                            | 84  |

|          |       | 5.3.5   | Acceptance probability                                      | 84  |

|          | 5.4   | Evalua  | ation Results                                               | 85  |

|          |       | 5.4.1   | Case Study 1: Multi-GPU System                              | 87  |

|          |       | 5.4.2   | Case Study 2: CPU-DRAM System                               | 88  |

|          |       | 5.4.3   | Case Study 3: Huawei Ascend 910 System                      | 91  |

|          |       | 5.4.4   | Discussion on Scalability                                   | 92  |

|          | 5.5   | Summ    | ary                                                         | 93  |

| 6        | Cor   | clusio  | n and Future Work                                           | 94  |

|          | 6.1   | Summ    | ary of Major Contributions                                  | 94  |

|          | 6.2   | Future  | e Research Directions                                       | 97  |

|          |       | 6.2.1   | Using Machine Learning Techniques to Speed up Evaluations . | 97  |

|          |       | 6.2.2   | Extending Our Methodology for Active Interposer             | 98  |

|          |       | 6.2.3   | Using Photonic Links to Provide High-bandwidth Low-latency  |     |

|          |       |         | Communication                                               | 99  |

| R        | efere | nces    |                                                             | 100 |

## References

Curriculum Vitae

110

# List of Tables

| 3.1 | Dimensions of 2.5D-integrated system.                                    | 17 |

|-----|--------------------------------------------------------------------------|----|

| 3.2 | Notation used in Equations (3.1) through $(3.12)$                        | 19 |

| 4.1 | Notations used in the cross-layer co-optimization methodology            | 40 |

| 4.2 | microbump count, stretch-out width of microbump region $(w_{ubump})$ ,   |    |

|     | and microbump area $(A_{ubump})$ overhead per chiplet for different net- |    |

|     | work topologies designed using repeaterless links, 2-stage and 3-stage   |    |

|     | gas-station links.                                                       | 45 |

| 4.3 | Technology node parameters.                                              | 48 |

| 4.4 | Notations used in the cost oracle                                        | 51 |

| 4.5 | Notations used in routing optimization                                   | 57 |

| 4.6 | Inputs to routing optimization.                                          | 58 |

| 4.7 | Comparison of cross-layer optimization solution against other cases      |    |

|     | that optimize at single layer or two layers. Here O means cross-layer    |    |

|     | optimal choice, W means worst choice, F means prefixed choice, B         |    |

|     | means best choice.                                                       | 72 |

| 5.1 | Thermal modeling of 2.5D systems (Chaware et al., 2012), (Charbon-       |    |

|     | nier et al., 2012)                                                       | 77 |

| 5.2 | Notations.                                                               | 80 |

| 5.3 | Chiplet dimensions and powers in 2.5D examples                           | 86 |

# List of Figures

| 1.1         | 42 years of microprocessor trend data (Rupp, 2018)                                  | 1  |

|-------------|-------------------------------------------------------------------------------------|----|

| $2 \cdot 1$ | Cross-sectional view of a 2.5D integrated system                                    | 11 |

| $3 \cdot 1$ | Impact of defect densities on 2.5D system cost normalized to the single-            |    |

|             | chip system costs at the same defect densities                                      | 20 |

| $3 \cdot 2$ | Impact of chiplet counts, interposer sizes, and power densities on peak             |    |

|             | temperature of 2.5D systems with <b>uniform</b> spacing between chiplets.           | 22 |

| 3.3         | Impact of different heat transfer coefficients of the heatsink (normalized          |    |

|             | to 122 $W/m^2 K$ ) on peak temperature of 16-chiplet 2.5D systems with              |    |

|             | uniform spacing between chiplets.                                                   | 24 |

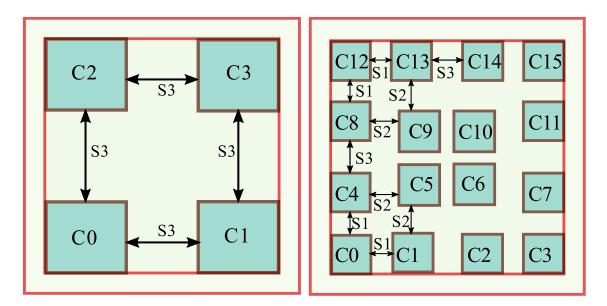

| $3 \cdot 4$ | Chiplet count and placement options. We vary the chiplet spacings                   |    |

|             | independently to find the optimal chiplet placement.                                | 26 |

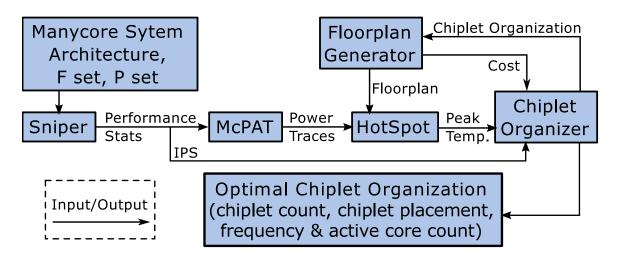

| 3.5         | Evaluation framework.                                                               | 29 |

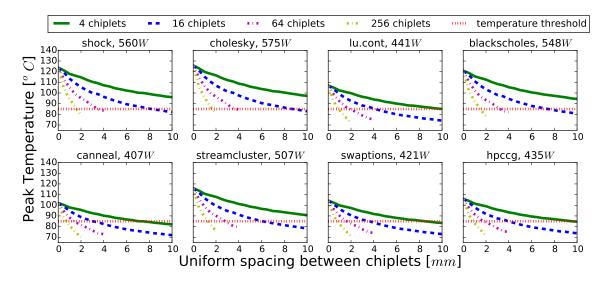

| $3 \cdot 6$ | Peak temperature of a 256-core system with all cores active at 1 $GHz$              |    |

|             | for single-chip case $(0 \ mm)$ and 2.5D integration cases for various              |    |

|             | chiplet counts and spacings (with chiplets placed in a matrix fashion).             | 32 |

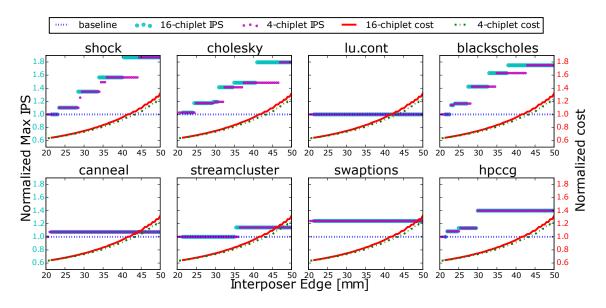

| 3.7         | Maximum IPS and cost of $2.5D$ systems (normalized to maximum IPS                   |    |

|             | and cost of a single-chip system) under 85 $^oC$ for various interposer             |    |

|             | sizes and benchmarks.                                                               | 33 |

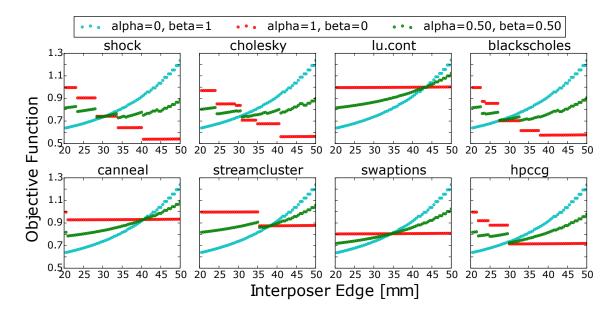

| $3 \cdot 8$ | Minimum objective function (from Equation $(3.7)$ ) value for different             |    |

|             | $(\alpha, \beta)$ pairs across different interposer sizes for different benchmarks. | 35 |

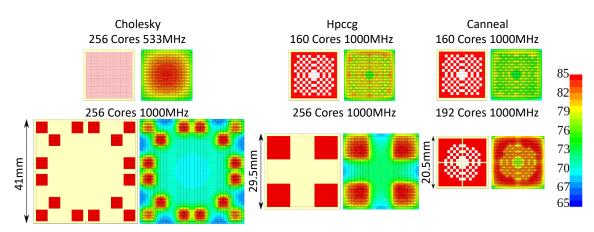

| 3.9         | Choice of chiplet organizations that maximizes the performance under                    |    |

|-------------|-----------------------------------------------------------------------------------------|----|

|             | 85 $^oC$ for single-chip baseline (top) and 2.5D systems (bottom). $\ . \ .$ .          | 35 |

| $4 \cdot 1$ | Cross-layer co-optimization methodology                                                 | 38 |

| $4 \cdot 2$ | Logical view of network topologies. (a)-(b) are unified networks, (c)-(g)               |    |

|             | are used to form hierarchical networks                                                  | 43 |

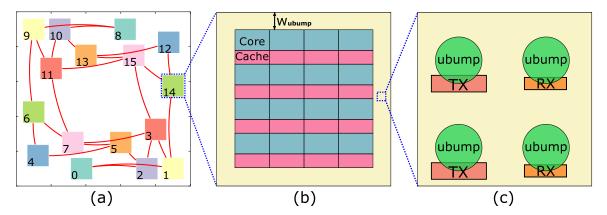

| $4 \cdot 3$ | Illustration of (a) chiplet placement on an interposer with logical con-                |    |

|             | nections, (b) a chiplet with microbump overhead, and (c) microbumps                     |    |

|             | with TX/RX regions (not drawn to scale).                                                | 45 |

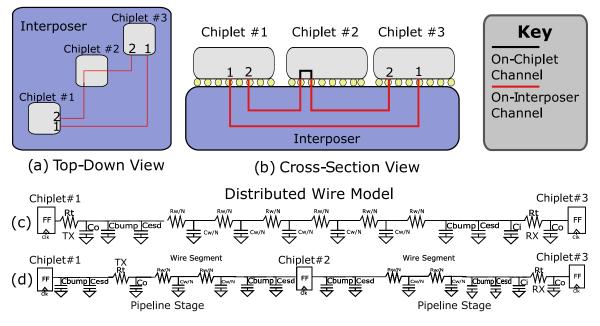

| $4 \cdot 4$ | Illustration of (a) top-down view and (b) cross-section view of inter-                  |    |

|             | chiplet link implementation, and distributed wire models for (c) re-                    |    |

|             | peaterless link (Path 1 in (a)-(b)) and (d) gas-station link (Path 2 in                 |    |

|             | (a)-(b))                                                                                | 47 |

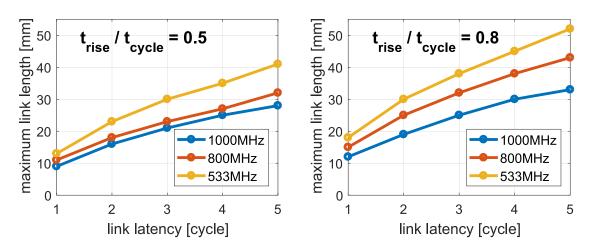

| 4.5         | Maximum reachable inter-chiplet link length w.r.t. clock cycles for                     |    |

|             | various frequencies and rise-time constraints                                           | 49 |

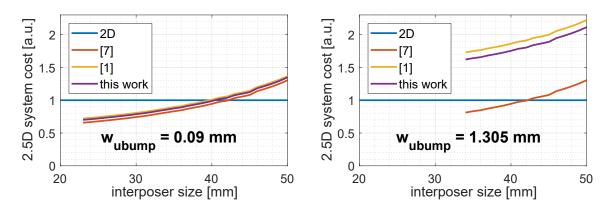

| $4 \cdot 6$ | Comparison between the cost of a 2D system, and the cost of a $2.5D$                    |    |

|             | system estimated using prior cost models (Eris et al., 2018), (Coskun                   |    |

|             | et al., 2018) and our enhanced cost model for interposer sizes from                     |    |

|             | 20 mm to 50 mm and microbump stretch-out widths $(w_{ubump})$ of 0.09 mm                |    |

|             | and 1.305 $mm$ , which correspond to the lower and upper limits of                      |    |

|             | $w_{ubump}$ in our analysis, respectively                                               | 53 |

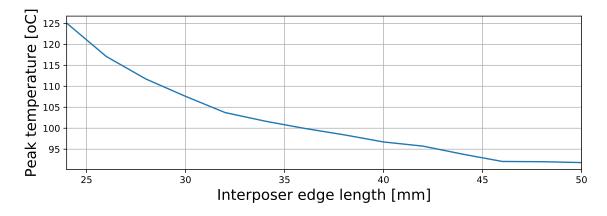

| 4.7         | Temperature of best chiplet placement for each interposer size, running                 |    |

|             | cholesky with <i>Mesh</i> network using single-cycle link without <i>gas stations</i> . | 55 |

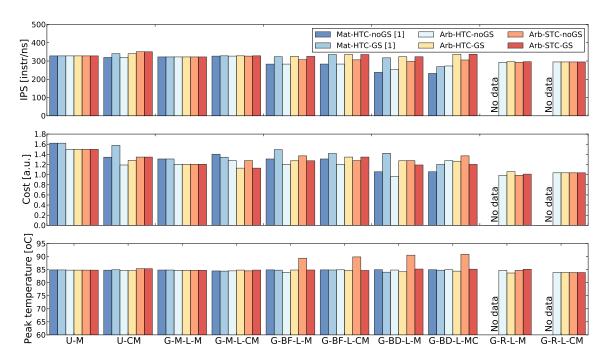

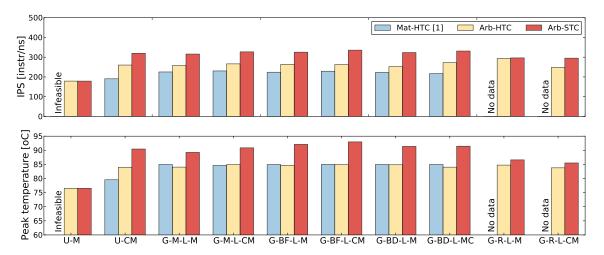

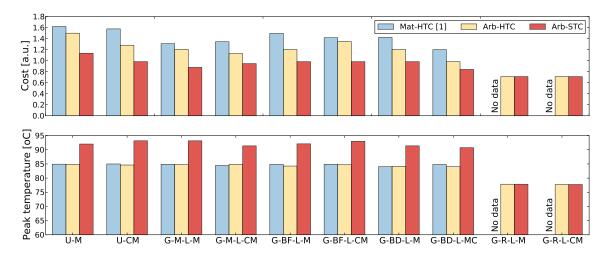

| $4 \cdot 8$  | Maximum performance, the corresponding cost and the corresponding              |    |

|--------------|--------------------------------------------------------------------------------|----|

|              | peak temperature for various networks with and without $gas$ -station          |    |

|              | links when running cholesky benchmark. Here the optimization goal              |    |

|              | is to maximize performance; the cost values are normalized to the cost         |    |

|              | of a 2D system.                                                                | 64 |

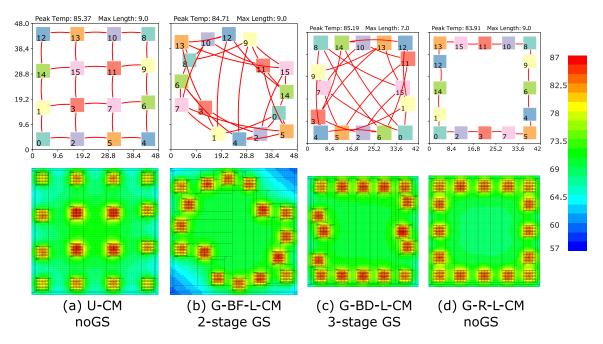

| $4 \cdot 9$  | Optimal chiplet placement for maximum performance and correspond-              |    |

|              | ing thermal maps when running the $cholesky$ benchmark in 2.5D sys-            |    |

|              | tems with different network topologies. The figures are scaled to the          |    |

|              | interposer sizes.                                                              | 66 |

| $4 \cdot 10$ | Iso-cost performance and the corresponding peak temperature when               |    |

|              | running cholesky benchmark for various networks, while not exceed-             |    |

|              | ing the cost budget of a 2D system                                             | 67 |

| 4.11         | Iso-performance cost and the corresponding peak temperature for each           |    |

|              | network. Here the performance is equal to the maximum performance              |    |

|              | achieved using $Mat$ - $HC$ - $GS$ (Coskun et al., 2018) when running cholesky |    |

|              | benchmark. The cost values are normalized to the cost of a 2D system.          | 68 |

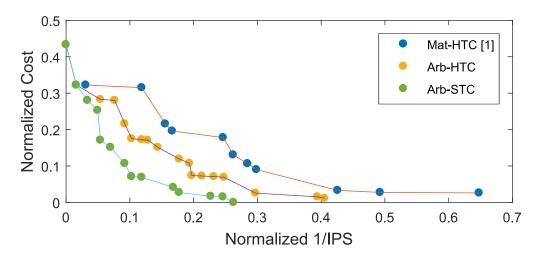

| $4 \cdot 12$ | Pareto Frontier Curve of normalized performance $(1/IPS)$ and nor-             |    |

|              | malized cost using $Mat-HTC$ approach (Coskun et al., 2018), $Arb-HTC$         |    |

|              | approach, and Arb-STC approach.                                                | 69 |

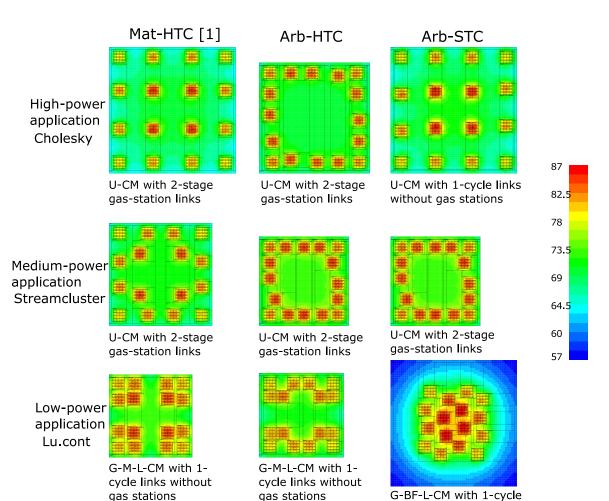

| 4.13         | Thermal maps of 2.5D systems designed for high-power, medium-power,            |    |

|              | and low-power applications using $Mat$ - $HTC$ (Coskun et al., 2018), $Arb$ -  |    |

|              | HTC, $Arb-STC$ approaches. The figures are scaled to the interposer            |    |

|              | sizes                                                                          | 70 |

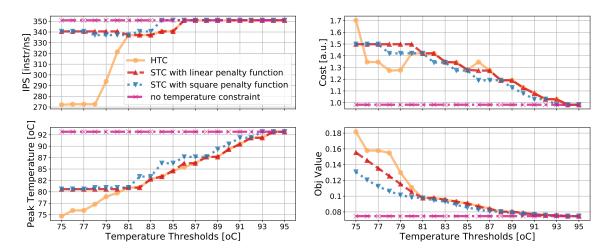

| 4.14         | Sensitivity analysis comparing hard temperature constraint, soft tem-          |    |

|              | perature constraints with linear function and square function, and no          |    |

|              | temperature constraint of various temperature thresholds from 75-95 $^{o}C$ .  | 73 |

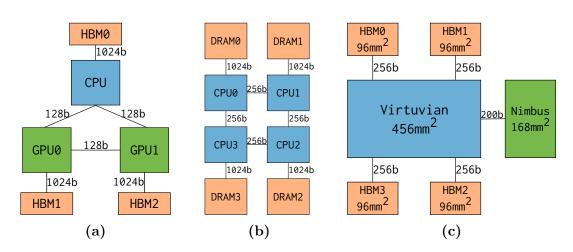

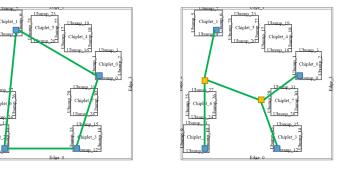

| $5 \cdot 1$ | Logical network topologies for heterogeneous 2.5D examples: (a) a con-             |    |

|-------------|------------------------------------------------------------------------------------|----|

|             | ceptual Multi-GPU System, (b) CPU-DRAM System (Kannan et al.,                      |    |

|             | 2015), and (c) Huawei Ascend 910 System (Huawei, 2019). Numbers                    |    |

|             | shown next to the inter-chiplet links refers to the bit widths                     | 86 |

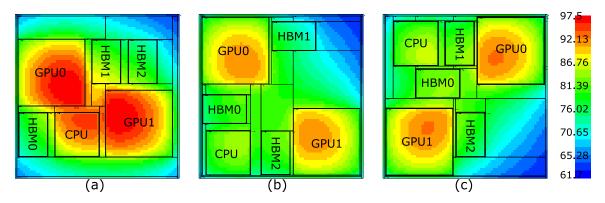

| $5 \cdot 2$ | Thermal maps of a conceptual Multi-GPU System: (a) a placement                     |    |

|             | solution using B*-tree and fast-SA approach, (b) our thermally-aware               |    |

|             | placement solution using repeaterless non-pipelined inter-chiplet links,           |    |

|             | and (c) our placement solution using gas-station links. $\ldots$ $\ldots$ $\ldots$ | 87 |

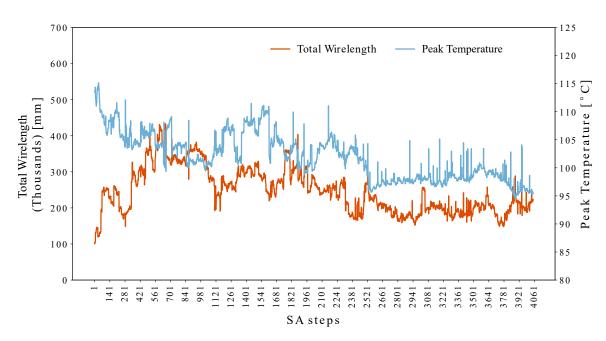

| 5.3         | Wirelength and temperature at each SA step of our simulated anneal-                |    |

|             | ing based algorithm for the Multi-GPU case study.                                  | 88 |

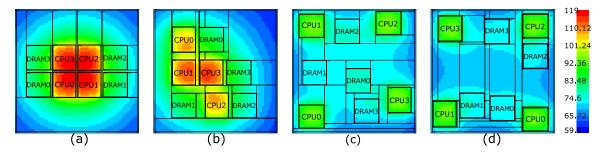

| $5 \cdot 4$ | Thermal maps of the CPU-DRAM System (Kannan et al., 2015): (a)                     |    |

|             | the original placement, (b) a placement solution using B*-tree and                 |    |

|             | fast-SA approach, (c) our thermally-aware placement solution using                 |    |

|             | repeaterless non-pipelined inter-chiplet link, and (d) using $gas$ -station        |    |

|             | links                                                                              | 89 |

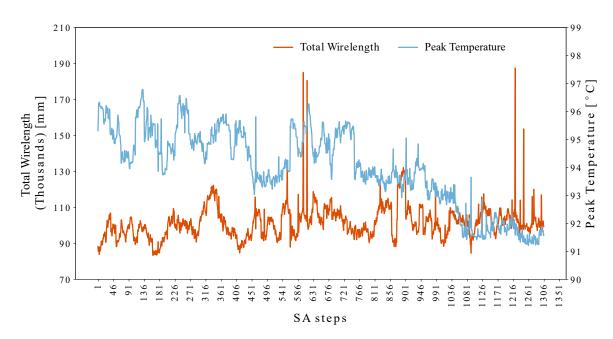

| $5 \cdot 5$ | Wirelength and temperature at each SA step of our simulated anneal-                |    |

|             | ing based algorithm for the CPU-DRAM case study                                    | 90 |

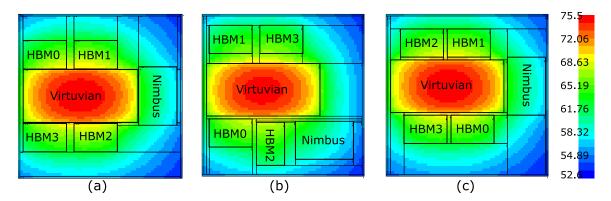

| $5 \cdot 6$ | Thermal maps of the existing Huawei Ascend 910 System (Huawei,                     |    |

|             | 2019): (a) the exact placement layout, (b) a placement solution using              |    |

|             | B*-tree and fast-SA approach, and (c) our thermally-aware placement                |    |

|             | solution.                                                                          | 91 |

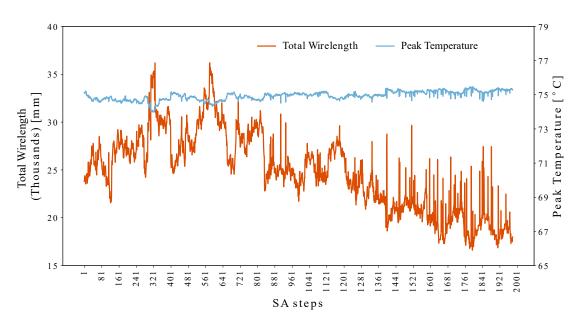

| 5.7         | Wirelength and temperature at each SA step of our simulated anneal-                |    |

|             | ing based algorithm for the Ascend 910 case study. $\ldots$ . $\ldots$ .           | 92 |

| 6.1         | Router Placement in (a) passive interposer and (b) active interposer.              | 98 |

|             |                                                                                    |    |

# List of Abbreviations

| 2.5D                | <br>2.5 Dimensional                        |

|---------------------|--------------------------------------------|

| AP                  | <br>Acceptance Probability                 |

| Arb                 | <br>Arbitrary placement of chiplets        |

| AWS                 | <br>Amazon Web Service                     |

| BEOL                | <br>Back-End-Of-Line                       |

| CPU                 | <br>Central Processing Unit                |

| DVFS                | <br>Dynamic Voltage and Frequency Scaling  |

| EMIB                | <br>Embedded Multi-die Interconnect Bridge |

| FEOL                | <br>Front-End-Of-Line                      |

| GPU                 | <br>Graphics Processing Unit               |

| $\operatorname{GS}$ | <br>Gas Stations                           |

| HBM                 | <br>High-Bandwidth Memory                  |

| HMC                 | <br>Hybrid Memory Cube                     |

| HPC                 | <br>High Performance Computing             |

| HTC                 | <br>Hard Temperature Constraint            |

| Mat                 | <br>Matrix-style chiplet placement         |

| MILP                | <br>Mixed Integer-Linear Program           |

| noGS                | <br>no Gas Stations                        |

| PNR                 | <br>Place aNd Route                        |

| ROI                 | <br>Region Of Interest                     |

| RX                  | <br>Receiver                               |

| SA                  | <br>Simulated Annealing                    |

| SCC                 | <br>Single-chip Cloud Computer             |

| SiP                 | <br>System-in-Package                      |

| STC                 | <br>Soft Temperature Constraint            |

| TDP                 | <br>Thermal Design Power                   |

| $\mathrm{TSV}$      | <br>Through-silicon vias                   |

| ТΧ                  | <br>Transmitter                            |

# Chapter 1 Introduction

## 1.1 Problem Statement

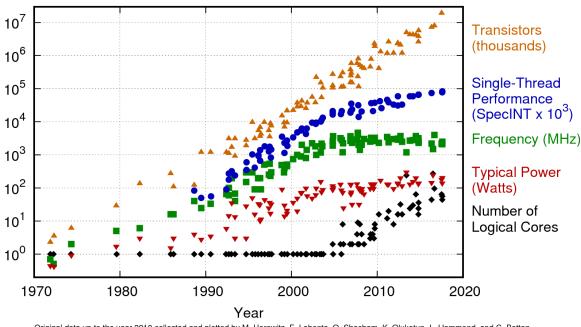

Moore's Law (Schaller, 1997), which has dominated the computing industry since the 1960s, is approaching the end. With voltage scaling no longer in line with the transistor size, the power density is increasing quickly as the transistor size shrinks. This is known as the breakdown of Dennard's Scaling (Dennard et al., 1974). As a result, the 'free-lunch' performance improvement from scaling has stopped since 2004 (as shown in Figure 1.1).

Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten New plot and data collected for 2010-2017 by K. Rupp

Figure 1.1: 42 years of microprocessor trend data (Rupp, 2018)

To continue the performance improvement predicted by Moore's Law despite the speed limit, the computing industry has been exploring 'More-than-Moore' approaches (Waldrop, 2016), (ITRS, 2015a). A common 'More-than-Moore' approach is to pack many cores on a single die and use parallelism to improve performance, as shown in Figure 1.1. However, although we have enough transistors to support many cores on a chip, we cannot use all of them because of the 'dark silicon' problem (Esmaeilzadeh et al., 2011). Dark silicon is the phenomenon that not all cores can be operated at the highest frequency or even turned ON simultaneously due to thermal design power (TDP) constraint. This leads to inactive regions on the chip and limits the performance of manycore systems. To address the dark silicon problem, researchers have proposed a variety of solutions through hardware level to system management level such as dynamic voltage and frequency scaling (DVFS) (Muthukaruppan et al., 2013), (Swaminathan et al., 2013), (Allred et al., 2012), designing customized hardware (Venkatesh et al., 2011), (Goulding-Hotta et al., 2011), near-threshold computing (Dreslinski et al., 2010), (Silvano et al., 2014), approximate computing (Han and Orshansky, 2013), (Kulkarni et al., 2011), power budgeting (Pagani et al., 2014), and computational sprinting (Raghavan et al., 2012). While some of these dark silicon solutions may apply to manycore systems, they do not focus on the challenge specific to manycore systems, which is to run a larger number of cores persistently.

Another path that has been taken to sustain the historical performance improvement involves integrating diverse functional components into a package (ITRS, 2015a). This transformation focuses on the overall system performance and cost rather than on individual components to push the system-level scaling, and heterogeneous integration is the backbone of this approach (Iyer, 2016). Thus, die-stacking technologies, such as 2.5D and 3D integration (Loh et al., 2007), (Kannan et al., 2015), (Stow et al., 2016), have emerged to support heterogeneous integration. 2.5D integration places multiple dies side-by-side on a silicon interposer, while 3D integration stacks dies vertically. These die-stacking technologies offer both high bandwidth and reduced latency (Kannan et al., 2015), which could be utilized to handle the growing data traffic requirements of today's applications (ITRS, 2015a).

This new trend of heterogeneous systems poses many opportunities and challenges. As more functional components are packed in the same package, thermal dissipation becomes more critical. Therefore, although 3D integration has been proven to be a popular option in memory design (Waldrop, 2016), it is not a good candidate for highperformance computing because of the high power density resulting from the vertical stacking of dies (Loh et al., 2007). 2.5D integration is often less prone to the thermal challenges aggravated by 3D stacking (Stow et al., 2016), but still requires good heat dissipation capability. Although there are already interposer-based commercial products in the market, such as Xilinx Virtex 7 (Xilinx, 2016), AMD Fiji (Macri, 2015), Nvidia Tesla (Nvidia, 2016), and Intel Foveros (Intel, 2018), they typically place the chiplets next to each other on an interposer to embrace the benefits of low communication latency due to short inter-chiplet links and low manufacturing cost resulting from small interposer sizes. The design and optimization of 2.5D systems, including chiplet placement, inter-chiplet network architecture, design of inter-chiplet links and microbump assignment, need to be thoroughly explored to maximize the benefits of 2.5D integration (ITRS, 2015b). Especially, the opportunities of leveraging 2.5D integration technology to maximize system heat dissipation and lower operating temperature have not been discussed and utilized in prior works.

In 2.5D system design, a top-down or a bottom-up approach is typically used. However, both of them lead to sub-optimal solutions. Consider the following two examples that highlight the need for a cross-layer approach. (1) If we adopt a topdown performance-centric approach, an architecture-level analysis of network topologies indicates that high-radix, low-diameter networks provide the best overall system performance for inter-chiplet networks. However, in the physical layer, such networks usually require long wires, which would limit the network performance, and hence, the overall system performance. In the circuit layer, such long wires require active (rather than passive) interposer to house repeaters and/or pipelines to maintain high performance. Since active interposers are  $10 \times$  more expensive than passive interposers (Parès, 2013), the system cost becomes expensive and so the top-down approach does not provide a desirable solution. (2) A bottom-up, cost-centric approach prefers to use passive interposers, which can only support repeaterless links in the circuit layer, thus degrading link performance and limiting maximum link length between chiplets in the physical layer. Consequently, in the logical layer, we have to adopt low-radix, high-diameter inter-chiplet networks, which result in a lowperformance system. Therefore, a cross-layer optimization methodology is needed for designing 2.5D systems.

#### **1.2** Thesis Contribution

At a broader level, this thesis aims to tackle the challenges in designing thermallyaware 2.5D systems. As a first step, we focus on homogeneous manycore systems, and propose a thermally-aware chiplet organization methodology to address the dark silicon problem. The main idea is to separate a single-chip manycore system into multiple chiplets and strategically insert spacing in between by leveraging the placement flexibility of 2.5D integration technology. We optimize the chiplet organization to jointly maximize performance and minimize manufacturing cost. Then we extend our thermally-aware chiplet organization methodology to optimize performance, manufacturing cost and peak operating temperature across logical, physical, and circuit layers. Our methodology jointly considers network topology, physical chiplet placement, and inter-chiplet interconnect design and routing. We propose a novel inter-chiplet link design, named gas-station links, to enable pipelining in a cost-effective passive interposer instead of using expensive active interposer. For heterogeneous systems, we leverage 2.5D integration technology and extend our thermally-aware chiplet organization methodology to systems consisting of CPUs, GPUs, memory stacks, and/or accelerators. We formulate a multi-objective optimization framework to floorplan the heterogeneous components in a thermally-aware fashion and optimize the routing of the inter-chiplet interconnects between these components of the heterogeneous 2.5D system. The main contributions of my PhD research are as follows.

• Leveraging Thermally-Aware Chiplet Organization in Homogeneous 2.5D Systems to Reclaim Dark Silicon: We are the first to propose a thermally-aware chiplet organization methodology to address the dark silicon problem in homogeneous manycore systems. The key idea is to divide a large monolithic chip into multiple smaller chiplets and intelligently place these chiplets on a passive silicon interposer in a thermally-aware fashion. We strategically insert spacing between the chiplets of a 2.5D manycore system to lower the peak operating temperature and thus reclaim dark silicon by allowing the system to operate with a larger number of active cores and/or at a higher operating frequency without violating the thermal constraints. We investigate manufacturing cost and thermal behavior of chiplet-based 2.5D systems, formulate and solve an optimization problem that jointly maximizes performance and minimizes manufacturing cost of the 2.5D manycore systems. We design a multi-start greedy approach to find (near-)optimal solutions efficiently. Our analysis demonstrates that by using our proposed technique, an optimized 2.5D many core system improves performance by 41% and 16% on average and by up to 87% and 39% for temperature thresholds of 85  $^{o}C$  and 105  $^{o}C$ , respectively, compared to a traditional single-chip system at the same manufacturing cost. When maintaining the same performance as an equivalent single-chip system, our thermally-aware chiplet organization approach is able to reduce the 2.5D system manufacturing cost by 36%.

• Cross-Layer Co-Optimization of Network Design and Chiplet Placement in Homogeneous 2.5D Systems: We generalize our thermally-aware chiplet organization methodology to explore the tradeoffs across logical, physical, and circuit layers and form a cross-layer co-optimization methodology. The outcome of our methodology includes the design choice of network topology, chiplet placement, inter-chiplet link design and routing. Our cross-layer methodology jointly optimizes performance, manufacturing cost, and operating temperature of 2.5D systems. We use a soft constraint for peak temperature in the optimization problem to achieve better overall performance gain or cost reduction by allowing a small amount of thermal violation, while still ensuring thermal safety and routability. In order to maintain cost-effective and highperformance communication between chiplets in 2.5D systems, we propose a novel *qas-station* link which enables pipelining between chiplets in a passive interposer. We develop a simulated annealing algorithm to search the highdimensional placement solution space, which supports arbitrary placements that consider non-matrix and asymmetric chiplet organizations. Our crosslayer methodology achieves better performance-cost tradeoffs of 2.5D systems and yields better solutions in optimizing inter-chiplet network and 2.5D system designs than prior methods. Compared to single-chip systems, 2.5D systems designed using our new approach achieve 88% higher performance at the same manufacturing cost or 29% lower cost with the same performance. Compared to the closest state-of-the-art (Coskun et al., 2018), our new approach achieves 40-68% (49% on average) iso-cost performance improvement and 30-38% (32% on average) iso-performance cost reduction.

• Inter-Chiplet Network Design in Heterogeneous 2.5D Systems: We propose a methodology for efficient routing of inter-chiplet wires and thermally-aware placement of chiplets in heterogeneous 2.5D systems, which integrate various components such as CPUs, GPUs, memory stacks, and/or accelerators on a silicon interposer. Our methodology jointly minimizes the total wirelength and the system temperature with strategic insertion of spacing between chiplets. We develop an SA-based approach to optimize the routing of inter-chiplet wires and thermally-aware chiplet placement for heterogeneous 2.5D systems. We enhance the traditional floorplanning algorithm for monolithic chips to support 2.5D systems. We use a flexible data structure to represent chiplet placement with strategically inserted spacing, which is not supported in traditional floorplan data structures. Our methodology increases the TDP without using any advanced and costly active cooling methods. This increase in TDP envelope allows higher power budget, which can be used to improve performance.

## 1.3 Organization

The rest of this thesis start with a review of the background and related work on die-stacking technologies, an overview of 2.5D systems, the dark silicon problem, cross-layer methodology, and thermally-aware floorplanning in Chapter 2. Chapter 3 introduces our work on single-layer optimization methodology in homogeneous 2.5D systems. Chapter 4 presents our work on cross-layer co-optimization methodology in homogeneous 2.5D systems. Then in Chapter 5 we show how we extended our cross-layer optimization methodology to heterogeneous 2.5D systems. Chapter 6 discusses future directions and concludes the thesis.

# Chapter 2 Background and Related Work

In this chapter we provide an overview of background and related work on die-stacking technologies, 2.5D systems, the dark silicon problem, cross-layer methodology, and thermally-aware floorplanning.

## 2.1 Die-stacking Technologies

Die-stacking technologies, such as 2.5D integration and 3D integration, have emerged as a popular "More than Moore" approach to continue the computing performance improvement (Loh et al., 2007), (Kannan et al., 2015), (Stow et al., 2016). The multidie systems using either 2.5D integration or 3D integration technology are viewed as cost-effective alternatives to single-chip systems (also called 2D systems), as breaking down a chip into multiple chiplets alleviates the manufacturing yield drop suffered in a large 2D chip. These technologies also enable the design of System-in-Package (SiP) that consists of multiple heterogeneous functional chiplets (CPU, GPU, memory, etc.) fabricated using different technologies and processes to further push the system-level improvement of performance and cost (HIR, 2019), (ITRS, 2015a). 3D integration stacks chiplets vertically on top of each other to form a system and uses throughsilicon vias (TSVs) to communicate between chiplets. It reduces system footprint, communication distance, and increases memory bandwidth (Kannan et al., 2015). However, the vertical stacking of chiplets exacerbates the thermal challenges (Loh et al., 2007). Therefore, 3D integration has been a popular option in memory design (Waldrop, 2016), such as Hybrid Memory Cube (HMC) (Jeddeloh and Keeth, 2012) and High-Bandwidth Memory (HBM) (Tran et al., 2016), but it is rarely used for thermally-stressed high-power systems. 2.5D integration places the chiplets side by side on a silicon interposer. The chiplets communicate with each other through high-density fine-grained microbumps and interconnects in the interposer. 2.5D integration provides additional routing resources through the interposer, and thus supports high-density die-to-die communication (Kannan et al., 2015). Compared to 3D integration, 2.5D integration requires larger X-Y size while 3D systems are more compact. 2.5D integration technology is more mature and cost-effective while 3D integration technology often requires redesigning the chiplets to account for the TSV overhead and alignment (Radojcic, 2017). Moreover, 2.5D integration is less prone to the thermal challenges observed in 3D systems (Stow et al., 2016).

### 2.2 Overview of 2.5D Systems

2.5D integration is a promising technology that enables the integration of homogeneous or heterogeneous sets of chiplets onto a carrier. The carrier provides additional wiring resources that can be leveraged to increase the communication bandwidth between the chiplets and improve system performance (Jerger et al., 2014). Furthermore, 2.5D integration is more cost effective than building large 2D chips and is more thermally efficient than 3D-stacked systems (Stow et al., 2016). Currently, 2.5D integration technology is being widely explored by both academia (Jerger et al., 2014), (Kannan et al., 2015), (Grani et al., 2016), (Stow et al., 2016), (Stow et al., 2017), (Karim et al., 2013) and industry (Xilinx, 2016), (Chaware et al., 2012), (Macri, 2015), (Urino et al., 2014), (Nvidia, 2016), (Intel, 2018).

There are multiple options for 2.5D integration technology. Embedded Multidie Interconnect Bridge (EMIB) (Intel, 2019), (Hot Chips, 2017) and silicon interposer (Xilinx, 2016) are two commonly used carrier options. EMIB is a novel integration method, which embeds small pieces of silicon interconnect bridge chips in the organic package substrate to connect the edges of adjacent chiplets for die-to-die communication. Silicon interposer technology uses a relatively large interposer to house all chiplets. It is more mature and has already been used in commercial products (Xilinx, 2016), (Macri, 2015). Both EMIB and silicon interposer can provide high density die-to-bridge and die-to-interposer connections, respectively, and correspondingly, high-density die-to-die connections (Hot Chips, 2017). EMIB-based approach requires less silicon area than silicon interposer-based approach and thus has lower silicon cost (Hot Chips, 2017). However, EMIB has limited die-to-die connections per layer (Ramalingam, 2016), and also has higher complexity in the manufacturing of organic substrates (Mahajan et al., 2016). Furthermore, EMIB can only hook up adjacent chiplets and requires multi-hop communication for logically connected chiplets that are physically placed far apart.

Interposer-based integration, including active interposers and passive interposers, provides more flexibility in chiplet placement, network design and interconnect routing. Thus, it has better thermal dissipation capability as it does not require chiplets to be placed close to each other. An active interposer is effectively a large carrier chip containing transistors to house other chiplets. It is expensive as it requires front-end-of-line (FEOL) process and suffers from yield loss when the area is large. A passive interposer is transistor-free, so it can be fabricated using back-end-of-line (BEOL) process and inherently has high yield (Parès, 2013). Thus, a passive interposer is much cheaper than an active interposer (\$500 per wafer without yield loss for passive interposer vs. \$5000 per wafer with yield loss for active interposer (Parès, 2013)). In this thesis, we focus on passive interposer based 2.5D integration, which provides both cost effectiveness and placement flexibility.

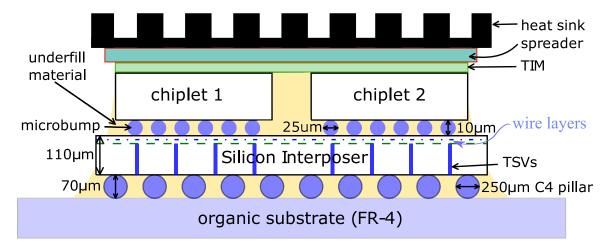

Figure 2.1 shows the cross-section view of a passive interposer based 2.5D system. A 2.5D-integrated system consists of three main layers: an organic substrate, a silicon interposer, and a chiplet layer. Fine-pitch microbumps connect the chiplets and the silicon interposer. Through-silicon vias (TSVs) connect the top and the bottom of the interposer, and C4 bumps connect the interposer and the organic substrate. Epoxy resin is often used to underfill the connection layers (C4 bumps layer and microbumps layer) and the empty spaces between chiplets (Zhang and Wong, 2004).

Figure 2.1: Cross-sectional view of a 2.5D integrated system.

#### 2.3 Dark Silicon Problem

In manycore systems, dark silicon is the phenomenon where not all cores can operate at the highest frequency or can be turned ON simultaneously due to thermal design power (TDP) constraints. Over the past few years, a number of solutions have been proposed to alleviate the dark silicon problem. The proposed solutions include the use of specialized cores (Venkatesh et al., 2011), (Goulding-Hotta et al., 2011), DVFS (Muthukaruppan et al., 2013), (Yan et al., 2012), near-threshold computing (Dreslinski et al., 2010), (Silvano et al., 2014), approximate computing (Han and Orshansky, 2013), (Kulkarni et al., 2011), power budgeting (Pagani et al., 2014), and computational sprinting (Raghavan et al., 2012). A specialized core is applicationspecific and enables efficient execution of that specific application with a smaller number of transistors. However, a specialized core cannot execute other types of applications efficiently. Applying DVFS degrades system performance, while nearthreshold computing and approximate computing trade off accuracy and reliability for energy efficiency. Power budgeting enables operating at a thermally-safe power instead of a constant TDP to achieve a higher total performance. Computational sprinting (where the system runs with a larger number of cores in short bursts) incorporates phase-change materials for higher thermal capacitance, and thus allows violation of the thermal power budget for a short time. Power budgeting and computational sprinting, however, require a 'cooling down' period after the performance boost. Hence, these works cannot harness the full potential of manycore systems persistently.

Our work (Eris et al., 2018) leverages the placement flexibility and cost effectiveness of 2.5D systems to tackle the dark silicon problem. We strategically place chiplets in a thermally-aware fashion to facilitate heat dissipation, and thus raise the thermally-safe power budget without additional cooling cost to improve performance persistently.

#### 2.4 Cross-layer methodology

2.5D integration of smaller chiplets on a large interposer has been demonstrated to achieve a higher compute throughput per watt (or volume) than a single large die (Stow et al., 2017), (Knickerbocker et al., 2012). Several related studies have explored the design and optimization of 2.5D systems, with primary focus being placed on individual design layers: logical, physical, and circuit.

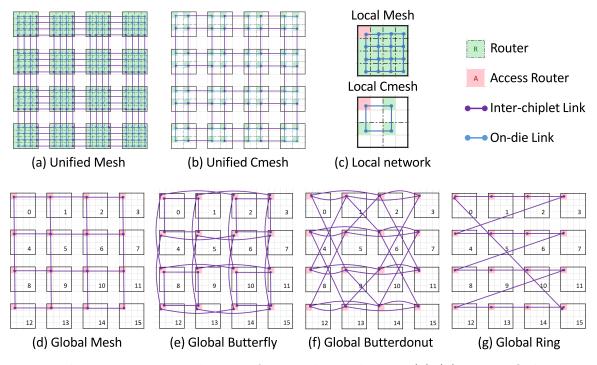

At the logical layer, Jerger et al. (Jerger et al., 2014) present a hybrid network

topology between the cores and memory. They account for different coherence and memory traffic characteristics across applications, and design a hybrid network-onchip (NoC) that has low latency and high throughput. In their follow-up work, Kannan et al. (Kannan et al., 2015) evaluate the impact of different network topologies on 2.5D systems, and demonstrate that disintegration of a large 2D chip into multiple chiplets improves manufacturing yield and lowers costs. However, their work overlooks the microbump overhead. Ahmed et al. (Ahmed et al., 2017) identify that interposer's routing resources are highly under-utilized due to the high interconnect pitch in 2.5D systems. To maximize performance, they propose a hierarchical mesh network for inter-chiplet communication. Akgun et al. (Akgun et al., 2016) perform a design space exploration of different memory-to-core network topologies and routing algorithms. However, a static placement of chiplets in their work limits a complete cross-layer exploration that leaves much of the performance benefits in 2.5D systems untapped. While these works aim to maximize the system performance under different traffic conditions, they do not account for the thermal impact and a complete manufacturing cost model in the NoC design and optimization. In addition, these works do not consider different chiplet placement and link routing options.

At the physical layer, there have been several optimization-based approaches aimed at providing routing and placement solutions for 2.5D systems. Placing chiplets closer to each other results in lower manufacturing cost and higher performance (reduced wirelength), but higher temperature. Therefore, finding a thermally-aware placement and routing solution that maximizes performance and/or minimizes cost is essential in 2.5D systems. Osmolovskyi *et al.* (Osmolovskyi et al., 2018) optimize the chiplet placement to reduce the interconnect length using pruning techniques. Ravishankar *et al.* (Ravishankar et al., 2018) determine the quality of different placement options in a 2D grid using a stochastic model and implement a placer for 2.5D FPGAs. Seemuth *et al.* (Seemuth et al., 2015) consider the increased design solution space in 2.5D systems due to flexible I/Os in their chiplet placement problem. They present a method for die placement and pin assignment using simulated annealing to minimize the total wirelength. Much of the focus of routing in 2.5D systems has been placed on minimizing IR drops and total wirelength in inter-chiplet links (Fang et al., 2015) and minimizing the number of metal layers (Liu et al., 2014). None of these physical layer optimization solutions consider thermal effects.

Prior research at the circuit layer of 2.5D systems generally focuses on link optimization techniques to improve the network and system throughput. Karim *et al.* (Karim et al., 2013) evaluate the power efficiency of electrical links with and without electrostatic discharge (ESD) capacitance. Stow *et al.* (Stow et al., 2017) evaluate both repeater and repeaterless links to explore the benefits of active and passive interposers respectively. There have also been efforts on using emerging technologies like wireless links (Shamim et al., 2017) and silicon-photonic links for communication in 2.5D systems (Grani et al., 2017), (Kim et al., 2017), (Narayan et al., 2019).

A common drawback among these previous works is that their design and optimization only focus on a single design layer. In contrast, in our work (Coskun et al., 2018), (Coskun et al., 2020) we optimize the cost, performance and temperature by jointly considering the logical, physical and circuit layers of the inter-chiplet network. We evaluate various logical topologies and their feasibilities at the physical and circuit layer. At the physical layer, we design an overlap-free and thermally-safe routing and placement solution that results in the lowest cost and operating temperature. The circuit layer provides us with multiple circuit design options for inter-chiplet links. Our cross-layer methodology, thus, presents a rich solution space to evaluate a variety of network options at different design layers for 2.5D systems, thus enabling accurate and complete modeling of such systems.

#### 2.5 Thermally-Aware Floorplanning

In addition to the traditional design objectives, such as area and wirelength, many floorplanning works consider the thermal aspect. A number of previous approaches have introduced thermally-aware floorplanning methods to reduce hot spots while optimizing area (Hung et al., 2005), to reduce peak temperature inside a microprocessor (Sankaranarayanan et al., 2005), and to reduce peak temperature and thermal gradients of 3D ICs (Frantz et al., 2012). Healy *et al.* (Healy et al., 2006) present a multiobjective microarchitectural floorplanning algorithm for 2D and 3D systems to achieve both high performance and thermal reliability. Cong *et al.* (Cong et al., 2004) propose a thermal-driven 3D floorplanning algorithm. All of these works consider placement of components to reduce temperature, but they do not focus on placement on a 2.5D interposer. In addition, these works are limited to compact placement, which cannot be applied to 2.5D systems to leverage the placement flexibility with a larger solution space. In contrast, we offer a thermally-aware chiplet placement approach that strategically adjusts spacing among chiplets on 2.5D systems to reduce the peak temperature.

# Chapter 3

# Single-Layer Optimization Methodology in Homogeneous 2.5D Systems

In this chapter, we discuss our optimization methodology for single-layer thermallyaware chiplet organization. We use a homogeneous 256-core manycore system as the target system. All the chiplets in our system have same architecture and size, as discussed in Section 3.1. We investigate manufacturing cost model of 2.5D systems in Section 3.2, perform a detailed design space exploration of chiplet thermal behavior in Section 3.3, formulate and solve an optimization problem in Section 3.4, demonstrate our simulation framework in Section 3.5, and discuss the results in Section 3.6.

## 3.1 Target System

We use a 256-core homogeneous system as our example manycore system. The core architecture of the 256-core system is based on the IA-32 core from Intel Single-chip Cloud Computer (SCC) (Howard et al., 2011), with size and power scaled to 22 nm technology (Zhang et al., 2014). Each core has a 16 KB I/D L1 cache and a 256 KB private L2 cache. The area of each core (including L1 cache) is 0.93  $mm^2$ , and the area of each L2 cache is 0.35  $mm^2$ . We assume each L2 cache is placed next to the corresponding core, and each core together with its L2 cache is square shaped, with an area of 1.28  $mm^2$  (1.13  $mm \times 1.13 mm$ ) (Zhang et al., 2014). The total size of the 256-core chip is 18  $mm \times 18 mm$ .

We split the 256-core single chip into chiplets and form a 2.5D system as described

in Figure 2.1 and Section 2.2. The interposer is passive and designed using 65 nm technology. The dimensions of the 2.5D system (shown in Table 3.1) are based on the prototypes from CEA-Leti (Charbonnier et al., 2012) and Xilinx (Chaware et al., 2012). Our evaluation uses the conventional 2D single-chip system as a baseline, where the 256-core chip is placed directly on top of an organic substrate using C4 bumps for connection.

| Layers             | Thickness                                   | Materials             |               |

|--------------------|---------------------------------------------|-----------------------|---------------|

| Heat Sink          | 6.9 mm                                      |                       |               |

| Spreader           | 1 mm                                        |                       |               |

| Interface Material | $20 \ \mu m$                                |                       |               |

| CMOS Chiplet Layer | S Chiplet Layer $150 \ \mu m$ Silicon, Epox |                       | on, Epoxy     |

| Microbump Layer    | $10 \ \mu m$                                | Copper, Epoxy         |               |

| Silicon Interposer | $110 \ \mu m$                               | Silicon, Copper (TSV) |               |

| C4 Layer           | $70 \ \mu m$                                | Copp                  | er, Epoxy     |

| Organic Substrate  | $200 \ \mu m$                               | FR-4                  |               |

| Component          | Diameter                                    | Height                | Pitch         |

| Microbumps         | $25 \ \mu m$                                | $10 \ \mu m$          | $50 \ \mu m$  |

| $\mathrm{TSVs}$    | $10 \ \mu m$                                | $100 \ \mu m$         | $50 \ \mu m$  |

| C4 bumps           | $250~\mu m$                                 | $70 \ \mu m$          | $600 \ \mu m$ |

Table 3.1: Dimensions of 2.5D-integrated system.

We use an electrical mesh network (single-cycle routers and single-cycle links) for the example 256-core system. Intra-chiplet communication is through on-chiplet interconnects, while inter-chiplet communication is through links in the interposer. We use DSENT (Sun et al., 2012) to calculate power of on-chip links and routers, and HSpice (HSPICE, 2009) to compute power of inter-chiplet links based on a 2.5D interconnect model (Karim et al., 2013). We size up the drivers to ensure single-cycle propagation delay in the inter-chiplet links. The electrical mesh in the 2.5D system consumes upto 8.4 W, based on real benchmarks activities obtained from Sniper (Carlson et al., 2011). An electrical mesh network with the same micro architecture consumes 3.9 W in case of a single-chip system. Essentially, we trade off power

to match the performance of the network in the 2.5D system with that in a single-chip system. This power increase, however, has negligible impact on the thermal profile of the whole system.

#### 3.2 Manufacturing Cost Model

The cost benefit of 2.5D systems has already been discussed in prior work (Stow et al., 2016), (Kannan et al., 2015), where a 20% to 30% reduction in cost can be achieved by replacing a single chip with a 4-chiplet 2.5D system. Smaller chiplets utilize more wafer area around the edge and achieve higher yield (Kannan et al., 2015), thus, leading to lower cost per unit area. Though an extra interposer is needed to integrate these small chiplets, the cost is rather low in case of a passive interposer (typically \$500 per 300 mm diameter wafer (Pares, 2013)) because it can be manufactured using older process technologies (Chaware et al., 2012), and with high yield (as much as 98%) (Tran et al., 2016).

To estimate the cost of our 2.5D systems, we adopt the manufacturing cost model proposed by Stow et al. (Stow et al., 2016), which takes into account the cost and yield of CMOS chiplets, microbump bonding, and interposer, assuming known good dies<sup>1</sup>. All notations are listed in Table 3.2. Equation (3.1) computes the number of CMOS dies that can be cut out from a wafer. Equation (3.2) computes the number of interposer dies per wafer. Equation (3.3) calculates the yield of CMOS chiplet. Equation (3.4) and Equation (3.5) compute the cost of a CMOS die and an interposer die, respectively. Equation (3.6) adds up all the components to get the overall cost of a 2.5D system.

<sup>&</sup>lt;sup>1</sup>We do not explicitly model the testing cost. We assume the testing costs of a single-chip system and a 2.5D system are similar because a 2.5D system costs less in per-chiplet testings but has an additional cost associated with testing the 2.5D system as a whole.

$$N_{CMOS} = \frac{\pi \times (\phi_{wafer}/2)^2}{A_{CMOS}} - \frac{\pi \times \phi_{wafer}}{\sqrt{2 \times A_{CMOS}}}$$

(3.1)

$$N_{int} = \frac{\pi \times (\phi_{wafer_{int}}/2)^2}{A_{int}} - \frac{\pi \times \phi_{wafer_{int}}}{\sqrt{2 \times A_{int}}}$$

(3.2)

$$Y_{CMOS} = (1 + A_{CMOS} D_0 / \alpha)^{-\alpha}$$

(3.3)

$$C_{CMOS} = C_{wafer} / N_{CMOS} / Y_{CMOS}$$

(3.4)

$$C_{int} = C_{wafer_{int}} / N_{int} / Y_{int}$$

(3.5)

$$C_{2.5D} = \frac{C_{int} + \sum_{i=1}^{n} (C_{CMOS} + C_{bond})}{Y_{bond}^{n-1}}$$

(3.6)

| Table 3.2: | Notation | used in | Equations | (3.1) | through | (3.12) |

|------------|----------|---------|-----------|-------|---------|--------|

|------------|----------|---------|-----------|-------|---------|--------|

| Notation                                                          | Definition                                                                                                                                              | Assumed Value                                                                              |  |  |  |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|

| $\phi_{wafer}, \phi_{wafer_{int}}$                                | Diameter of CMOS and interposer wafer                                                                                                                   | $300 \ mm$                                                                                 |  |  |  |

| $N_{CMOS}, N_{int}$                                               | CMOS and interposer dies per wafer                                                                                                                      | Eq. $(3.1)$                                                                                |  |  |  |

| $D_0$                                                             | Defect density                                                                                                                                          | $0.25/mm^2$ (Stow et al., 2016)                                                            |  |  |  |

| α                                                                 | Defect clustering parameter                                                                                                                             | 3 (Stow et al., 2016 $)$                                                                   |  |  |  |

| Y <sub>int</sub>                                                  | Yield of an interposer                                                                                                                                  | 98% (Tran et al., 2016)                                                                    |  |  |  |

| $Y_{CMOS}$                                                        | Yield of a CMOS chiplet                                                                                                                                 | from Eq. $(3.3)$                                                                           |  |  |  |

| $C_{wafer}$                                                       | CMOS wafer cost                                                                                                                                         | \$5000 (Pares, 2013)                                                                       |  |  |  |

| $C_{wafer_{int}}$                                                 | Interposer wafer cost                                                                                                                                   | \$500 (Pares, 2013)                                                                        |  |  |  |

| $C_{int}, C_{CMOS}, C_{2D}$                                       | Chiplet, interposer, and 2D chip cost                                                                                                                   | from Eq. $(3.4)$                                                                           |  |  |  |

| $Y_{bond}$                                                        | Chiplet bonding yield                                                                                                                                   | 99% (Stow et al., 2016)                                                                    |  |  |  |

| $C_{2.5D}$                                                        | Cost of the 2.5D system                                                                                                                                 | from Eq. $(3.6)$                                                                           |  |  |  |

| $l_g$                                                             | Guard band along each interposer edge                                                                                                                   | 1 mm                                                                                       |  |  |  |

| $w_{2D}, h_{2D}$                                                  | Width and height of the baseline 2D chip                                                                                                                | 18 mm                                                                                      |  |  |  |

| $w_{int}, h_{int}$                                                | Width and height of the interposer $(in mm)$                                                                                                            | from Eq. $(3.11)$                                                                          |  |  |  |

| $w_c, h_c$                                                        | Width and height of the chiplets                                                                                                                        | from Eq. $(3.10)$                                                                          |  |  |  |

| Notation                                                          | Definition                                                                                                                                              |                                                                                            |  |  |  |

| $A_{CMOS}, A_{int}$                                               | CMOS, interposer di                                                                                                                                     | e area                                                                                     |  |  |  |

| $C_{bond}$                                                        | Bonding cost of a chiplet (Farrens                                                                                                                      | and MicroTec, 2010)                                                                        |  |  |  |

| r                                                                 | Number of chiplets in a row                                                                                                                             | w or column                                                                                |  |  |  |

| $\overline{n}$                                                    | Number of chiplets $n = r \times$                                                                                                                       | $r, n \in \{4, 16\}$                                                                       |  |  |  |

| F                                                                 | Frequency set {1000, 800, 533,                                                                                                                          | $400, 320 MHz\}$                                                                           |  |  |  |

| V                                                                 | Corresponding voltage set $\{0.9, 0.87, 0.71, 0.63, 0.63 V\}$                                                                                           |                                                                                            |  |  |  |

| v                                                                 |                                                                                                                                                         | ,,,,                                                                                       |  |  |  |

| $\frac{v}{f}$                                                     | Operating frequency                                                                                                                                     | $f \in F$                                                                                  |  |  |  |

|                                                                   |                                                                                                                                                         | $f \in F$                                                                                  |  |  |  |

| $\frac{f}{f}$                                                     | Operating frequencyActive core count $p \in \{32, 64, 96, 12$ Instructions per second (IPS) of 2.5D                                                     | $f \in F$<br>8, 160, 192, 224, 256}<br>system and 2D system                                |  |  |  |

| $\frac{f}{p} \\ \frac{IPS_{2.5D}, IPS_{2D}}{s_{1}, s_{2}, s_{3}}$ | Operating frequency<br>Active core count $p \in \{32, 64, 96, 12$<br>Instructions per second (IPS) of 2.5D<br>Chiplet spacings (Figure 3.5(a)). $s_1 =$ | $f \in F$ 8, 160, 192, 224, 256} system and 2D system $s_2 = 0 \text{ for 4-chiplet case}$ |  |  |  |

|                                                                   | Operating frequencyActive core count $p \in \{32, 64, 96, 12$ Instructions per second (IPS) of 2.5D                                                     | $f \in F$ 8, 160, 192, 224, 256} system and 2D system $s_2 = 0 \text{ for 4-chiplet case}$ |  |  |  |

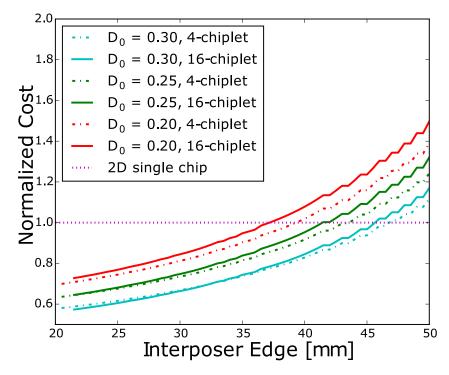

Figure 3-1 shows the manufacturing cost of the 2.5D systems with various (squareshaped) interposer sizes normalized to an equivalent 18  $mm \times 18 mm$  single-chip system for a range of defect densities (Stow et al., 2016). As the interposer size increases, the cost is higher since there are fewer interposers that can be cut out from a wafer. The 2.5D system with a minimal interposer size has a cost saving ranging from 30% to 42%, compared to the cost of the single-chip system at the same defect density. With higher defect density, the 2D system costs more due to lower yield. Thus, there are higher cost saving from splitting chiplets for a larger defect density. With a larger chiplet count, the CMOS chiplet yield is higher but the bonding yield is lower. The 16-chiplet case costs more at a larger interposer size due to lower bonding yield. While at a smaller interposer size, the costs of both chiplet counts are close, because the lower bonding yield of the 16-chiplet case is compensated by the higher CMOS yield of smaller chiplets.

Figure 3.1: Impact of defect densities on 2.5D system cost normalized to the single-chip system costs at the same defect densities.

## 3.3 Thermal Behavior of 2.5D Systems

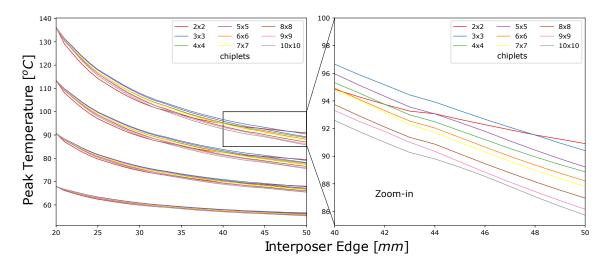

To understand the thermal behavior of a 2.5D system, we first analyze the impact of chiplet count on the operating temperature of the 2.5D system. In this study, we divide a single chip of 18  $mm \times 18 mm$  into  $r \times r$  identical chiplets ( $r \times r = n$ , and r varies from 2 to 10) and place them onto an interposer in a matrix fashion with **uniform** spacing between adjacent chiplets. For each value of r, we vary the interposer edge length from 20 mm to 50 mm in steps of 1 mm and calculate the corresponding spacing between chiplets. For example, if an interposer has an edge length of L mm, the spacing between the adjacent chiplets is  $(L - 18 - 2 \times l_g)/(r -$ 1) mm (where  $l_g = 1 mm$  is the guard-band spacing along each interposer edge), and an individual chiplet edge is 18/r mm. For a given interposer size, as the chiplet count increases, the spacing between the chiplets decreases. We assign synthetic power densities from 0.5  $W/mm^2$  to 2.0  $W/mm^2$  to the chiplets and perform thermal simulations via HotSpot (Zhang et al., 2015) to get a better understanding of the thermal trends in 2.5D systems.

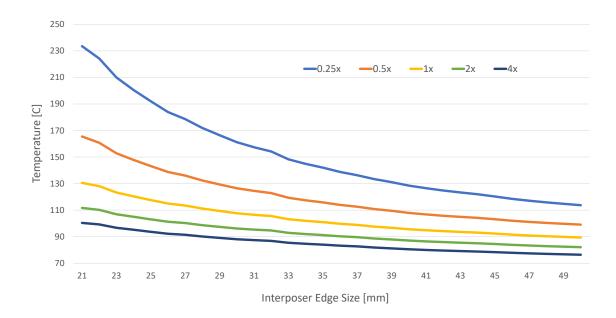

Figure 3.2 shows the impact of chiplet counts, interposer sizes, and power densities on peak temperature of 2.5D systems. In general, as expected, for the same chiplet count and interposer size, the peak temperature increases with power density. For the same chiplet count and power density, as the interposer size increases, the peak temperature decreases due to the increased spacing among chiplets. For the same interposer size and power density, the peak temperature decreases with increasing chiplet count. However, there are some exceptions that the  $2 \times 2$  case has lower peak temperature than others for small interposer sizes, and the  $4 \times 4$  case has lower peak temperature than the  $5 \times 5$  case. This is because 'even' chiplet counts avoid placing a chiplet at the interposer center where it is harder to dissipate heat than at the interposer edge. As the chiplet count increases, the individual chiplet size decreases,

Figure 3.2: Impact of chiplet counts, interposer sizes, and power densities on peak temperature of 2.5D systems with **uniform** spacing between chiplets.

resulting in less power dissipated by the center chiplet. Hence, we do not observe such exceptions for chiplet counts greater than  $5 \times 5$ .

Although a single chip with the same power profile and the same area as our 2.5D system would achieve a similar thermal profile, the single-chip solution is not the best choice from a cost perspective. For example, based on Equations (3.1)-(3.6) and parameters in Table 3.2, increasing the single chip size from 20  $mm \times 20 mm$  to 40  $mm \times 40 mm$  results in 27× higher cost because of drastically lower yield. Alternatively, an equivalent 2.5D system with four smaller chiplets and a 40  $mm \times 40 mm$  passive silicon interposer has 27% lower cost (where the interposer cost is 30% of the 2.5D system) than a 20  $mm \times 20 mm$  single chip.