# BOSTON UNIVERSITY COLLEGE OF ENGINEERING

#### Dissertation

# NEURAL NETWORK COMPUTING USING ON-CHIP ACCELERATORS

by

### SCHUYLER ELDRIDGE

B.S., Boston University, 2010

Submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

2016

### Approved by

First Reader

Ajay J. Joshi, PhD

Associate Professor of Electrical and Computer Engineering

Second Reader

Allyn E. Hubbard, PhD

Professor of Biomedical Engineering

Professor of Electrical and Computer Engineering

Third Reader

Martin C. Herbordt, PhD

Professor of Electrical and Computer Engineering

Fourth Reader

Jonathan Appavoo, PhD

Associate Professor of Computer Science

...he looked carefully at the barman.

"A dry martini," he said. "One. In a deep champagne goblet."

"Oui, monsieur."

"Just a moment. Three measures of Gordon's, one of vodka, half a measure of Kina Lillet. Shake it very well until it's ice-cold, then add a large thin slice of lemon peel. Got it?"

"Certainly, monsieur." The barman seemed pleased with the idea.

"Gosh, that's certainly a drink," said Leiter.

Bond laughed. "When I'm ... er ... concentrating," he explained, "I never have more than one drink before dinner. But I do like that one to be large and very strong and very cold and very well-made. I hate small portions of anything, particularly when they taste bad. This drink's my own invention. I'm going to patent it when I can think of a good name."

[Fleming, 1953]

#### Acknowledgments

All of this work was enabled by my gracious funding sources over the past six years. In my first year, Prof. Ayse Coskun helped me secure a Dean's Fellowship through Boston University. My second year was funded through Boston University's former Center of Excellence for Learning in Education, Science, and Technology (CELEST) working with Dr. Florian Raudies and Dr. Max Versace. Florian and Max were instrumental in providing my first introduction to biological modeling and neural networks.

I am incredibly thankful for funding through the subsequent four years from the National Aeronautics and Space Administration (NASA) via a Space Technology Research Fellowship (NSTRF). This provided me with the unbelievable opportunity to work at NASA Jet Propulsion Lab (JPL) for three summers with Dr. Adrian Stoica. Adrian's discussions were invaluable and I'm incredibly thankful for him acting as host, mentor, instigator, and friend.

Digressing, I must mention a number of people who guided me along the way up to this point and on whose wisdom I drew during this process. Luis Lovett, my figure skating coach in Virginia, taught me that there's beauty just in the effort of trying. Allen Schramm, my choreographer, similarly showed me the brilliance of abandoning perfection for artistic immersion within and without. Tommy Litz, my technical coach, impressed on me that eventually you'll hit a point and you just have to be a man. And finally, Slavka Kohout, my competitive coach, taught me the unforgettable lesson that the crowd really does just want to see blood.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>c.f. [Hemingway, 1926]:

Romero's bull-fighting gave real emotion, because he kept the absolute purity of line in his movements and always quietly and calmly let the horns pass him close each time. He did not have to emphasize their closeness. Brett saw how something that was beautiful done close to the bull was ridiculous if it were done a little way off. I told her how since the death of Joselito all the bull-fighters had been developing a technique that simulated this appearance of danger in order to give a fake emotional

Naturally, I'm thankful for the help and guidance of my advisor, Prof. Ajay Joshi, who helped me through (and stuck with me) during the meandering, confusing, and dead-end-riddled path that I took. I am also forever indebted to Prof. Jonathan Appavoo, acting as an unofficial advisor, collaborator, and friend over the past three years. My one regret throughout this whole process was not getting to know him sooner.

It goes without saying that none of this would have been possible without the friendship of my parents, John and Diana Eldridge. They have consistently been my wellspring of support throughout my life. This is further remarkable considering our atypical family and all of the extraneous and incredibly challenging circumstances we've collectively experienced. Furthermore, my lifelong friends Alex Scott and Peter Achenbaum have always been there and, critically, always ready for a cocktail.

Finally, as I've attempted to impress on new PhD students, a PhD is a psychological gauntlet testing your mental limits. It's hard, it's terrible, and it will push you in every way imaginable, but it's one of the only times in your lives when you can lose yourself in maniacal focus. It's a lot like wandering into a forest.<sup>2</sup> It's pretty for a while, but you will eventually, without fail, become (seemingly) irrevocably lost. Be worried, but not overly so—there's a catharsis coming. You will hit a point and you'll take ownership,<sup>3</sup> and after that your perspective in all things changes. So, it does get better, I promise, and there's beauty in all of it.

feeling, while the bull-fighter was really safe. Romero had the old thing, the holding of his purity of line through the maximum of exposure, while he dominated the bull by making him realize he was unattainable, while he prepared him for the killing.

<sup>&</sup>lt;sup>2</sup>c.f. [The Cure, 1980]

<sup>&</sup>lt;sup>3</sup>c.f. [The Cure, 1985]

NEURAL NETWORK COMPUTING USING ON-CHIP

ACCELERATORS

SCHUYLER ELDRIDGE

Boston University, College of Engineering, 2016

Major Professor: Ajay J. Joshi, PhD

Associate Professor of Electrical and Computer

Engineering

ABSTRACT

The use of neural networks, machine learning, or artificial intelligence, in its broadest

and most controversial sense, has been a tumultuous journey involving three distinct

hype cycles and a history dating back to the 1960s. Resurgent, enthusiastic interest

in machine learning and its applications bolsters the case for machine learning as a

fundamental computational kernel. Furthermore, researchers have demonstrated that

machine learning can be utilized as an auxiliary component of applications to enhance

or enable new types of computation such as approximate computing or automatic par-

allelization. In our view, machine learning becomes not the underlying application,

but a ubiquitous component of applications. This view necessitates a different ap-

proach towards the deployment of machine learning computation that spans not only

hardware design of accelerator architectures, but also user and supervisor software to

enable the safe, simultaneous use of machine learning accelerator resources.

In this dissertation, we propose a multi-transaction model of neural network com-

putation to meet the needs of future machine learning applications. We demonstrate

that this model, encompassing a decoupled backend accelerator for inference and

vii

learning from hardware and software for managing neural network transactions can be achieved with low overhead and integrated with a modern RISC-V microprocessor. Our extensions span user and supervisor software and data structures and, coupled with our hardware, enable multiple transactions from different address spaces to execute simultaneously, yet safely. Together, our system demonstrates the utility of a multi-transaction model to increase energy efficiency improvements and improve overall accelerator throughput for machine learning applications.

#### **Preface**

Neural Networks, machine learning, and artificial intelligence—some of the most hyped technologies of the past half century—have seen a dramatic, recent resurgence towards solving many hard yet computable problems. However, it is with the utmost caution that the reader must temper their enthusiasm, as I have been forced to over the duration of the following work. Nevertheless, neural networks are a very powerful tool, while not truly biological to a purist, that reflect some of the structure of the brain. These biological machines, evolved over millennia, must indicate a viable computational substrate for processing the world around us. It is my belief, a belief shared by others, that this style of computation provides a way forward—beyond the current difficulties of semiconductor technology—towards more efficient, biologically-inspired systems capable of providing the next great leap for computation. What follows, broadly, concerns the design, analysis, and evaluation of hybrid systems that bring neural networks as close as possible to traditional computer architectures. While I admit that such architectures are only a stopgap, I hope that this will contribute towards that aforementioned way forward.

# Contents

| 1 | Intr               | Introduction                                                   |                                                           |    |  |

|---|--------------------|----------------------------------------------------------------|-----------------------------------------------------------|----|--|

|   | 1.1                | Backg                                                          | round                                                     | 1  |  |

|   |                    | 1.1.1                                                          | An ontology for computation                               | 4  |  |

|   |                    | 1.1.2                                                          | Machine learning accelerators of the future               | 6  |  |

|   | 1.2                | Motiv                                                          | ating Applications                                        | 7  |  |

|   | 1.3                | Outlin                                                         | e of Contributions                                        | 9  |  |

|   |                    | 1.3.1                                                          | Thesis statement                                          | 9  |  |

|   |                    | 1.3.2                                                          | Contributions                                             | 10 |  |

|   | 1.4                | Disser                                                         | tation Outline                                            | 12 |  |

| 2 | Bac                | kgrou                                                          | nd                                                        | 14 |  |

|   | 2.1                | A Brie                                                         | ef History of Neural Networks                             | 14 |  |

|   |                    | 2.1.1                                                          | Neural networks and early computer science                | 14 |  |

|   |                    | 2.1.2                                                          | Criticisms of neural networks and artificial intelligence | 18 |  |

|   |                    | 2.1.3                                                          | Modern resurgence as machine learning                     | 21 |  |

|   | 2.2                | Neura                                                          | l Network Software and Hardware                           | 23 |  |

|   |                    | 2.2.1                                                          | Software                                                  | 24 |  |

|   |                    | 2.2.2                                                          | Hardware                                                  | 25 |  |

|   |                    | 2.2.3                                                          | Context of this dissertation                              | 28 |  |

| 3 | $\mathbf{T}$ - $f$ | T-fnApprox: Hardware Support for Fine-Grained Function Approx- |                                                           |    |  |

|   | ima                | tion u                                                         | sing MLPs                                                 | 31 |  |

|   | 3.1                | Funct                                                          | on Approximation                                          | 32 |  |

|   |                                                        | 3.1.1   | CORDIC and Unified CORDIC                                     | 34        |

|---|--------------------------------------------------------|---------|---------------------------------------------------------------|-----------|

|   | 3.2                                                    | A Fixe  | ed-topology Neural Network Accelerator                        | 36        |

|   |                                                        | 3.2.1   | Approximation capability                                      | 39        |

|   | 3.3                                                    | Evalua  | ation                                                         | 42        |

|   |                                                        | 3.3.1   | Energy efficiency                                             | 42        |

|   |                                                        | 3.3.2   | Comparison against traditional floating point                 | 43        |

|   |                                                        | 3.3.3   | Affect on application benchmarks                              | 47        |

|   | 3.4                                                    | Appro   | eximation and Fixed-topology Neural Network Accelerators      | 48        |

| 4 | X-F                                                    | ILES:   | Software/Hardware for Neural Networks as First Class          |           |

|   | Pri                                                    | mitives | $\mathbf{S}$                                                  | <b>52</b> |

|   | 4.1                                                    | Motiv   | ation: Neural Networks as Function Primitives                 | 52        |

|   | 4.2                                                    | X-FIL   | ES: Software and Hardware for Transaction Management          | 57        |

|   |                                                        | 4.2.1   | X-FILES Hardware Arbiter                                      | 60        |

|   |                                                        | 4.2.2   | Supervisor data structures: the ASID-NNID Table               | 63        |

|   |                                                        | 4.2.3   | Supervisor and user API                                       | 67        |

|   | 4.3                                                    | Opera   | ting System Integration                                       | 69        |

|   |                                                        | 4.3.1   | RISC-V Proxy Kernel                                           | 69        |

|   |                                                        | 4.3.2   | RISCV-V Linux port                                            | 70        |

|   | 4.4                                                    | Summ    | ary                                                           | 72        |

| 5 | 5 DANA: An X-FILES Accelerator for Neural Network Comp |         | n X-FILES Accelerator for Neural Network Computation          | 73        |

|   | 5.1                                                    | Motiv   | ation and Guidelines for a General Neural Network Accelerator | 74        |

|   | 5.2                                                    | DANA    | A: A Dynamically Allocated Neural Network Accelerator         | 77        |

|   |                                                        | 5.2.1   | Transaction Table                                             | 78        |

|   |                                                        | 5.2.2   | Configuration Cache                                           | 79        |

|   |                                                        | 5.2.3   | ASID-NNID Table Walker                                        | 82        |

|   |                                                        | 5 2 4   | Control modulo                                                | 83        |

| $\mathbf{C}_{1}$ | urric        | ulum '  | Vitae                                      | 129 |

|------------------|--------------|---------|--------------------------------------------|-----|

| $\mathbf{R}$     | References 1 |         |                                            | 119 |

|                  | 7.4          | Final   | Remarks                                    | 118 |

|                  |              | 7.3.5   | Linux kernel modifications                 | 118 |

|                  |              | 7.3.4   | New X-FILES backends                       | 117 |

|                  |              | 7.3.3   | Asynchronous in-memory input–output queues | 116 |

|                  |              | 7.3.2   | Variable transaction priority              | 115 |

|                  |              | 7.3.1   | Transaction granularity                    | 114 |

|                  | 7.3          | Future  | e Work                                     | 114 |

|                  | 7.2          | Limita  | ations of X-FILES/DANA                     | 112 |

|                  | 7.1          | Summ    | ary of Contributions                       | 111 |

| 7                | Con          | clusio  | n                                          | 111 |

|                  | 6.4          | Summ    | ary                                        | 110 |

|                  | 6.3          | Rocke   | t + X-FILES/DANA                           | 107 |

|                  |              | 6.2.2   | Single and multi-transaction throughput    | 101 |

|                  |              | 6.2.1   | Power and latency                          | 96  |

|                  | 6.2          | X-FIL   | ES/DANA in SystemVerilog                   | 95  |

|                  | 6.1          | Differe | ent Implementations of X-FILES/DANA        | 92  |

| 6                | Eva          | luatio  | n of X-FILES/DANA                          | 92  |

|                  | 5.4          | Summ    | ary                                        | 91  |

|                  |              | 5.3.2   | Learning                                   | 89  |

|                  |              | 5.3.1   | Feedforward computation                    | 88  |

|                  | 5.3          | Opera   | tion for Neural Network Transactions       | 88  |

|                  |              | 5.2.6   | Scratchpad memories                        | 86  |

|                  |              | 5.2.5   | Processing Elements                        | 84  |

# List of Tables

| 2.1 | Related work on neural network software and hardware                       | 23  |

|-----|----------------------------------------------------------------------------|-----|

| 3.1 | Identities from Unified CORDIC                                             | 35  |

| 3.2 | Scaling steps for Unified CORDIC                                           | 36  |

| 3.3 | Error for neural networks approximating transcendental functions           | 40  |

| 3.4 | Accelerator configurations with minimum energy delay error product         | 43  |

| 3.5 | Error and energy of T- $fn$ Approx approximating transcendental functions  | 43  |

| 3.6 | Area, frequency, and energy of floating point transcendental functions     | 45  |

| 3.7 | Energy delay product of T- $fn$ Approx applied to transcendental functions | 46  |

| 3.8 | Percentage of execution time for transcendental functions in PARSEC        | 48  |

| 3.9 | Error of PARSEC applications with T- $fn$ Approx                           | 49  |

| 4.1 | X-FILES Hardware Arbiter Transaction Table bit fields                      | 61  |

| 4.2 | Exceptions generated by X-FILES/DANA                                       | 66  |

| 4.3 | X-FILES supervisor and user API                                            | 67  |

| 5.1 | A taxonomy of neural network accelerators                                  | 74  |

| 6.1 | Neural network configurations evaluated for feedforward transactions       | 99  |

| 6.2 | Feedforward energy and performance gains of DANA vs. software              | 106 |

| 6.3 | Neural network configurations evaluated for learning transactions          | 108 |

# List of Figures

| 1.1         | Venn diagram of general and special-purpose computation               | 4  |

|-------------|-----------------------------------------------------------------------|----|

| 2.1         | A single artificial neuron with five inputs                           | 16 |

| $2 \cdot 2$ | A two layer neural network with four inputs and three outputs         | 17 |

| 2.3         | Related software and hardware work                                    | 28 |

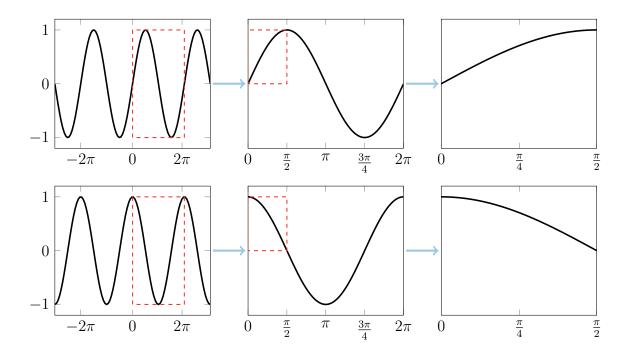

| 3.1         | Decomposition of sine and cosine functions                            | 35 |

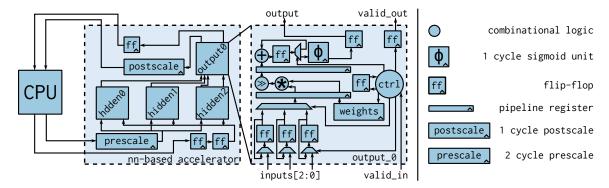

| 3.2         | Overview of the T- $fn$ Approx hardware architecture                  | 38 |

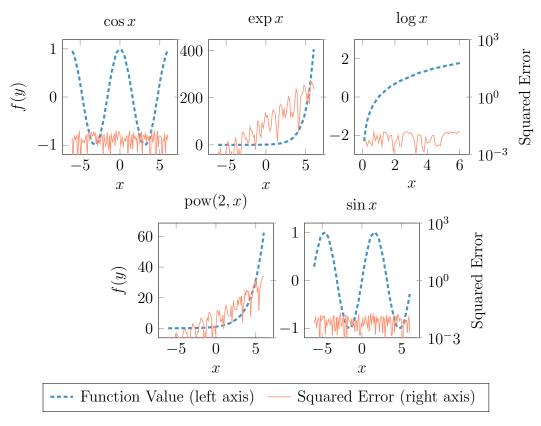

| 3.3         | Approximated transcendental functions using a neural network          | 41 |

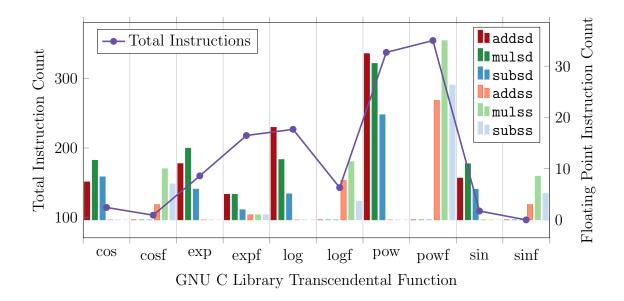

| 3.4         | Instruction counts for transcendental functions in the GNU C Library  | 44 |

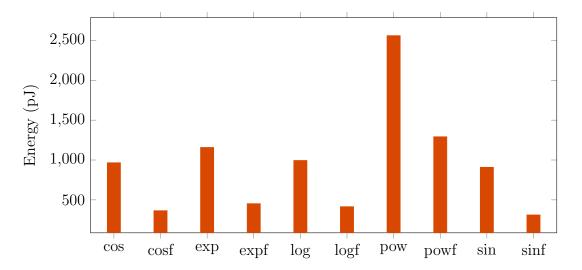

| 3.5         | GNU C Library transcendental function energy consumption              | 45 |

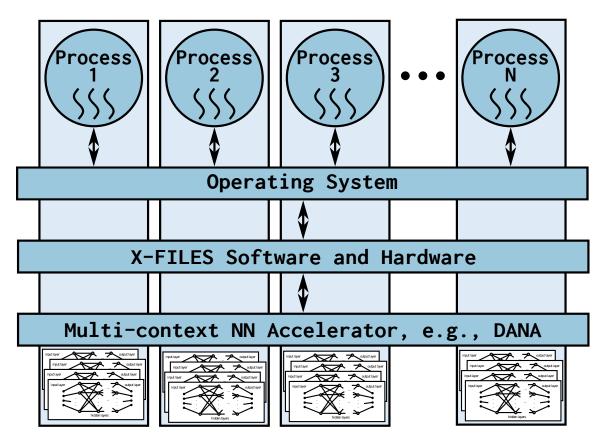

| 4.1         | Hardware/software view of neural network acceleration                 | 54 |

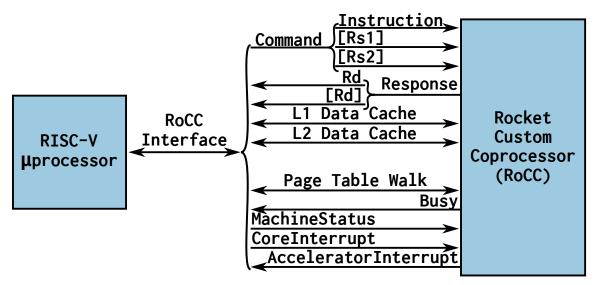

| 4.2         | The RoCC accelerator interface for RISC-V microprocessors             | 58 |

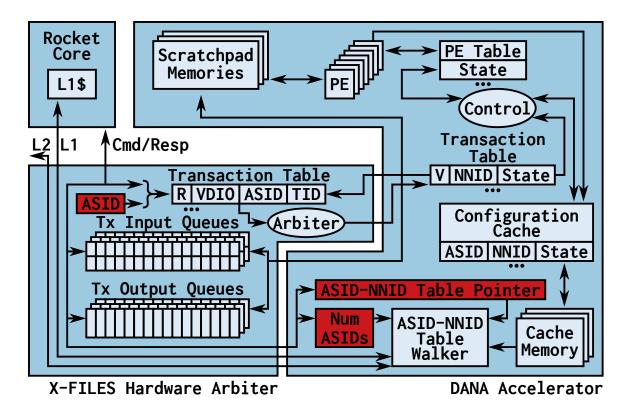

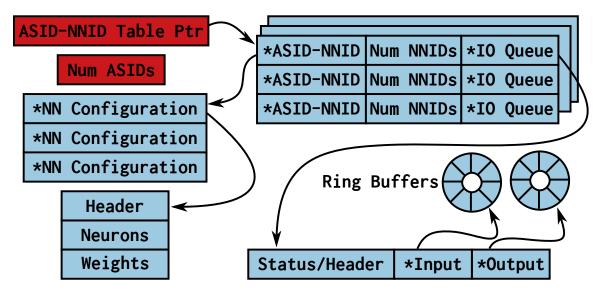

| 4.3         | The X-FILES/DANA hardware architecture                                | 60 |

| 4.4         | An ASID-NNID Table                                                    | 65 |

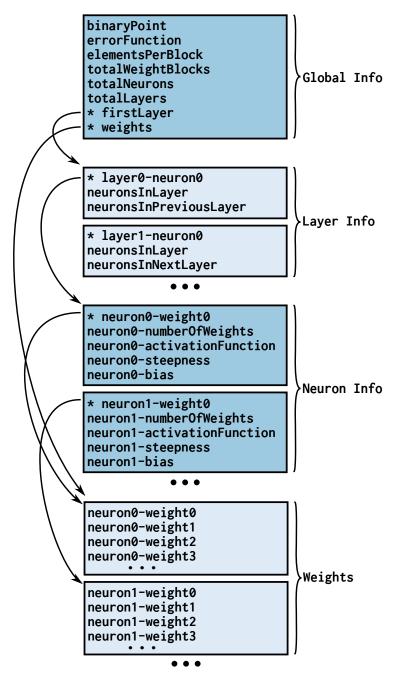

| 5.1         | Neural network configuration data structure                           | 81 |

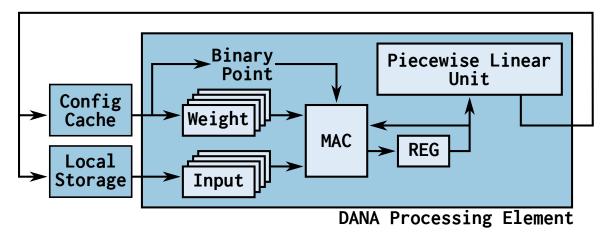

| 5.2         | Processing Element architecture                                       | 84 |

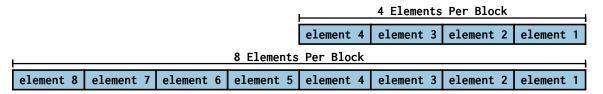

| 5.3         | Block of elements DANA data format                                    | 85 |

| 5.4         | Memory utilization in DANA for feedforward and learning transactions  | 86 |

| 6.1         | Register File used for intermediate storage in early versions of DANA | 94 |

| 6.2         | X-FILES/DANA architecture in SystemVerilog                            | 96 |

| 6.3         | Power and performance of DANA in 40nm CMOS                            | 97 |

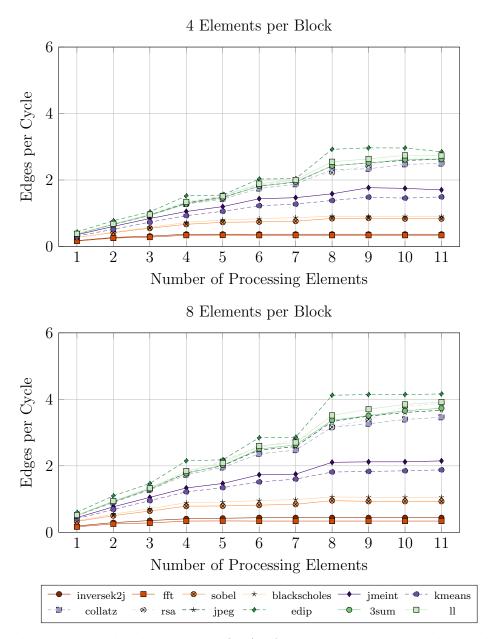

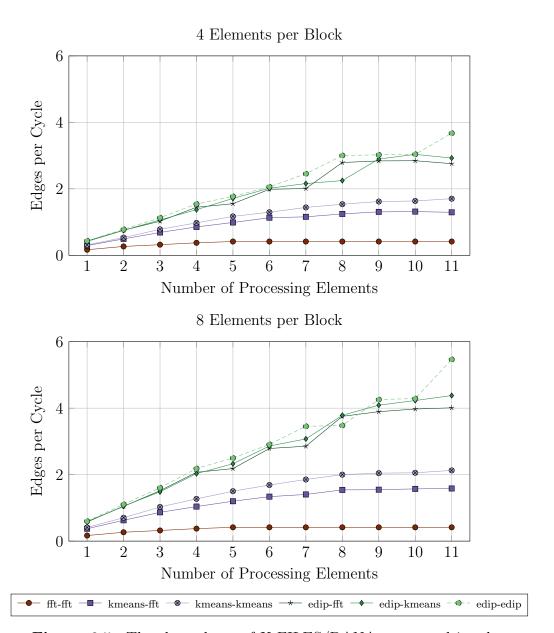

| 6.4 | Single-transaction throughput of X-FILES/DANA               | 102 |

|-----|-------------------------------------------------------------|-----|

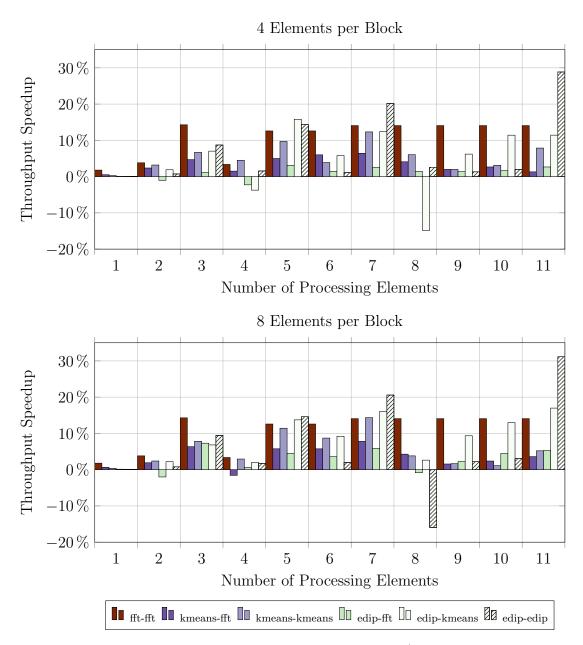

| 6.5 | Dual-transaction throughput of X-FILES/DANA                 | 104 |

| 6.6 | Dual-transaction throughput speedup of X-FILES/DANA $\ \ .$ | 105 |

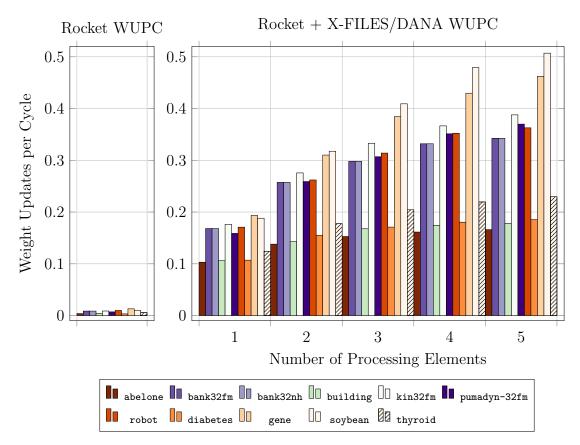

| 6.7 | Learning throughput of X-FILES/DANA hardware vs. software   | 109 |

# List of Abbreviations

| AI     | Artificial Intelligence                              |

|--------|------------------------------------------------------|

| ALU    | Arithmetic Logic Unit                                |

| ANTP   | ASID-NNID Table Pointer                              |

| ANTW   | ASID–NNID Table Walker                               |

| AOT    | Ahead-of-time (Compilation)                          |

| API    | Application Programming Interface                    |

| ASIC   | Application-specific Integrated Circuit              |

| ASID   | Address Space Identifier                             |

| ATLAS  | Automatically Tuned Linear Algebra Software (ATLAS)  |

| ВЈТ    | Bipolar Junction Transistor                          |

| BLAS   | Basic Linear Algebra Subprograms                     |

| BSD    | Berkeley Software Distribution                       |

| CAPI   | Coherent Accelerator Processor Interface             |

| CISC   | Complex Instruction Set Computer                     |

| CGRA   | Coarse-grained Reconfigurable Accelerator            |

| CMOS   | Complimentary Metal-oxide-semiconductor              |

| CNN    | Convolutional Neural Network                         |

| CNS    | Cognitive Neuroscience                               |

| CORDIC | Coordinate Rotation Digital Computer                 |

| CPU    | Central Processing Unit                              |

| CSR    | Control/Status Register                              |

| CUDA   | NVIDIA's Parallel Programming API for GPUs           |

| DANA   | Dynamically Allocated Neural Network Accelerator     |

| DBN    | Deep Belief Network                                  |

| DNN    | Deep Neural Network                                  |

| DSP    | Digital Signal Processor                             |

| EDIP   | Environmental-dependent Interatomic Potential        |

| EDEP   | Energy-delay-error Product                           |

| EDP    | Energy-delay Product                                 |

| EDVAC  | Electronic Discrete Variable Automatic Computer      |

| ENIAC  | Electronic Numerical Integrator and Computer         |

| FANN   | Fast Artificial Neural Network library               |

| FPGA   | Field Programmable Gate Array                        |

| FPU    | Floating Point Unit                                  |

| GNU    | GNU's Not Unix! (an open source software collection) |

| GPU    | Graphics Processing Unit                                 |

|--------|----------------------------------------------------------|

| HDL    | Hardware Description Language                            |

| HMAX   | Hierarchical Model and X                                 |

| IBM    | International Business Machines                          |

| ICSG   | Boston University Integrated Circuits and Systems Group  |

| IEEE   | The Institute of of Electrical and Electronics Engineers |

| ISA    | Instruction Set Architecture                             |

| IoT    | Internet of Things                                       |

| JIT    | Just-in-time (Compilation)                               |

| JPL    | (NASA) Jet Propulsion Lab                                |

| JPEG   | Joint Photographic Experts Group (an image standard)     |

| LSTM   | Long Short Term Memory                                   |

| LWC    | Light-weight Check                                       |

| MAC    | Multiply Accumulate                                      |

| MLP    | Multilayer Perceptron Neural Network                     |

| MOSFET | Metal-oxide-semiconductor Field-effect-transistor        |

| MSE    | Mean Squared Error                                       |

| NASA   | The National Aeronautics and Space Administration        |

| NN     | Neural Network                                           |

| NNID   | Neural Network Identifier                                |

| NPU    | Neural Processing Unit                                   |

| NSTRF  | NASA Space Technology Research Fellowship                |

| OS     | Operating System                                         |

| PC     | Personal Computer                                        |

| PCIe   | Peripheral Component Interconnect Express                |

| PDK    | Process Design Kit                                       |

| PE     | Processing Element                                       |

| PK     | (RISC-V) Proxy Kernel                                    |

| RAP    | Ring Array Processor                                     |

| RAW    | Read After Write (hazard)                                |

| RISC   | Reduced Instruction Set Computer                         |

| RISC-V | Fifth Generation of RISC Instruction Sets                |

| RNN    | Recurrent Neural Network                                 |

| RTL    | Register-transfer Level                                  |

| RoCC   | Rocket Custom Coprocessor                                |

| SCC    | (Intel) Single Chip Cloud                                |

| SMT    | Simultaneous Multithreading                              |

| SPARC  | Scalable Processor Architecture                          |

| TID    | Transaction Identifier                                   |

| UART   | Universal Asynchronous Receiver/Transmitter              |

| VCD    | Value Change Dump                                        |

| VLIW   | Very Long Instruction Word                               |

|        |                                                          |

| VLSI         | Very Large Scale Integration                          |

|--------------|-------------------------------------------------------|

| WUPC         | Weight Updates per Cycle                              |

| X-FILES      | Extensions for the Integration of Machine Learning in |

|              | Everyday Systems                                      |

| X-FILES/DANA | X-FILES hardware with a DANA backend                  |

## Chapter 1

## Introduction

#### 1.1 Background

All computer architectures in the 20<sup>th</sup> and 21<sup>st</sup> centuries have struggled with the unfortunate, yet necessary, trade-off between generality and speciality of their computer hardware designs. On the former extreme, and to serve the widest possible audience, such hardware implements an instruction set architecture (ISA), e.g., RISC-V [Waterman et al., 2014. The ISA describes, at minimum, the fundamental units of computation, i.e., instructions (e.g., ADD R1, R2, R3) which must be combined and sequenced through programming to conduct useful, higher-order computation. On the latter extreme, the highest performance and lowest power computer hardware is, by definition, finely tuned to a specific application. These two extremes concisely describe both a microprocessor (e.g., a CPU) built for general-purpose computing and an Application Specific Integrated Circuit (ASIC) designed to solve one specific problem. Consequently, a myriad of dedicated, application-specific hardware designs have been created dating back to the dawn of computer hardware in the 1950s. Over time the best and most utilitarian designs have eventually made their way into commercial microprocessor implementations. The most prominent example of special-purpose hardware eventually becoming part of a microprocessor is that of floating point coprocessors/accelerators.

<sup>&</sup>lt;sup>1</sup>Note that a microprocessor is an ASIC implementing an ISA, however, we refer to an ASIC in a more general sense as a dedicated piece of hardware built for a specific application, e.g., an image processing algorithm.

Floating point arithmetic provides a compact way to represent both very large and very small numbers with a fixed relative error, but at increased computational cost. In contrast, integer or fixed point representations utilize a fixed number of fractional bits resulting in a varying relative error, but with simpler computational hardware. Consequently, floating point arithmetic has long been a component of applications in the scientific domain that encompass large scales and necessitate fixed relative errors. Support for floating point arithmetic can be provided through either software running on a general-purpose microprocessor or on a dedicated floating point accelerator.

The history of floating point hardware and its eventual migration into microprocessors provides a rough trajectory that other dedicated hardware can be expected to follow. A critical milestone in this history occurred in 1954 with IBM's introduction of the 704. The IBM 704 was the first commercially available computer with floating point support backed by dedicated hardware. The 704 became IBM's first entry in its line of "scientific architectures." The intent of the 704 was that these machines would be marketed for use in scientific applications of importance to government or industrial entities, e.g., NASA or the Department of Energy.<sup>2</sup>

In the span of 24 years, floating point hardware became mainstream enough that Intel, in 1976, began work on a floating point coprocessor that, working alongside an Intel CPU, would provide hardware floating point support. Intending to get this right the first time, Intel (amongst others) bootstrapped the IEEE-754 floating point standardization effort which notably included William Kahan. Four years later, in 1980, Intel released the 8087, a floating point coprocessor for its 8086 microprocessor, that implemented a draft specification of IEEE-754. The 8087 could then be plugged into a standard IBM PC providing hardware support for floating point arithmetic to

<sup>&</sup>lt;sup>2</sup>Tangentially, this notion of floating point hardware making a computer a "scientific architecture" provides an interesting juxtaposition with modern computers (e.g., servers, desktops, laptops) or devices utilizing computational resources (e.g., cellphones, televisions) which all provide dedicated floating point hardware but are not, arguably, "scientific" in nature.

the user. Nine years later, in 1989, Intel released the 80486 which was a dedicated microprocessor that included an *on-die* floating point unit. Going forward from the release of the 80486, nearly all microprocessors (barring restricted embedded architectures or microcontrollers) have hardware support for floating point, and specifically, a version of IEEE-754.

This general to special-purpose hardware transition of floating point arithmetic over the course of 35 years provides useful insights and a possibly similar trajectory for one of the key application domains of computing in the early 21<sup>st</sup> century: machine learning. While machine learning (or neural networks, artificial intelligence, expert machines, etc. ad nauseam) has had a tumultuous past (discussed in detail in Section 2.1), its present successes are astounding and future promises appear attainable and realistic.<sup>3</sup>

Additionally, machine learning has emerged as an alternative computing paradigm to traditional algorithmic design. Machine learning allows an end user who has many examples of a specific relationship (e.g., labeled images) to iteratively modify a machine learning substrate (e.g., a neural network) to represent the provided example dataset and generalize to new data. This model provides extreme power for problem domains with unclear or unknown solutions, but ample example data.

The recent successes of machine learning, largely driven by the achievements of Yann LeCun [Lecun et al., 1998], Yoshua Bengio [Bengio, 2009], and Geoff Hinton [Hinton et al., 2006], have precipitated effervescent interest in machine learning hardware accelerators in addition to CPU and GPU-optimized versions of neural networks. However, the proliferation of machine learning accelerators, while clearly beneficial, necessitates some periodic evaluation and big picture analysis.

<sup>&</sup>lt;sup>3</sup>While this is obviously speculation, anecdotal experience indicates that there exists a general feeling within the machine learning community, heavily tempered by past failures, that, "This time it's different."

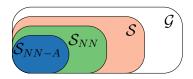

Figure 1·1: For a given computation, this can be decomposed into regions for general purpose and special purpose computation and also, special purpose regions offloaded to neural network accelerators.

#### 1.1.1 An ontology for computation

One of these analyses concerns an overarching ontology of computation that encompasses general and special-purpose hardware and, additionally, makes room for different categories of neural network accelerators. Figure 1·1 shows this ontology by breaking down regions of a computation into those which can be executed on different hardware. Broadly, all computation we generally care about<sup>4</sup> can execute on general-purpose, Turing complete hardware,  $\mathcal{G}$ . Such general purpose hardware typically takes the form of a microprocessor executing a specific ISA. The benefit of this approach is that the expensive costs of hardware design (i.e., of the general-purpose microprocessor) are paid once. New applications can be created using the underlying primitives that the hardware supports, i.e., the instructions a microprocessor can execute.

Alternatively, special-purpose hardware,  $\mathcal{S}$  designed for a specific application will have improved energy efficiency at the cost of increased design time effort that must be paid for each unit of special-purpose hardware. Additionally, the utility of such hardware generally decreases for new applications.<sup>5</sup> In consequence, only a subset of the general-purpose computation region would be amenable to be offloaded to a given unit of special-purpose hardware. Figure 1·1 reflects this due to the reduced size of the region  $\mathcal{S}$  relative to  $\mathcal{G}$ .

$<sup>^4</sup>$ We naturally mean computation within  $\mathcal{P}$ , i.e., problems computable with a deterministic Turing machine. Alternatively, this is just a restatement of Cobham's thesis [Cobham, 1965].

<sup>&</sup>lt;sup>5</sup>Though, techniques do exist to create, e.g., patchable accelerators [Venkatesh et al., 2010].

Obviously, being able to reuse special-purpose hardware for multiple, disparate applications amortizes the design time cost of the special-purpose hardware while still retaining energy efficiency improvements. One avenue towards achieving this goal involves thinking of "special-purpose substrates," i.e., a substrate that can adapt and specialize to meet the requirements of different workloads. Both Field Programmable Gate Arrays (FPGAs) and Coarse-grained Reconfigurable Architectures (CGRAs) are natural candidates. However, and as a dramatic alternative, neural networks have some critical properties that makes them strong candidates for special-purpose substrates.

Feedforward neural networks are universally approximate [Cybenko, 1989, Hornik, 1991] and recurrent neural networks (RNNs) are Turing complete [Siegelmann and Sontag, 1995]. Consequently, these properties may allow neural networks to be trained to suit multiple different problems while avoiding the repeated design time costs of special purpose hardware on a per-application basis. Additionally, resurgent interest motivates the inclusion of special purpose neural network accelerator hardware. We define a subset of S in Figure 1·1 for computation that is amenable to acceleration via neural networks,  $S_{NN}$ . A further subdivision concerns portions of computation amenable to acceleration via neural networks that are also amenable to approximation,  $S_{NN-A}$ .

Mathematically, the relationships described above and in Figure 1·1 are defined by the following equations:

General Purpose

$$\equiv \mathcal{G}$$

(1.1)

Special Purpose

$$\equiv S$$

$\subseteq \mathcal{G}$  (1.2)

Special Purpose via Neural Networks

$$\equiv S_{NN} \qquad \subseteq S$$

(1.3)

Approximable via Neural Networks

$$\equiv S_{NN-A}$$

$\subseteq S_{NN}$  (1.4)

Due to resurgent interest in machine learning and the potential capacity for neural network accelerators to act as special-purpose substrates (and, in effect, push upwards from  $S_{NN}$  into S), we focus on the development of accelerators that fit within the areas of  $S_{NN-A}$  and  $S_{NN}$ .

#### 1.1.2 Machine learning accelerators of the future

The second analysis concerns the design of neural network accelerators to meet the requirements of future applications which will assumedly treat machine learning as an application primitive. The aforementioned floating point analogy provides guidance, but not the full picture due to the differences between floating point and machine learning accelerators. We use the following questions to further drive the narrative:

- What are the characteristics of applications that treat machine learning as a functional primitive?

- How should machine learning accelerators be integrated with computing systems?

- How and who will manage these accelerators as an increasing number of applications require access to machine learning hardware acceleration?

Nevertheless, the answers to these questions are difficult to address without some concrete usages cases. We momentarily defer answers to these questions to first discuss general-purpose and special-purpose hardware in light of recent, novel uses of machine learning.

#### 1.2 Motivating Applications

Two recent applications of machine learning, approximate computing via function approximation [Esmaeilzadeh et al., 2012b, Amant et al., 2014, Moreau et al., 2015] and automatic parallelization [Waterland et al., 2012, Waterland et al., 2014], employ neural networks in untraditional ways. Specifically, they utilize machine learning to augment and improve the energy efficiency of existing applications.

Neural networks can be used to approximate functions and, to maximize energy efficiency gains, approximated functions should be hot, i.e., frequently used. Put broadly, a user or compiler profiles or injects code to build up an approximate model of some region of code. That region of code can then be replaced with an approximate version. Dynamic programming/memoization is a classical, non-approximate technique that uses a similar approach. While existing work in this area approximates compiler-identified hot regions in handpicked benchmarks, the obvious place to look for hot functions is in shared code. Such shared code, assumedly packaged into shared libraries, introduces an interesting opportunity for neural network accelerator hardware. Specifically, since neural networks are then approximating shared functions, the constituent neural networks backing this approximation must also be shared. This introduces the first requirement of future neural network accelerators, namely the capacity for sharing descriptions of neural networks across requests.

In automatic parallelization work, neural networks predict future microprocessor state.<sup>6</sup> Spare system resources then speculate based on these predictions. As a

<sup>&</sup>lt;sup>6</sup> For readers with a hardware design background, this work can appear relatively opaque. A helpful analogy is to view this work as a generalization of branch prediction (where a single bit of state is predicted) to multiple bits. The predicted bits, however, can exist anywhere in the full state of the microprocessor (architectural state, registers, memory). This work hinges on choosing

hedging mechanism and to improve performance, multiple predictions from a given state are made. In consequence, many requests to access neural network resources are generated at the same time. Similarly, as aforementioned approximate computing work (or, more generally, machine learning) becomes more prominent, many different processes may begin using the neural network accelerator resources of a system. This introduces the second requirement of future neural network accelerators, namely the capability to manage multiple simultaneous requests within short time frames. A further, tangential benefit is the capability to exploit multiple requests to neural network accelerator resources, e.g., to improve accelerator throughput.

These two applications demonstrate future directions for the use of machine learning and neural networks in applications. Specifically, machine learning augments and benefits applications which were originally characterized as having no relation to machine learning. This directly contrasts with the current viewpoint where machine learning is the application. While obviously extrapolatory, this viewpoint mirrors the transition of floating point hardware from the realm of "scientific architectures" to everyday computing systems, e.g., mobile phones. This transition requires a rethinking of neural network accelerator hardware, as well as user and operating system software, that integrates and manages both neural network sharing and requests to access accelerator resources.

Not surprisingly, this dissertation applies a holistic, system-level view to neural network computing that spans the software and hardware stack. Motivated by applications like approximate computing via neural networks and automatic parallelization, we design accelerator hardware and software to support such new applications. Specifically, we incorporate accelerator hardware alongside a traditional micropro-

points in an executing program where small numbers of bits change, e.g., at the top of loops. From a mathematical view, this work views a microprocessor as a dynamical system where points with small Hamming distances along the trajectory are predicted using machine learning. Approximate predictions of state can still be useful.

cessor and include a full discussion of the user and supervisor (operating system) software necessary to support future machine learning accelerators.<sup>7</sup>

#### 1.3 Outline of Contributions

#### 1.3.1 Thesis statement

Broadly, a multi-context, multi-transaction model of neural network computation has the following benefits:

- 1. It aligns with the needs of modern, highly novel, and emerging applications that utilize machine learning as an application primitive, for learning and prediction, on top of which complex applications can be built.

- 2. Such a model can be achieved with low overhead while improving the overall throughput of a backend accelerator matching this multi-transaction model.

- 3. The necessary management infrastructure for a multi-transaction model, both hardware and software, can be sufficiently decoupled from the backend accelerator such that multiple backends can be supported.

- 4. All hardware and software for such a model can be realized and integrated with an existing general-purpose software and hardware environment.

Nevertheless, the benefits of a multi-transaction model are predicated on two assertions. First, there exists sufficiently interesting work that can be achieved with "small" neural networks, on the order of tens to hundreds of neurons, such that a multi-transaction model can realize significant throughput improvements.<sup>8</sup> Second,

<sup>&</sup>lt;sup>7</sup>It is our opinion that such a system-level view is *generally* necessary when thinking about non-trivial accelerators. Specifically, how will the user access an accelerator? How will the operating system manage the accelerator? What data structures need to be maintained across context switches?

<sup>&</sup>lt;sup>8</sup>Small neural networks have the potential for the most dramatic throughput gains in a multi-transaction model due to the large number of data dependencies as a portion of the total number of computations required to execute the network.

a neural network accelerator meeting the requirements outlined above does, in fact, exist and can be realized.

Towards validating these assertions, we present two bodies of work. First, we explore the design and implementation of an accelerator architecture for specific, fixed topology neural networks. This accelerator enables fine-grained approximation of mathematical functions in a shared library using small networks. Second, leveraging lessons learned from this first accelerator, we design a new accelerator capable of processing multiple neural network transactions simultaneously.

In experimental support of the aims of this thesis and towards validating the benefits of our multi-transaction model, we provide and evaluate this second accelerator implementation as well as its hardware and software integration with an open source microprocessor and operating system. We experimentally evaluate this accelerator on energy efficiency grounds and, expectedly, find dramatic gains over software. Furthermore, the accelerator improves its throughput with additional transactions validating our multi-transaction model.

#### 1.3.2 Contributions

Our design and implementation of a fixed topology neural network accelerator, T-fnApprox, applies function approximation at very small functional granularities, specifically transcendental functions. This work does not address the previous issues of sharing and management of multiple transactions, but serves as an example implementation of a neural network accelerator. This work then further motivates, by counterexample, the need for a system-level view of neural network acceleration. Additionally, this work empirically reiterates a rough lower bound on the amount of computation that can be approximated using digital neural network accelerator hardware.

Our proposed arbitrary topology neural network accelerator supporting both neu-

ral network sharing and a multi-transaction model comprises three specific contributions. First, we provide an example MLP neural network accelerator backend called DANA (a Dynamically Allocated Neural Network Accelerator). DANA uses a Processing Element (PE) model (similar to recent MLP accelerators in the approximate computing literature [Esmaeilzadeh et al., 2012b, Moreau et al., 2015]). However, in contrast to existing work, DANA does not execute a stored program implementing a neural network, but uses a binary data structure describing a neural network—what we refer to as a neural network configuration. DANA then can be viewed as a control unit capable of scheduling the constituent neurons described by a neural network configuration on its PEs. This model enables us to naturally support multiple transactions via the interleaving of neurons from outstanding requests.

Second, we provide hardware and software support for managing requests to access a backend neural network accelerator (with DANA being one example of such a backend). This infrastructure, X-FILES, comprises a set of hardware and software Extensions for the Integration of Machine Learning in Everyday Systems. On the hardware side, we detail an X-FILES Hardware Arbiter that manages transactions, i.e., requests to access DANA. We interface X-FILES/DANA as a coprocessor of a Rocket RISC-V microprocessor developed at UC Berkeley [UC Berkeley Architecture Research Group, 2016]. We then provide an X-FILES user software library that application developers can use to include neural network transactions in their software. We provide two sets of supervisor software: one that interfaces with a basic uniprocessing kernel developed at UC Berkeley called the Proxy Kernel [RISC-V Foundation, 2016b] and another that provides support for the Linux kernel.

Together, this system comprises Rocket + X-FILES/DANA, i.e., a Rocket microprocessor with an X-FILES transaction manager and a DANA accelerator. Finally we

<sup>&</sup>lt;sup>9</sup>We beseech the reader to forgive the acronyms—no FOX, SKINNER, or CGB SPENDER currently exist.

evaluate Rocket + X-FILES/DANA using power and performance criteria on single and multi-transaction workloads. All work related to X-FILES/DANA is provided under a 3-clause Berkeley Software Distribution (BSD) license on our public GitHub repository [Boston University Integrated Circuits and Systems Group, 2016].

In summary, the specific contributions of this dissertation are as follows:

- A fixed topology neural network accelerator architecture used for transcendental function approximation, T-fnApprox, that demonstrates the limits of function approximation techniques using digital accelerators [Eldridge et al., 2014]

- An architectural description of DANA, an arbitrary topology neural network accelerator architecture capable of processing multiple neural network transactions simultaneously [Eldridge et al., 2015]

- An architectural description of the X-FILES Hardware Arbiter, a hardware transaction manager that facilitates scheduling of transactions on a backend (of which DANA is provided as an example)

- A description of user and supervisor software necessary to facilitate the management of transactions on the X-FILES Hardware Arbiter from both a user and kernel perspective

- An evaluation of Rocket + X-FILES/DANA across the design space of X-FILES/DANA and on single and multi-transaction workloads

#### 1.4 Dissertation Outline

This dissertation is organized in the following manner. Section 2 details the history of neural networks as well as the copious work in this area related to hardware acceleration of neural networks and machine learning algorithms. Section 3 provides a description and evaluation of T-fnApprox, a fixed topology architecture used for

mathematical function approximation. The limitations of this architecture are high-lighted. Section 4 describes the X-FILES, hardware and software that enables the safe use of neural network accelerator hardware by multiple processes. Section 5 describes the architecture of our arbitrary topology neural network accelerator architecture, DANA, that acts as a backend accelerator for the X-FILES. Section 6 evaluates X-FILES/DANA, integrated with a RISC-V microprocessor on power and performance metrics. In Section 7, we conclude and discuss observations and future directions for this and related work.

## Chapter 2

## Background

#### 2.1 A Brief History of Neural Networks

The history of neural networks, artificial intelligence, and machine learning<sup>1</sup> is an interesting study in and of itself largely due to the fact that this history is dotted with proponents, detractors, significant advances, and three major waves of disappointment and associated funding cuts.<sup>2</sup> While not specifically necessary for the understanding of this dissertation or its contributions, we find that having some broad perspective on the history of neural networks provides the reader with necessary grounding that has unfortunately contributed to much of the past disappointment in neural networks as computational tools over the past seven decades.

#### 2.1.1 Neural networks and early computer science

The human brain or, much more generally, any cortical tissue has long been viewed as an inspirational substrate for developing computing systems. Put simply, humans and animals perform daily tasks which can be classified as computation (e.g., logical inference, mathematics, navigation, and object recognition) and they are exceedingly good at these tasks. Furthermore, these biological substrates are the result of millions of years of evolution lending credence to the belief that these substrates are, at worst,

<sup>&</sup>lt;sup>1</sup>We view these names as interchangeable—they all refer to similar aspects of the same underlying problem: How do we design machines capable of performing human-level feats of computation? The naming convention, historically, is largely an artifact of the research and funding climate at the time.

<sup>&</sup>lt;sup>2</sup>These waves of disappointment are generally referred to hyperbolically as AI winters.

suitable and, more likely, highly optimized. It is therefore reasonable to expect that such biological substrates provide guideposts towards developing machines capable of similar computational feats. Unsurprisingly, psychological and biological developments motivated and shaped the views of the emerging area of computer science during the early 20<sup>th</sup> Century.

Unfortunately, though perhaps unsurprisingly, the human brain is a highly complex organ whose mechanisms are exceedingly difficult to discern.<sup>3</sup> Nevertheless, cortical tissue does demonstrate some regular structure. Namely, such tissue is composed of interconnected elementary cells, neurons, that communicate through electrical and chemical discharges, synapses, that modify the electrical potential of a neuron.

While the full computational properties of biological neurons are complex and not completely understood,<sup>4</sup> neurons generally demonstrate behavior as threshold units: if the membrane potential, the voltage of the neuron augmented by the summation of incident connections, exceeds a threshold, the neuron generates a spike to its outgoing connected neurons. McCulloch and Pitts provide an axiomatic description of an artificial neuron in this way [McCulloch and Pitts, 1943].

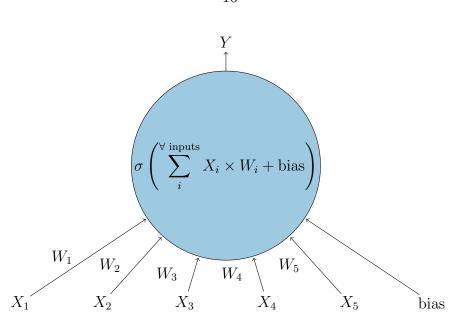

Broadly, an individual, artificial neuron in the style of McCulloch and Pitts is an approximation of a biological neuron. Each artificial neuron, like the one shown in Figure 2·1, consists of a unit that fires or does not fire in response to a number of inputs,  $X_i$ . Specifically, if the weighted sum of the inputs,  $X_i \times W_i$ , exceeds a bias, then the neuron "fires" and produces an output, Y. The firing action is determined by applying an activation function,  $\sigma$  in Figure 2·1, that represents some type of threshold. Common activation functions are either a sigmoid, returning values on

<sup>&</sup>lt;sup>3</sup>Relatedly, the blunt instruments of biologists, psychologists, and cognitive researchers exacerbate this problem [Lazebnik, 2004, Jonas and Kording, 2016].

<sup>&</sup>lt;sup>4</sup>A specific example here is the method of information storage of biological neurons—is information stored in the binary presence/absence of a synapse, in the timing of the synapses, in both simultaneously?

Figure  $2 \cdot 1$ : A single artificial neuron with five inputs

range [0, 1], or a hyperbolic tangent, returning values on range [-1, 1]. Other options include rectification using a ramp or softplus function to produce an unbounded output on range  $[0, \infty]$ .

Critically, McCulloch and Pitts also demonstrated how assemblies of neurons can be structured to represent logic functions (e.g., Boolean AND and OR gates), storage elements, and, through the synthesis of logic and storage, a Turing machine. Later work by Frank Rosenblatt solidified the biological notion of receptive fields, i.e., groups of neurons, here termed *perceptrons*, producing different behavior based on their local regions of activation [Rosenblatt, 1958]. The resulting body of work derived from and related to this approach is termed *connectionism*.

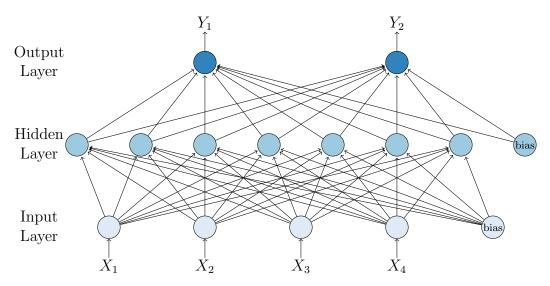

Assemblies of artificial neurons form artificial neural networks.<sup>5</sup> Figure 2·2 shows an example two-layer neural network. This neural network transforms four inputs,  $[X_1, X_2, X_3, X_4]$ , into two outputs  $[Y_1, Y_2]$ , through the use of seven hidden neurons. Each neuron in the hidden or output layer is a replica of the neuron shown in Fig-

<sup>&</sup>lt;sup>5</sup>We drop the "artificial" qualifier and just refer to artificial neural networks as "neural networks" throughout this dissertation.

Figure 2.2: A two layer neural network with four inputs and three outputs

ure  $2\cdot 1$ . Note that the neurons in the input layer are pass-through and do not modify their inputs. Through careful selection of weights, the neural network can be made to approximate a general input—output relationship or, much more simply and stated previously, arbitrary Boolean functions or collections of Boolean functions.

This fact was not lost on early pioneers of computer science who drew heavy inspiration from biological neurons when designing early computers.<sup>6</sup> In fact, it seemed only natural that neurons should form the basis of computing. Neurons could act like logic gates and Claude Shannon had already demonstrated the equivalence of existing digital circuit elements and Boolean logic [Shannon, 1938]. Qualitatively, John von Neumann specifically refers to the work of McCulloch and Pitts in his technical notes on the design of the EDVAC [von Neumann, 1993].<sup>7</sup> However, and more interestingly,

<sup>&</sup>lt;sup>6</sup>Similarly, this notion of neurons as Boolean functions coincidentally or causally aligns with the early 20<sup>th</sup> Century focus on the philosophy and foundation of mathematics with particular focus on Logicism, i.e., the efforts of Betrand Russel and Alfred North Whitehead to reduce mathematics to logic [Whitehead and Russell, 1912]. Granted, later proofs by Kurt Gödel make this line of thought less convincing and even intractable.

<sup>&</sup>lt;sup>7</sup>The Electronic Discrete Variable Automatic Computer was a bit serial computer developed for the United States Army's Ballistics Research Laboratory at the Aberdeen Proving Ground and a predecessor of the more well known ENIAC.

this biological motivation is implicit in von Neumann's descriptions of computational units as "Organs", the bit serial architecture of the EDVAC, and even in the very figures that von Neumann uses to describe the computational organs as assemblies of neurons. Similar sentiments, and almost entirely biologically-inspired designs, are presented again by von Neumann when he discusses approaches to build reliable computing systems [von Neumann, 1956]. Relatedly, Alan Turing commented extensively on the philosophical struggle of what it truly means for a machine to "think", i.e., reproduce the computational capabilities of the brain in a way indistinguishable to a human observer [Turing, 1950]. Programmatic approaches to general-purpose learning by machines, with psychological influences, can be seen by the concept of memoization as proposed by Donald Michie [Michie, 1968]. Here a machine (or a human), performs some action by rote memorization (e.g., via top-down dynamic programming) or by some rule (e.g., an algorithm).

In short, it is exceedingly difficult, though likely unnecessary, to decouple the predominant biological computing substrate, the brain, from artificial computing substrates. However, as this area of research progressed, traditional computing with logic gates as the primitives broke off from connectionist approaches that aligned with artificial intelligence efforts.

#### 2.1.2 Criticisms of neural networks and artificial intelligence

Nevertheless, this emerging area of artificial intelligence proceeded with fits and starts and notable high profile criticism.

First, Hubert Dreyfus, working for RAND corporation, provided a stark criticism of artificial intelligence research. Dreyfus' report questioned the fundamental assumptions of the brain as hardware and the mind as software [Dreyfus, 1965].<sup>8</sup> Put

<sup>&</sup>lt;sup>8</sup>It is interesting to note that the very title of this work, "Alchemy and Artificial Intelligence," draws parallels to modern work on deep neural networks—the networks are not fully understood and the construction and training of these networks is viewed as a black art.

simply, much of the research into building a machine with artificial intelligence hinges on the tenuous assumption that the brain, hardware, is a collection of neurons acting as logic gates and the mind, software, is either the organization or the program running on the hardware. However, just because neurons (or artificial representations of neurons) can be constructed in such a way that they behave like logic gates does not mean that this is the only function of neurons. Analogously, transistors, either metal-oxide-semiconductor field-effect-transistors (MOSFETs) or bipolar junction transistors (BJTs), can be arranged to behave like logic gates. However, this does not mean that such behavior encompasses the underlying physics or information processing capabilities of transistors.

Second, and most often recalled, Marvin Minsky and Seymour Papert published *Perceptrons* in 1969 that provided bounds on the fundamental computational limits of neurons [Minsky and Papert, 1987]. Specifically, and famously, Minksy describes the scenario of a single neuron, like that of Figure 2·1, being incapable of learning an XOR relationship due to the fact that this representation is not linearly separable. In effect, a single neuron is not a universal logic gate. Granted, the obvious counter criticism is that neural networks composed of more than one neuron in series can learn an XOR function. Nevertheless, this observation led to a decrease in interest in connectionist architectures.

Third, Sir James Lighthill provided a scathing critique of current artificial intelligence research with the dramatic effect being that the United Kingdom scaled back all research in this area [Lighthill, 1973]. Briefly, it is worth mentioning Lighthill's classification of AI research as it bears similarities to the continued difficulties and problems of research in the field (or machine learning/neural networks) today. Lighthill groups AI research into three main areas:

Improved Automation (class A) Work in this area encompasses improvements

to traditional techniques of object recognition, natural language processing, and similar topics. This work is relatively easy to evaluate as it can be compared directly against the best existing traditional approach that does not have any grounding in biology.

# Cognitive Neuroscience (CNS) Research assisted by a Computer (class C)

CNS research can be augmented and enhanced by the use of computers through the simulation of biological systems, e.g., neurons. Additionally, this allows for fundamental psychological concepts to be tested with assemblies similar to or inspired by biology.

Bridge Activities, chiefly Robotics (class B) This work attempts to combine fundamental CNS research with improved automation and often takes the form of, as Lighthill somewhat derogatorily calls, "building robots."

The identified split between Lighthill's A and C classes largely persists to this day. Fundamental advances in neural networks and machine learning has enabled dramatic improvements in automation, e.g., image classification. Similarly, the ability of models of the cortical tissue of the human or animal brain to be simulated in computer software or hardware allows for new insights to be gleaned in both neuroscience and psychology. However, the combination of these two research areas still leaves much to be desired. Put differently, biological inspiration cannot be a beneficial criteria in its own right or, similarly, adopting a biologically-inspired approach is no explicit guarantee of success. Nevertheless, there is no reason to not take inspiration from biology! The expectations, however, must be tempered appropriately. Furthermore, the lack of tempered expectations, promises, and restraint by researchers can be viewed as a dominant cause in the repeated periods of disenfranchisement with neural

<sup>&</sup>lt;sup>9</sup>This is something which I learned the hard way through an experiment involving a hardware implementation of a biologically-inspired approach to optical flow [Raudies et al., 2014]. While interesting in its own right, such work was unable to achieve comparable performance to a state of the art traditional, i.e., a non-biologically-inspired, approach.

networks.

In combined effect, these criticisms diminished interest (and funding) in connectionist approaches to artificial intelligence, i.e., approaches involving groupings of neurons into larger assemblies, until their resurgence in the 1990s.

# 2.1.3 Modern resurgence as machine learning

Following the initial downfall of connectionist approaches, the 1980s commercial artificial intelligence market was dominated by expert systems and Lisp machines that aimed to describe the world with rules. Nevertheless, these systems and their associated companies were largely defunct by the 1990s. However, the reemergence of connectionist approaches can be seen during the 1980s and, generally, as a continuation of computing by taking inspiration from biology.

While the work of McCulloch and Pitts as well as Rosenblatt provided some biological grounding for artificial intelligence, Hubel and Wiesel provided a concrete model for how the visual processing system operates. In their work on the cat visual cortex, they demonstrated that certain cells are sensitive to points over specific regions of the retina, i.e., the receptive fields of Rosenblatt [Rosenblatt, 1958]. Further along in the visual processing system, other cells are sensitive to lines (collections of points) and still others to collections of lines or specific motions [Hubel and Wiesel, 1965]. Put simply, biological visual processing systems are hierarchically organized and construct complex structures from simpler primitives.

Fifteen years later, a more concrete structure for a generic connectionist architecture inspired by the visual processing system as experimentally determined by Hubel and Wiesel emerged—the work on the Neocognitron by Fukushima [Fukushima, 1980]. Additionally, evidence and techniques that allowed neural networks to be incrementally modified through error backpropagation to represent an arbitrary input—output relationship [Rumelhart et al., 1988] reignited significant interest in connectionism.

Nevertheless, approaches were plagued by the so-called vanishing gradient problem where the gradient decreases exponentially with the number of layers in a network. In result, the features used by an architecture like the Neocognitron had to be hand selected and could not be generally learned.

A number of approaches towards dedicated neural network computers or hardware to enable neural network computation in the 1990s [Fakhraie and Smith, 1997]. However, the lineage of Hubel and Wiesel to Fukushima and general research into connectionist approaches to artificial intelligence were maintained and furthered during this time by the so-called Canadian mafia: Yann LeCun, Geoff Hinton, and Yoshua Bengio. LeCun provided prominent work into convolutional neural networks, i.e., neural networks inspired by the visual processing system that use convolutional kernels as feature extractors (whose size effectively defines a receptive field), and their training [Lecun et al., 1998]. Similarly, Hinton provided a means of training another type of deep neural network—a deep belief network composed of stacked Restricted Boltzmann Machines—using a layer-wise approach [Hinton et al., 2006]. This work, and followup work in this area, provide a means of avoiding the vanishing gradient problem through connectivity restrictions or layer-wise training and demonstrated the capabilities of connectionist approaches to solve difficult problems: image classification and scene segmentation.

In consequence, these successes, and numerous ones since, have created a dramatically increased and resurgent interest in machine learning. However, the general utility of machine learning is not in its ability to solve a specific niche problem, e.g., image classification. Machine learning provides a general class of substrates, neural networks and their variants, for automatically extracting some structure in presented data. This contrasts dramatically with traditional, algorithmic computing where a complete understanding of a specific problem is required. Instead, machine learning

Table 2.1: Related work on neural network software and hardware

| Category              | Work                                                                               | Citation                                                                                                                                                                                                                                                    |

|-----------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Software Libraries    | FANN Theano Caffe cuDNN Torch Tensorflow                                           | [Nissen, 2003]<br>[Al-Rfou et al., 2016]<br>[Jia et al., 2014]<br>[Chetlur et al., 2014]<br>[Collobert et al., ]<br>[Abadi et al., 2015]                                                                                                                    |

| Spiking Hardware      | SpiNNaker<br>TrueNorth                                                             | [Khan et al., 2008]<br>[Preissl et al., 2012]                                                                                                                                                                                                               |

| Hardware Architecture | RAP SPERT NPU NPU-Analog DianNao DaDianNao NPU-GPU PuDianNao SNNAP TABLA DNNWEAVER | [Morgan et al., 1992] [Asanović et al., 1992] [Esmaeilzadeh et al., 2012b] [Amant et al., 2014] [Chen et al., 2014a] [Chen et al., 2014b] [Yazdanbakhsh et al., 2015] [Liu et al., 2015] [Moreau et al., 2015] [Mahajan et al., 2016] [Sharma et al., 2016] |

| FPGA Hardware         | HMAX-FPGA<br>ConvNet                                                               | [Kestur et al., 2012]<br>[Farabet et al., 2013]                                                                                                                                                                                                             |

can be viewed as a soft computing paradigm where approximate or inexact solutions are served for problems with no known algorithmic (or non NP-hard) solution is currently known.

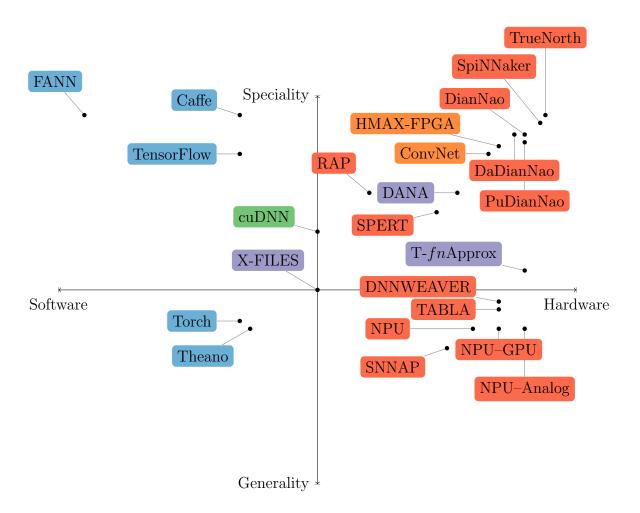

# 2.2 Neural Network Software and Hardware

The long tail of neural network research and modern, resurgence interest has resulted in a wide array of historical and recent software and hardware for performing and accelerating neural network computation. Table 2.1 shows a summary of related work discussed in this section. Critical to the contributions of this thesis, prior implementations focus on machine learning as the underlying application.

#### 2.2.1 Software

Machine learning software can be divided into roughly two categories:

- Software specific for machine learning

- Software for scientific (or mathematical) computation

In the former space, the Fast Artificial Neural Network (FANN) library is a representative example [Nissen, 2003]. This is a C library (with an optional C++ wrapper) that allows for computations with arbitrary multilayer perceptron neural networks and training using backpropagation algorithms. However, due to the time during which FANN was developed (i.e., 2003), this software library was optimized for a single CPU implementation—specifically with the use of software pipelining.

More recent versions of dedicated machine learning software include Caffe [Jia et al., 2014] and Tensorflow [Abadi et al., 2015]. In contrast with FANN, both of these libraries target deep learning specifically, i.e., convolutional neural networks or deep neural networks. In light of their much more recent development than something like FANN, they both target the predominant architecture for training neural networks—GPUs. GPU programming, while initially archaic in the sense that a user had to translate their program into an explicit graphics language, e.g., OpenGL. However, NVIDIA introduced CUDA, a C/C++-like language that enables more straightforward programming on the parallel architecture of a GPU, in 2007. The natural parallelism inherent in machine learning workloads makes GPUs a prime target for bearing the computational burdens of both feedforward inference and learning. To further bolster their support of this, NVIDIA introduced cuDNN, deep neural network (DNN) extensions to its existing CUDA library for programming GPUs [Chetlur et al., 2014].

Alternatively, though the boundary is somewhat fuzzy, more generic scientific computing packages can be used to describe machine learning algorithms. These libraries include Theano [Al-Rfou et al., 2016] and Torch [Collobert et al., ]. Similarly, both of these provide support for targeting both CPU and GPU backends.

Nevertheless, all of these existing software implementations treat machine learning as the underlying application as opposed to just one more way of approaching a problem.

### 2.2.2 Hardware

Hardware implementations can be broadly broken down along the guidelines of Lighthill's A (advanced automation) and C (cognitive neuroscience) classes. Class A implementations involve artificial neural networks which includes multilayer perceptron and convolutional/deep implementations. Class C generally uses a spiking model for inter-neuron computation. However, while Class C can obviously be utilized for neuroscience simulations, these implementations often merge into Class A or B and attempt to provide some utility for a specific application domain.

Biologically-inspired approaches include SpiNNaker [Khan et al., 2008] and IBM's recent entry, TrueNorth [Preissl et al., 2012]. Both use spiking neural network models and provide a more biologically-accurate view of neural network hardware. Nevertheless, the general utility of these types of systems for Class A tasks is widely disputed, e.g., in comments by Yann LeCun to the New York Times [Markoff, t B1]. Specifically, artificial neural networks, like convolutional neural networks, tend to outperform spiking models on the same tasks. While this does not preclude their use for Class A tasks, most of these systems are relegated to Class C.

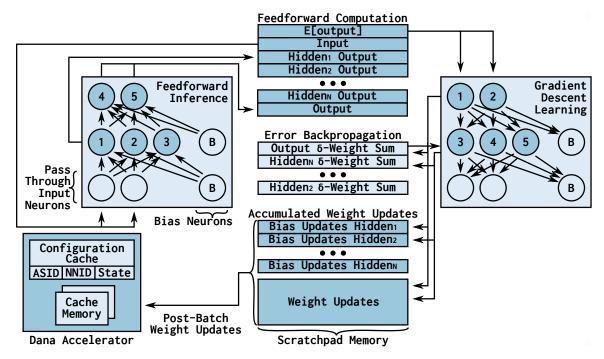

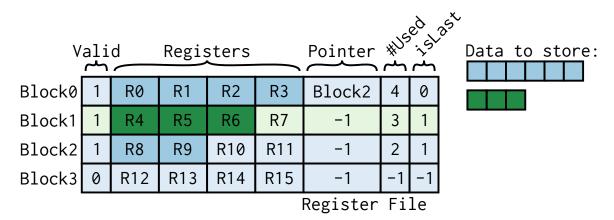

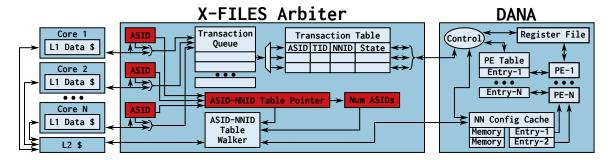

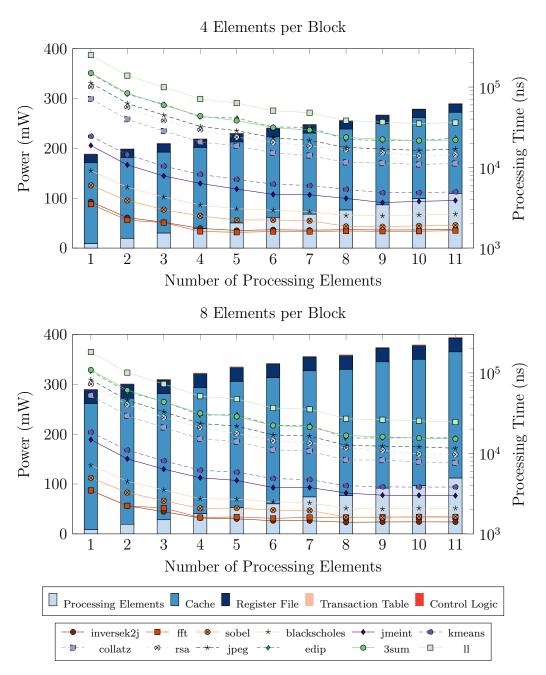

Artificial neural network hardware accelerators were explored in the 1990s, specifically with the Ring Array Processor (RAP) [Morgan et al., 1990, Przytula, 1991, Morgan et al., 1992] and SPERT [Asanović et al., 1992, Wawrzynek et al., 1996]. RAP utilized a collection of digital signal processors (DSPs) connected via a ring bus. Individual neurons can then be assigned to specific DSPs with broadcast communi-