## BOSTON UNIVERSITY COLLEGE OF ENGINEERING

## Dissertation

# A MULTI-LAYER APPROACH TO DESIGNING SECURE SYSTEMS: FROM CIRCUIT TO SOFTWARE

by

## **BOYOU ZHOU**

B.S., Southeast University, China, 2013M.S., Boston University, 2019

Submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

2019

## Approved by

First Reader

Ajay J. Joshi, PhD

Associate Professor of Electrical and Computer Engineering

Second Reader

Manuel Egele, PhD

Assistant Professor of Electrical and Computer Engineering

Third Reader

M. Selim Ünlü, PhD

Professor of Electrical and Computer Engineering Professor of Materials Science and Engineering Professor of Biomedical Engineering

Fourth Reader

Gianluca Stringhini, PhD

Assistant Professor of Electrical and Computer Engineering

$Ignorance\ is\ bliss$

– Thomas Gray (1742)

### Acknowledgments

First, I would like to express my gratitude to my advisor, Ajay Joshi. This work would not have been possible without Ajay's guidance and help. I am also thankful to Prof. Manuel Egele, as my co-advisor, for the last three years. He advised and guided most of my works during this process. My regret throughout the entire graduate school was to get to know him sooner. I also appreciate the help from Prof. Selim Unlu, for the guidance in our photonic project. I want to thank the funding agency, NSF and DARPA, to support all my works.

It goes without saying, without support from my parents, Jianhua Zhou, and Qi Jin, this work is not possible. Also, my girlfriend, Weisi Liao, was also incredibly supportive to help me through this process.

I also want to thank my collaborators, Ronen Adato, Aydan Aksoylar, Anmol Gupta, Rasoul Jahanshahi, Negin Zaraee, and Sadulla Canakci. With their collaborations, I could finish the works and publish them in the past few years. I would like to thank Boston University for funding most of my works and DARPA for the Posh open source hardware project (POSH). I also appreciate my colleagues in our group: Leila, Zahra, Yenai, Furkan, Marcia, Saiful, Zafar, Mahmoud, Schuyler, and Chao. I would never forget the life with them, the life sharing all happiness. This goes to the PEAC and CAAD labs too.

## A MULTI-LAYER APPROACH TO DESIGNING SECURE SYSTEMS: FROM CIRCUIT TO SOFTWARE

#### **BOYOU ZHOU**

Boston University, College of Engineering, 2019

Major Professors: Ajay J. Joshi, PhD

Associate Professor of Electrical and Computer

Engineering

Manuel Egele, PhD

Assistant Professor of Electrical and Computer

Engineering

#### ABSTRACT

In the last few years, security has become one of the key challenges in computing systems. Failures in the secure operations of these systems have led to massive information leaks and cyber-attacks. Case in point, the identity leaks from Equifax in 2016, Spectre and Meltdown attacks to Intel and AMD processors in 2017, Cyber-attacks on Facebook in 2018. These recent attacks have shown that the intruders attack different layers of the systems, from low-level hardware to software as a service (SaaS). To protect the systems, the defense mechanisms should confront the attacks in the different layers of the systems. In this work, we propose four security mechanisms for computing systems: (i) using backside imaging to detect Hardware Trojans (HTs) in Application Specific Integrated Circuits (ASICs) chips, (ii) developing energy-efficient reconfigurable cryptographic engines, (iii) examining the feasibility of malware detection using Hardware Performance Counters (HPC).

Most of the threat models assume that the root of trust is the hardware running

beneath the software stack. However, attackers can insert malicious hardware blocks, i.e. HTs, into the Integrated Circuits (ICs) that provide back-doors to the attackers or leak confidential information. HTs inserted during fabrication are extremely hard to detect since their overheads in performance and power are below the variations in the performance and power caused by manufacturing. In our work, we have developed an optical method that identifies modified or replaced gates in the ICs. We use the near-infrared light to image the ICs because silicon is transparent to near-infrared light and metal reflects infrared light. We leverage the near-infrared imaging to identify the locations of each gate, based on the signatures of metal structures reflected by the lowest metal layer. By comparing the imaged results to the pre-fabrication design, we can identify any modifications, shifts or replacements in the circuits to detect HTs.

With the trust of the silicon, the computing system must use secure communication channels for its applications. The low-energy cost devices, such as the Internet of Things (IoT), leverage strong cryptographic algorithms (e.g. AES, RSA, and SHA) during communications. The cryptographic operations cause the IoT devices a significant amount of power. As a result, the power budget limits their applications. To mitigate the high power consumption, modern processors embed these cryptographic operations into hardware primitives. This also improves system performance. The hardware unit embedded into the processor provides high energy-efficiency, low energy cost. However, hardware implementations limit flexibility. The longevity of the IoTs can exceed the lifetime of the cryptographic algorithms. The replacement of the IoT devices is costly and sometimes prohibitive, e.g., monitors in nuclear reactors. In order to reconfigure cryptographic algorithms into hardware, we have developed a system with a reconfigurable encryption engine on the Zedboard platform. The hardware implementation of the engine ensures fast, energy-efficient cryptographic operations.

With reliable hardware and secure communication channels in place, the computing systems should detect any malicious behaviors in the processes. We have explored the use of the Hardware Performance Counters (HPCs) in malware detection. HPCs are hardware units that count micro-architectural events, such as cache hits/misses and floating point operations. Anti-virus software is commonly used to detect malware but it also introduces performance overhead. To reduce anti-virus performance overhead, many researchers propose to use HPCs with machine learning models in malware detection. However, it is counter-intuitive that the high-level program behaviors can manifest themselves in low-level statics. We perform experiments using  $2 \sim 3 \times$  larger program counts than the previous works and perform a rigorous analysis to determine whether HPCs can be used to detect malware. Our results show that the False Discovery Rate of malware detection can reach 20%. If we deploy this detection system on a fresh installed Windows 7 systems, among 1,323 binaries, 198 binaries would be flagged as malware.

## Contents

| 1 | Intr | roducti | ion                                                        | 1  |

|---|------|---------|------------------------------------------------------------|----|

|   | 1.1  | Backg   | round and Motivation                                       | 1  |

|   | 1.2  | Relate  | ed Work                                                    | 5  |

|   |      | 1.2.1   | HT Detection using Backside Imaging                        | 6  |

|   |      | 1.2.2   | Cryptographic Engines for IoT Devices                      | 8  |

|   |      | 1.2.3   | Malware Detection using Hardware Performance Counters with |    |

|   |      |         | Machine Learning                                           | 10 |

|   | 1.3  | Comp    | leted Research                                             | 14 |

| 2 | Har  | dware   | Trojan Detection Using Backside Imaging                    | 17 |

|   | 2.1  | Introd  | luction                                                    | 17 |

|   | 2.2  | Threa   | t Model                                                    | 20 |

|   | 2.3  | Backs   | ide Imaging of IC Chips                                    | 20 |

|   |      | 2.3.1   | Optical Imaging Method                                     | 22 |

|   |      | 2.3.2   | Technology Scalability                                     | 25 |

|   |      | 2.3.3   | Optical Simulation Methodology                             | 26 |

|   | 2.4  | HT D    | etection Process                                           | 28 |

|   |      | 2.4.1   | Methodology to Generate "Golden Reference"                 | 28 |

|   |      | 2.4.2   | Correlation Method                                         | 31 |

|   |      | 2.4.3   | Results                                                    | 32 |

|   | 2.5  | Noise-  | Based Detection Method                                     | 33 |

|   |      | 2.5.1   | Methodology Explanation                                    | 34 |

|     |                             | 2.5.2  | Results                                                | 36         |

|-----|-----------------------------|--------|--------------------------------------------------------|------------|

| 2   | .6                          | Optim  | izations of HT Detection                               | 38         |

|     |                             | 2.6.1  | Process Variation                                      | 38         |

|     |                             | 2.6.2  | Resolution and Window Size                             | 39         |

|     |                             | 2.6.3  | Pattern Insertion                                      | 40         |

|     |                             | 2.6.4  | Results                                                | 41         |

| 2   | .7                          | Nanoa  | ntenna Implementations                                 | 43         |

| 2   | .8                          | Conclu | sion                                                   | 44         |

| 3 ( | $\mathbf{cry}_{\mathbf{j}}$ | ptogra | phic Algorithms on a Programmable SoC for IoT Devices  | <b>54</b>  |

| 3   | .1                          | Introd | uction                                                 | 54         |

| 3   | .2                          | Threat | Model                                                  | 58         |

| 3   | .3                          | Backgr | round                                                  | 58         |

|     |                             | 3.3.1  | Cryptographic Algorithms                               | 58         |

|     |                             | 3.3.2  | Cryptographic Accelerators                             | 59         |

|     |                             | 3.3.3  | A case for FPGA based Crypto                           | 61         |

| 3   | .4                          | Experi | mental Setup                                           | 62         |

| 3   | .5                          | Evalua | tion                                                   | 66         |

|     |                             | 3.5.1  | Symmetric Cryptography                                 | 67         |

|     |                             | 3.5.2  | Asymmetric Cryptography                                | 68         |

|     |                             | 3.5.3  | Hash Function                                          | 68         |

| 3   | .6                          | Conclu | sion                                                   | 68         |

| 4 N | /Ial                        | ware I | Detection using Hardware Performance Counters with Ma- |            |

| c   | hin                         | e Lear | ning                                                   | <b>7</b> 5 |

| 4   | .1                          | Introd | uction                                                 | 75         |

| 4   | .2                          | Threat | Model                                                  | 79         |

| 4   | .3                          | Experi | mental Setup                                           | 79         |

|    |                    | 4.3.1   | Savitor (HPC measuring tool)                               | 80  |

|----|--------------------|---------|------------------------------------------------------------|-----|

|    |                    | 4.3.2   | Malware and Benignware                                     | 81  |

|    |                    | 4.3.3   | Method for Running Experiments                             | 82  |

|    | 4.4                | Machi   | ne Learning Models                                         | 84  |

|    |                    | 4.4.1   | Reduction of Dimensions                                    | 84  |

|    |                    | 4.4.2   | Selection of Events                                        | 86  |

|    |                    | 4.4.3   | Classification Models                                      | 91  |

|    | 4.5                | Experi  | imental Results                                            | 94  |

|    |                    | 4.5.1   | Malware Detection                                          | 96  |

|    |                    | 4.5.2   | Cross-Validation                                           | 100 |

|    |                    | 4.5.3   | Ransomware                                                 | 103 |

|    | 4.6                | Discus  | sion                                                       | 104 |

|    | 4.7                | Conclu  | asion                                                      | 104 |

| 5  | Con                | clusio  | ns and Future Work                                         | 106 |

|    | 5.1                | Hardw   | vare Trojan Detection using near-Infrared Backside Imaging | 106 |

|    | 5.2                | High-F  | Performance Low Energy Implementation of Cryptographic Al- |     |

|    |                    | gorith  | ms on a Programmable SoC for IoT Devices                   | 108 |

|    | 5.3                | Malwa   | are Detection using Hardware Performance Counters with Ma- |     |

|    |                    | chine l | Learning                                                   | 109 |

| Re | efere              | nces    |                                                            | 111 |

| Cı | arric <sup>.</sup> | ulum V  | √itae                                                      | 124 |

|    |                    |         |                                                            |     |

## List of Tables

| 1.1 | Comparison between various previous works: Rows are various works                  |    |

|-----|------------------------------------------------------------------------------------|----|

|     | in HPC-based malware detection and columns are design choices. The                 |    |

|     | alternative shaded and white background represents different categories            |    |

|     | of tool/setup/model in malware detection using HPCs. Red texts high-               |    |

|     | light drawbacks, and black texts express the suggested tool/setup/model $$         |    |

|     | from this work. Solid dots $(\bullet)$ indicate the use of that tool/setup/model   |    |

|     | (column) by the reference (row), and hollow dimonds $(\diamond)$ indicate the      |    |

|     | non-use of that tool/setup/model by the reference. Star $(\star)$ is our work.     |    |

|     | Our work avoids the drawbacks discussed in the table, and quantita-                |    |

|     | tively analyzes how these drawbacks lead to the conclusion that HPCs               |    |

|     | can reliably detect hardware                                                       | 12 |

| 2.1 | Area (in $\mu m^2$ ) In this table, we show power consumption of all the           |    |

|     | testbenches that we implemented in this paper                                      | 33 |

| 2.2 | Area of Inserted fill cells $[\mu m^2]$ , 0.19, 0.38, 0.57 represents the width of |    |

|     | each fill cell in the array in $[\mu m]$ , 1, 2, 3, 4 represents number of rows    |    |

|     | and columns of the array                                                           | 42 |

| 3.1 | This table shows the LUTs utilizations in FPGA of different crypto-                |    |

|     | engines                                                                            | 66 |

| 4.1 | Description of the Selected Events (AMD, 2015)                                     | 90 |

| 4.2 | Detection   | Rates         | with TT  | A1 and | l TTA2:   | Red mean     | s the   | value is | less |    |

|-----|-------------|---------------|----------|--------|-----------|--------------|---------|----------|------|----|

|     | than $50\%$ | and <b>bo</b> | old mear | s that | the value | e is more tl | nan 90° | %        |      | 93 |

## List of Figures

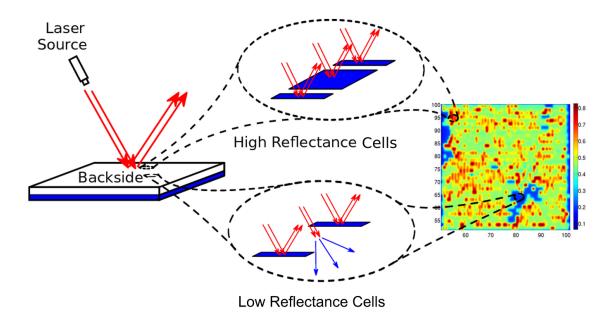

| 2.1         | Backside Imaging of IC chips                                                         | 21 |

|-------------|--------------------------------------------------------------------------------------|----|

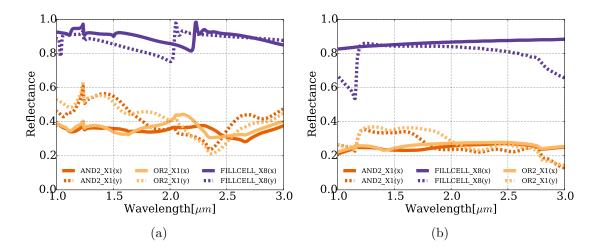

| 2.2         | (a) The reflectance spectrum of functional gates and fill cells designed             |    |

|             | in 45 nm technology (computed via FDTD simulations). The response                    |    |

|             | is computed for both X and Y polarizations of the illuminating field                 |    |

|             | (solid and dashed lines, respectively). For X polarization, the incident             |    |

|             | electric field is polarized along the VDD and VSS rails. For Y polariza-             |    |

|             | tion, the polarization is perpendicular. (b) The reflectance spectrum                |    |

|             | of functional gates and fill cells designed using 15nm technology. Fill              |    |

|             | cells still show much higher reflectance compared to functional cells.               | 24 |

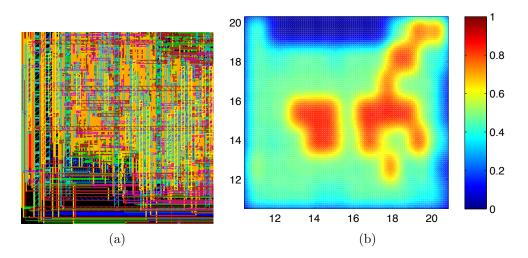

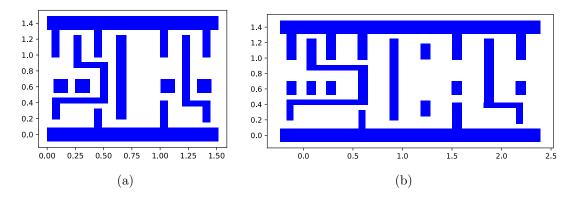

| $2 \cdot 3$ | (a) Physical layout of a $10\mu m \times 10\mu m$ region of the AEST100 hardware     |    |

|             | block. (b) Backside image (reflectance value) of the $10\mu m \times 10\mu m$        |    |

|             | region. The fill cells have the highest reflectance.                                 | 29 |

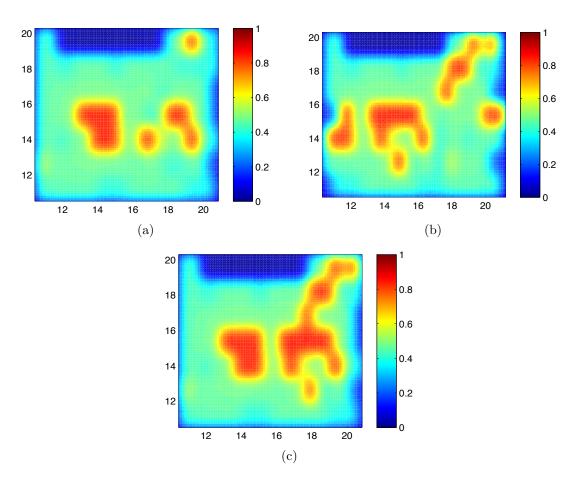

| $2 \cdot 4$ | (a) Backside image (reflectance value) of the $10\mu m \times 10\mu m$ region        |    |

|             | where the fill cells are replaced with functional gates that constitute              |    |

|             | the HTs. (b) Backside image (reflectance value) of the $10\mu m \times 10\mu m$      |    |

|             | region where the bottom 3 rows are shifted by 5 $\mu\mathrm{m}$ to the left to make  |    |

|             | room for cells that constitute the HT. (c) Backside image (reflectance               |    |

|             | value) of the $10\mu m \times 10\mu m$ region when the functional cells are replaced |    |

|             | by a different set of cells that constitute the HT                                   | 30 |

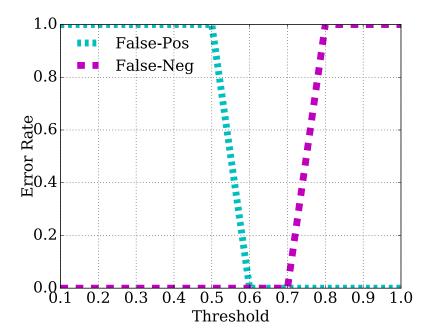

| 2.5 | By having Monte-Carlo simulation of detection error rate against de-          |    |

|-----|-------------------------------------------------------------------------------|----|

|     | tection threshold, we calculate false positive and false negative error       |    |

|     | rates versus threshold. The optimized detection threshold should be           |    |

|     | 0.65 for a fixed SNR of 10                                                    | 32 |

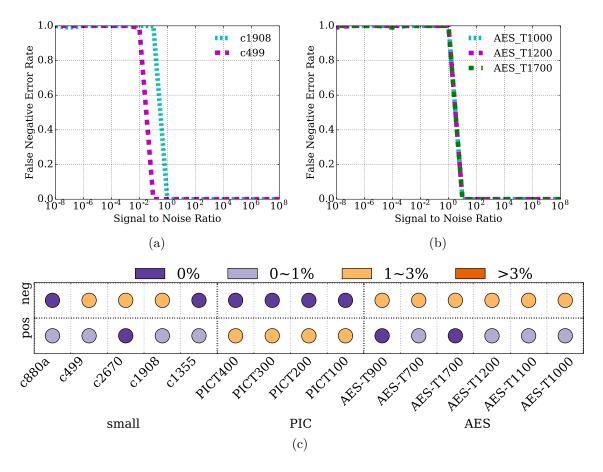

| 2.6 | (a) shows false negative error rates versus SNR of c1908 and c499 test-       |    |

|     | benches from (Wei et al., 2012a) using correlation comparison method.         |    |

|     | (b) shows AES-T1000, AES-T1200, and AES-T1700 testbenches from (Tr            | u, |

|     | 2014) using correlation comparison method. (c) is a summary of vari-          |    |

|     | ous testbenches from both (Wei et al., 2012a) and (Tru, 2014). We use         |    |

|     | colors in the legend to denote the error rates at SNR from $10^{-8}$ to $0.1$ |    |

|     | belonging to the corresponding range                                          | 46 |

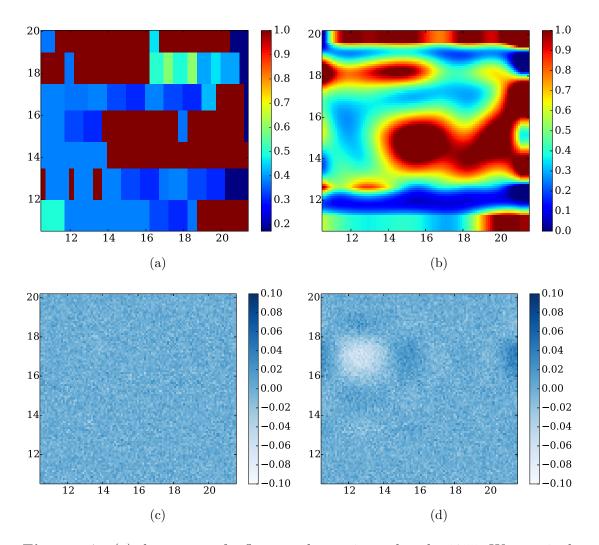

| 2.7 | (a) shows part of reflectance layout in testbench c1355. We use single        |    |

|     | gate FDTD results of the optical responses to represent every pixels          |    |

|     | in the gate location. (b) shows the cubic interpolated results from (a)       |    |

|     | as the reference of non-tampered circuit, which we denote it $M_Y$ . (c)      |    |

|     | is AWGN with a variant 0.01 of the same area. (d) is one tampered             |    |

|     | circuit example, in which we replace one NAND gate with an AND                |    |

|     | gate. We use the measure response, $M_Y$ , subtracted by the "golden          |    |

|     | reference", $M_X$ , to get the image in (d)                                   | 47 |

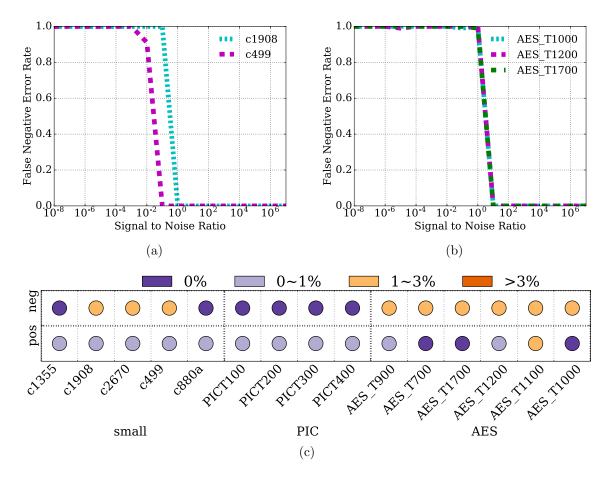

| 2.8 | (a) shows false negative error rates versus SNR of two testbenches            |    |

|     | from (Wei et al., 2012a) using noise detection method. (b) shows three        |    |

|     | testbenches from (Tru, 2014) using noise detection method. (c) is a           |    |

|     | summary of various test<br>benches from both (Wei et al., 2012a) and (Tru, $$ |    |

|     | 2014). We use colors in the legend to denote the error rates at SNR           |    |

|     | from $10^{-8}$ to 0.1 belonging to the corresponding range                    | 48 |

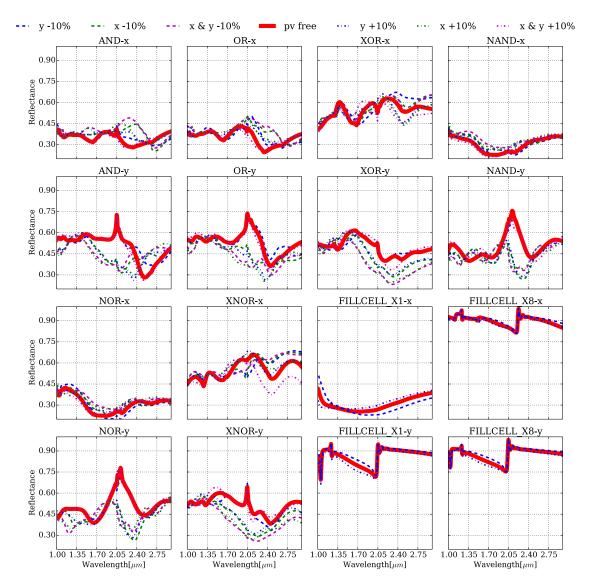

| 2.9  | Reflectance under $\pm 10\%$ variation in dimensions of metal1 structures                      |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | through near-IR laser of wavelength from $1\mu\mathrm{m}$ to $3\mu\mathrm{m}$ . X polarization |    |

|      | laser reflectance is on the left and Y polarization laser reflectance is                       |    |

|      | on the right. The thick red line represents the process variation free                         |    |

|      | reflectance of XOR2_X1 cell. The other lines are the reflectance with                          |    |

|      | process variation                                                                              | 49 |

| 2.10 | (a) Process variation free XOR2_X1 gate. (b) XOR2_X1 with $10\%$                               |    |

|      | process variation in the X dimension. Here, all the metal structures                           |    |

|      | inside of the gate have been compressed by 10% on the X dimension                              |    |

|      | to model process variations                                                                    | 50 |

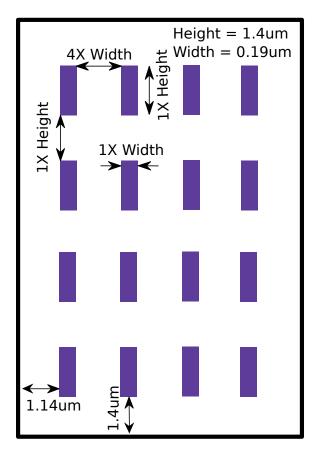

| 2.11 | Fill cell pattern that we inserted before $place\&route$ of the design.                        |    |

|      | We put this array of fill cells to secure these regions from shifts or                         |    |

|      | replacements of fill cells and replacement of functional cells with other                      |    |

|      | set of functional cells                                                                        | 51 |

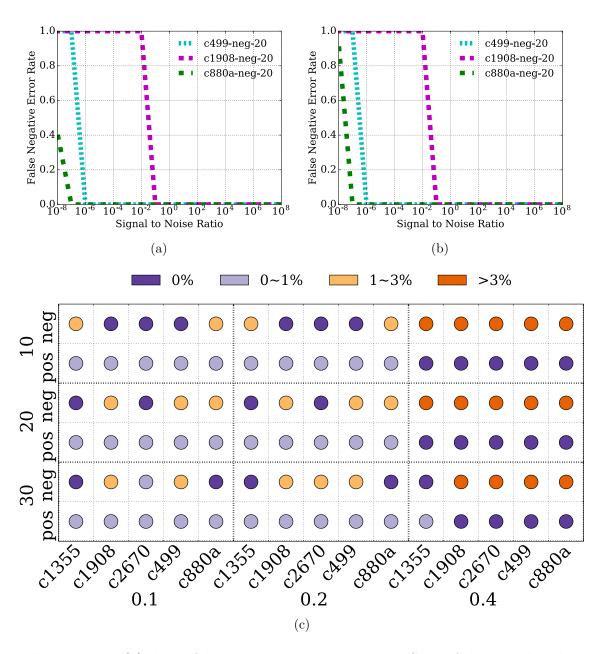

| 2.12 | (a) shows false negative error rates versus SNR of three testbenches                           |    |

|      | from (Tru, 2014) with an imaging resolution of $0.1 \mu m$ . (b) shows three                   |    |

|      | of testbenches from (Tru, 2014) using noise detection method with an                           |    |

|      | imaging resolution of $0.2\mu m$ . (c) is a summary of various testbenches                     |    |

|      | from both (Wei et al., 2012a). We use colors in the legend to denote                           |    |

|      | the error rates at SNR from $10^{-8}$ to 0.1 belonging to the corresponding                    |    |

|      | range. Here, 10, 20, and 30 refer to detection window sizes $10\mu m$ ,                        |    |

|      | $20\mu m,~30\mu m,$ On the X axis, 0.1, 0.2, and 0.4 refer to resolutions of                   |    |

|      | the image as $0.1\mu m$ , $0.2\mu m$ , and $0.4\mu m$ , respectively                           | 52 |

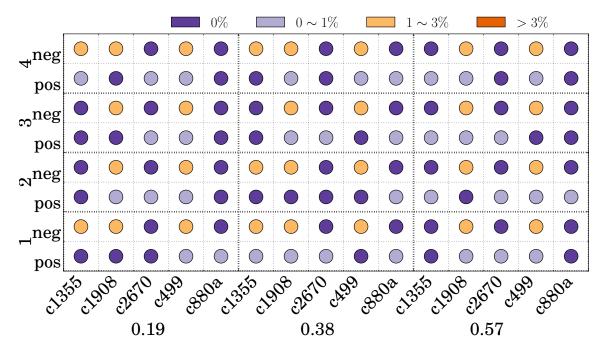

| 2.13 | This figure shows a table of detection rate with different designs of             |    |

|------|-----------------------------------------------------------------------------------|----|

|      | patterns. In all the patterns, we use same number of rows and columns             |    |

|      | of fill cell arrays. On the y axis, the number represents number of rows          |    |

|      | and columns that we used in fill cell array. On the x axis, the number            |    |

|      | represents the size of fill cells in the array                                    | 53 |

| 2.14 | (a) shows the metal 1 layer of the AND and NAND gate pair. (b)                    |    |

|      | shows the metal 1 layer of the AND and NAND with 322 nm distances                 |    |

|      | between metal structures and 200 nm nano-antenna between the two                  |    |

|      | gates                                                                             | 53 |

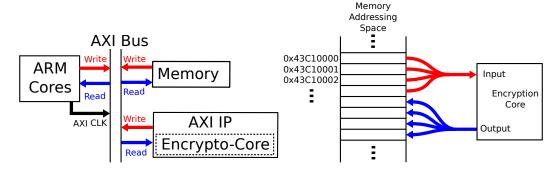

| 3.1  | System Architecture for AES Encryption Engine                                     | 62 |

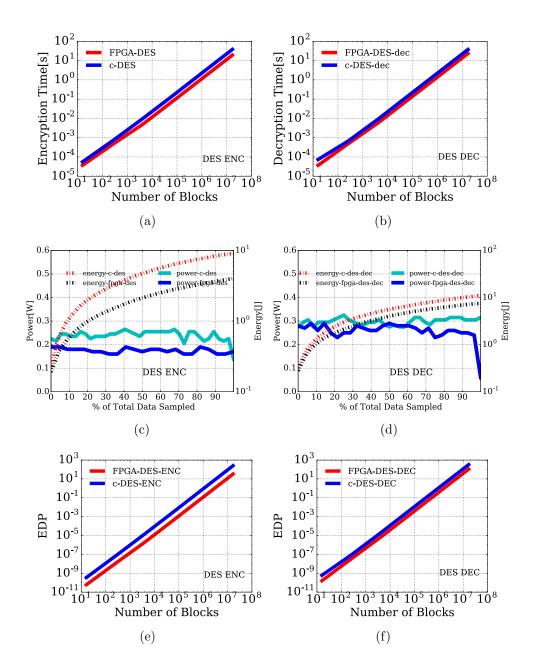

| 3.2  | Figures show the comparisons between C implementation (software),                 |    |

|      | and FPGA implementation (hardware) of DES in encryption (ENC)                     |    |

|      | and decryption (DEC). We encrypt and decrypt ranging from 16 blocks               |    |

|      | to 16 <sup>6</sup> blocks. (a) and (b) show time comparisons. Encryption shows    |    |

|      | $1.9 \times$ faster and decryption is $1.6 \times$ faster. (c) and (d) show power |    |

|      | consumption and energy comparisons. Encryption has $3.9\times$ energy             |    |

|      | reduction and decryption has $1.9\times$ energy reduction. (e) and (f) show       |    |

|      | EDP comparisons. Encryption has $7.6 \times$ savings and decryption has           |    |

|      | $3.0 \times$ savings. We can see performance boost, energy savings and EDP        |    |

|      | reductions of hardware implementation in DES                                      | 70 |

71

72

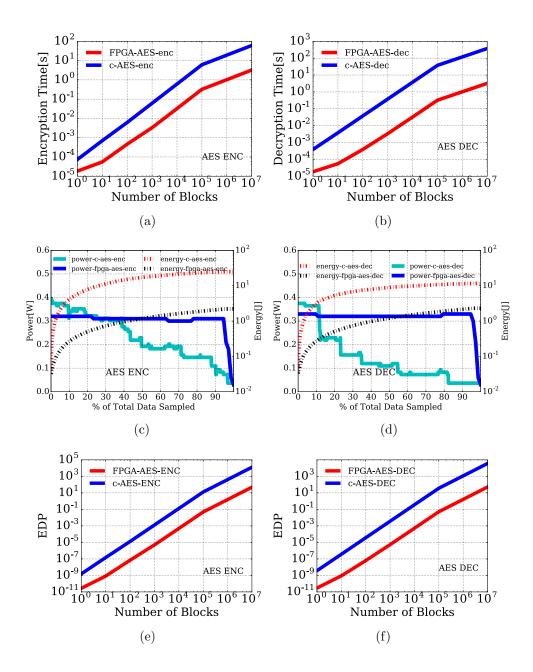

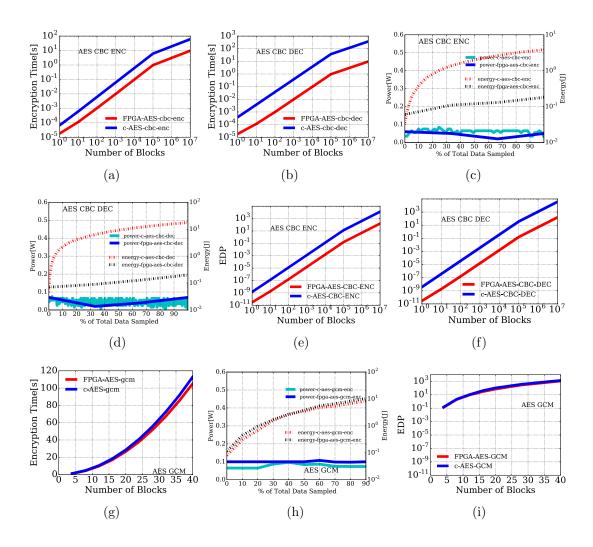

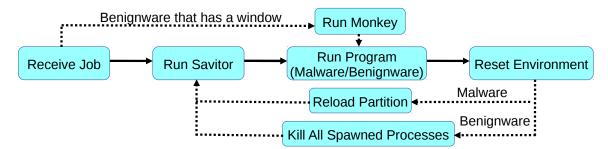

Figures show the comparisons between C implementation (software), and FPGA implementation (hardware) of AES block cipher modes, for both CBC and GCM. In all the hardware implementations, AES core engine operations use FPGA, while block cipher modes use c implementation. Thus, we still can see significant performance boost and energy savings in CBC modes, while much less benefits in GCM modes. In CBC mode, we encrypt and decrypt data ranging from 1 block to 10<sup>7</sup> blocks. In GCM mode, we encrypt data ranging from 4 to 40 blocks. (a), (b) and (g) show time comparisons. CBC encryption is 6.3× faster, CBC decryption is 38.6× and GCM is 1.1× faster. (c), (d) and (h) show power consumption and energy comparisons. CBC encryption has 33.2× energy reduction, CBC decryption has 154.8× energy reduction and GCM has 1.2× energy reduction. (e), (f) and (i) show EDP comparisons. CBC encryption has 82.4× savings, CBC decryption has 233.4× savings, and GCM has 1.3× savings. . . . . . .

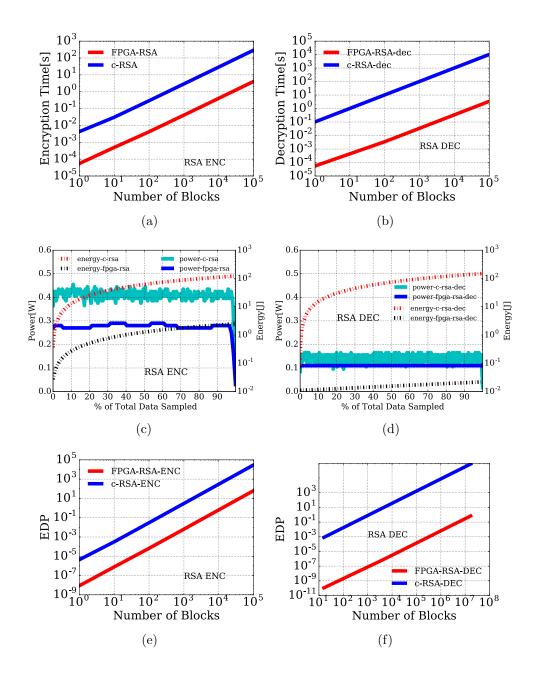

| 3.5 | Figures show the comparisons between C implementation (software),                   |    |

|-----|-------------------------------------------------------------------------------------|----|

|     | and FPGA implementation (hardware) of RSA in encryption (ENC)                       |    |

|     | and decryption (DEC). We encrypt and decrypt ranging from 1 block                   |    |

|     | to $10^5$ blocks. (a) and (b) show time comparisons. Encryption is                  |    |

|     | $71.2\times$ faster and decryption is $2983.1\times$ faster. (c) and (d) show power |    |

|     | consumption and energy comparisons. Encryption has $6.5\times$ energy               |    |

|     | reduction and decryption has $4033.0 \times$ energy reduction. (e) and (f)          |    |

|     | show EDP comparisons. Encryption has $462.7 \times$ savings and decryp-             |    |

|     | tion has $12,000,000 + \times$ savings. We can great performance boost,             |    |

|     | energy savings and EDP reductions of hardware implementation in                     |    |

|     | RSA decryption, since RSA private key length is much longer than                    |    |

|     | public key length.                                                                  | 73 |

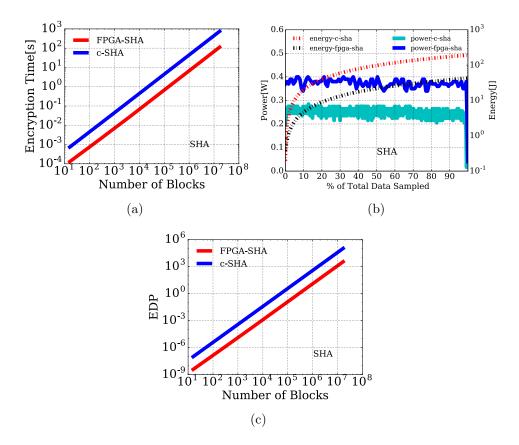

| 3.6 | Figures show the comparisons between C implementation (software),                   |    |

|     | and FPGA implementation (hardware) of SHA. We do hash ranging                       |    |

|     | from 16 blocks to $16^6$ blocks. (a) show time comparisons. (b) show                |    |

|     | power consumption and energy comparisons. (c) show EDP compar-                      |    |

|     | isons. We can see performance boost, energy savings and EDP reduc-                  |    |

|     | tions of hardware implementation in SHA. It shows $6.6 \times$ faster in time,      |    |

|     | $4.6 \times$ reduction in energy, and $30.3 \times$ savings in EDP                  | 74 |

82

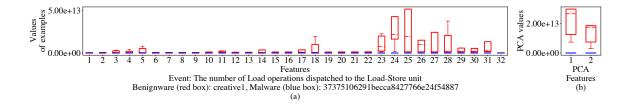

| 4.2 | X axis is the feature number and Y axis is the values of each example.               |    |

|-----|--------------------------------------------------------------------------------------|----|

|     | Red box corresponds to the malware and blue box corresponds to the                   |    |

|     | benignware. The dashed line is the mean of each distribution. The                    |    |

|     | boxes represent 25% $\sim$ 75% of the distributions. The whiskers (the               |    |

|     | short, horizontal lines outside the boxes) represent the confidence inter-           |    |

|     | val equivalent to $\mu \pm 3\sigma$ of Gaussian Distribution (0.3% $\sim$ 99.7%). We |    |

|     | measure The number of Load operations dispatched to the Load-Store                   |    |

|     | unit event 5 times in one benignware (creative 2 from Futuremark) and                |    |

|     | one malware. The distributions of the two subplots represent 5 exam-                 |    |

|     | ples in the experiments. (a) Distributions of sampled values before the              |    |

|     | reduction of dimensions: We cannot distinguish between the 5 malware                 |    |

|     | examples and the 5 benignware examples. (b) Distributions of sampled                 |    |

|     | values after the reduction of dimensions: We apply the reduction of di-              |    |

|     | mensions to examples in (a) to get examples in (b). We can separate                  |    |

|     | all the examples in (b) due to the gaps between values of malware and                |    |

|     | benignware in both features                                                          | 85 |

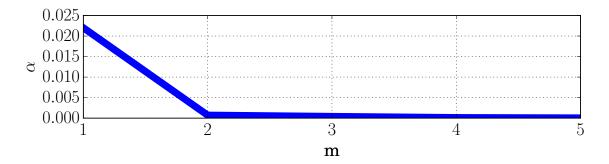

| 4.3 | Error Bound vs the Number of Eigenvetors Plot: when choosing dif-                    |    |

|     | ferent number of eigenvectors for reduction in dimensions, the error                 |    |

|     | bound $\alpha$ changes according to $m$ eigenvectors                                 | 89 |

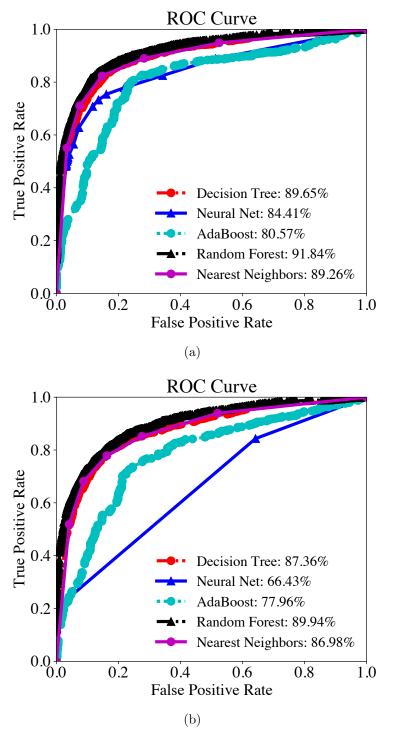

| 4.4 | Receiver Operating Characteristic (ROC) curve of 5 models. (a) The                   |    |

|     | AUC of DT, NN, AdaBoost, RF, and KNN using (TTA1) is $89.65\%$ ,                     |    |

|     | $84.41\%,\ 80.57\%,\ 91.84\%,\ and\ 89.26\%,\ respectively.$ (b) The AUC of          |    |

|     | DT, NN, AdaBoost, RF, and KNN using (TTA2) is $87.36\%$ , $66.43\%$ ,                |    |

|     | 77 96% 89 94% and 86 98% respectively                                                | 95 |

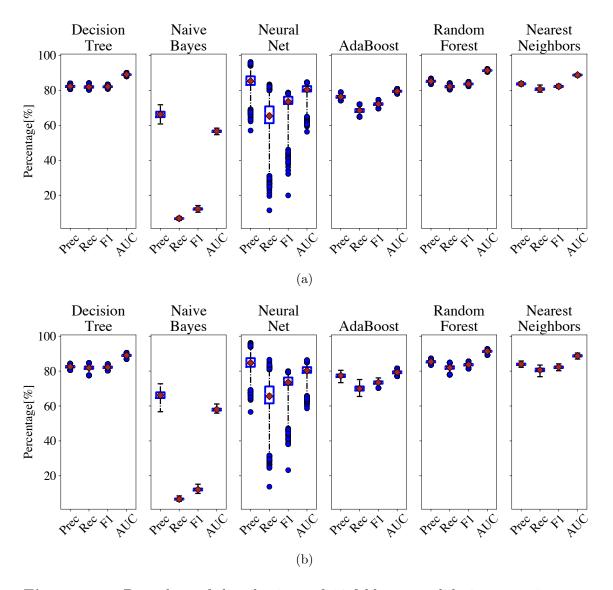

| 4.5 | Box plots of distributions of 10-fold cross-validation experiments using          |    |

|-----|-----------------------------------------------------------------------------------|----|

|     | (a) TTA1 and (b) TTA2. Red diamonds are means, and blue box                       |    |

|     | corresponds to cross-validation experiment results that lie between 25            |    |

|     | and 75 percentiles. The whiskers (the short, horizontal lines outside             |    |

|     | the blue box) represent confidence interval equivalent to $\mu \pm 3\sigma$ of a  |    |

|     | Gaussian Distribution. The blue dots are outliers that are outside the            |    |

|     | $\mu \pm 3\sigma$ regime. On the X-axis, Prec is precision, Rec is recall, and F1 |    |

|     | is F1 score. AUC is area under curve in ROC. These 10-fold cross-                 |    |

|     | validation experiments show that we cannot achieve $100\%$ malware                |    |

|     | detection accuracy                                                                | 99 |

## List of Abbreviations

RF .....

AEAD ..... Authenticated Encryption with Associated Data AES ...... Advanced Encryption Standard ASLR ..... Address-Space-Layout-Randomization Area Under Curve AUC ...... AXI ..... Advanced eXtensible Interface CDF ..... Cumulative Distribution Function CFG ..... Control Flow Graph CFI ..... Control Flow Integrity DBI ..... Dynamic Binary Instrumentation DEP ..... **Data Execution Prevention** DES ..... Data Encryption Standard DPA ..... Differential Power Analysis DT ..... Decision Tree ECB ..... Electronic Code Book mode Equivalence Classes ECs ..... GPP ..... General Purpose Processor GRUB ...... GNU GRand Unified Bootloader HPC ..... Hardware Performance Counter HPCs ..... Hardware Performance Counters Hardware Trojans HTs ...... IoTs ..... Internet of things IR ..... Intermediate Representations Instruction Translation Lookaside Buffer ITLB ...... JIT ...... Just-In-Time KNN ..... K Nearest Neighbors MLP ..... Multilayer Perceptron Neural Net NN ..... NSA ..... National Security Agency NX ..... Non-Executable memory PCA ..... Principal Component Analysis PDF ..... probability density function POSH ..... Posh open source hardware project POSIX ..... Portable Operating System Interface RE ..... Reverse Engineer

Random Forest

| RSA  | RivestShamirAdleman           |

|------|-------------------------------|

| Saas | software as a service         |

| SHA  | Secure Hash Algorithm         |

| SNR  | Signal to Noise Ratio         |

| SoC  | System on Chip                |

| SSH  | Secure SHell                  |

| TSVs | Through Silicon Vias          |

| TTA  | Training-and-Testing Approach |

| VLIW | Very Long Instruction Word    |

## Chapter 1

## Introduction

## 1.1 Background and Motivation

In the last few years, the security of the computing systems has become one of the main concerns in our lives. In 2016, identity theft from Equifax leaked the social security numbers of 300 million people (Equ, 2019); Spectre and Meltdown in 2017 affected all Intel and AMD processors to show the vulnerabilities in the architectural level (Mel, 2019); The leak of information from Facebook in 2018 directly affected millions of user profiles (Fac, 2019). Every year, there were a series of events in the security area involving millions or even billions of people. The previous incidents have shown that the security attacks have reached regimes which cannot be tackled by the existing defense system. Spectre and Meltdown exposed security flaws in computer architecture. The leaks of Facebook user profiles illustrated that the attacks on web applications can have social and political effects. In order to mitigate these failures in the existing systems, there is a pressing need to build secure systems on every layer of the computing systems, from circuits to web applications.

The root of the trust in the defense systems is the silicon running beneath all the software stacks. In general, the fabless design companies, such as Qualcomm, ARM and Broadcom trust the manufacturers of the ICs. The hardware companies fabricate their IC chips overseas, given that overseas IC manufacturers can support a range of technology nodes at much lower cost (AsC, 2019). However, this trust has been broken since the separation of design and manufacturing creates opportunities for hardware

attacks like Hardware Trojan (HT) insertion, IC overbuild, reverse engineering, side-channel analysis, and IC counterfeiting (Tehranipoor and Koushanfar, 2010). Among these attacks, HTs can cause significant economic and social damages. HTs are hardware blocks that are designed to perform malicious operations, e.g. leak secret keys, sabotage the functionality of the chip or launch privilege escalation attacks on the system. The HTs inserted during manufacturing have negligible overheads in performance and power consumption of the overall ICs (Nowroz et al., 2014; Yang et al., 2016). Besides, the attackers design HTs to evade being triggered during functional testing (Wei et al., 2012a). IC design companies need to either monitor the entire manufacturing process or apply costly reverse engineering techniques, including delayering the chip, imaging with Scanning Electron Microscope (SEM) etc. to detect HTs (Tehranipoor and Koushanfar, 2010; Karri et al., 2010). Both delayering and SEM are time-consuming and costly. Hence, there is a pressing need for a detection method, which can detect and locate HTs inserted during fabrication stage in a fast, accurate, and robust manner (Tsoutsos and Maniatakos, 2014).

At the architectural level, the security functionalities, e.g. cryptographic operations, ensure the confidentiality and integrity of the communications. The architectural solutions are deployed using dedicated Application Specific Integrated Circuit (ASIC) units embedded within the processor. For example ARM, Intel, and AVR, all provide hardware accelerated Advanced Encryption Standard (AES), crypto-engines in their ARMv8 (ARM, 2016), x86 (Int, 2016a), and Atmel (AVR, 2016) platforms respectively. These processors can leverage hardware primitives to perform cryptographic operations, such as Advanced Encryption Standard (AES), RivestShamirAdleman (RSA), and Secure Hash Algorithm (SHA). These operations are crucial to the Internet of things (IoT), which handle command and control signals at home and on the factory floors. IoTs are also low-power devices, which cannot easily be

replaced or modified, and are deployed for years at a time. Moreover, the longevity of these IoT devices often surpass the usage of cryptographic algorithm. Besides some IoT devices are deployed at dangerous places where they are dangerous and hard for humans to replace them. In order to achieve flexibility, high performance, and low power cryptographies, we need an energy-efficient configurable cryptography engine for IoT devices.

At the application level, the defense system must detect the malicious processes for protection. Researchers have utilized various analytical methodologies, such as signature analysis and dynamic analysis, for malware detection. All the previous methods have a substantial performance overhead. In order to reduce the overhead, the previous works propose the use of Hardware Performance Counters (HPCs) with machine learning models (Demme et al., 2013; Kazdagli et al., 2016; Wang et al., 2016; Ozsoy et al., 2015; Tang et al., 2014; Khasawneh et al., 2015; Khasawneh et al., 2017; Singh et al., 2017). HPCs are hardware blocks that count micro-architectural events. However, it is counter-intuitive that the high-level program behaviors can manifest themselves in low-level statics. In order to show the feasibility of HPC malware detection, the researchers must evaluate HPC malware detection rigorously before the real-life deployments.

In this work, we construct the solutions towards the threat models on each computing layer, hardware, architectural and software layer. We present the thesis statement as following:

Constructing a defense mechanism on the same computing layer as a security threat can protect the computing system effectively and efficiently.

Therefore, we propose a multi-level approach to securing computing systems. Our approaches include the following solutions for securing computing systems:

- HT Detection using backside imaging: We propose a novel optical method, where we image the integrated circuit chip from the backside without powering it up or delayering it (Chapter 2). Using our method, any replacements, modifications or re-arrangements of gates to add HTs can be easily detected through comparisons between the simulated optical response and backside imaged measurements. We introduce the idea of a noise-based detection method as our testing method to have higher HT detection rates in different testbenches. To further improve the robustness of our method, we strategically place high reflectance fill cells in the designs. Our imaging method provides high-resolution, non-destructive and rapid means to detect HTs inserted during fabrication. We evaluate our approach using various hardware blocks where the HTs can occupy less than 0.1% of the total area or consist of fewer than 3 gates. In addition, we analyze our method with different magnitudes of noise, process variations, detection window sizes, and resolutions. To increase the difference in the reflection among various gates, we also engineer nano-antenna structures into the gate pairs. These nano-antennas are unique to illumination polarizations, frequencies and angles. By implementing the nano-antennas, we can improve the reflectance signature by 300%.

- Flexible Hardware Implementations of Cryptographies: We propose to use FPGA as the reconfigurable substrate for cryptographic operations in IoT devices (Chapter 3). We demonstrate our proposed approach on the Zedboard platform, which has two ARM cores and a Zynq FPGA. The implemented cryptographic algorithms include symmetric cryptography, asymmetric cryptography, and secure hash functions. We also integrate our cryptographic engines in the SSL library to inherit the software support for block cipher modes implemented by OpenSSL. Our approach shows that the FPGA-based recon-

figurable cryptographic components consume  $1.8 \times \sim 4033 \times$  less energy and run  $1.6 \times \sim 2983 \times$  faster than software implementation. At the same time, the FPGA implementation of cryptographic operations are more flexible compared to custom hardware implementations of cryptographic components.

• Malware Detection using Hardware Performance Counters with machine learning: We identify the prevalent unrealistic assumptions and the insufficient analysis used in prior works that leverage HPCs for malware detection (Chapter 4). We perform thorough experiments with a program count that exceeds prior works (Demme et al., 2013; Kazdagli et al., 2016; Wang et al., 2016; Tang et al., 2014; Singh et al., 2017) by a factor of  $2 \times \sim 3 \times$ , and the number of experiments in cross-validations that are 3 orders of magnitude more than previous works. We divide the train-and-test dataset similar to what prior works have done, as well as, in a realistic setting where testing programs are not in the training programs. We compare the effects of this choice on the quality of the machine learning models. Finally, to facilitate reproducibility, and enable future researchers to easily compare their experiments with ours, we make all code, data, and results of our project publicly available under an open-source license: https://github.com/bu-icsg/Hardware\_Performance\_Counters\_Can\_Detect\_Malware\_Myth\_or\_Fact

### 1.2 Related Work

In this work, we present the works related to HT detection, cryptographic engines, malware detection using HPCs with machine learning and CFI hardware enforcement.

### 1.2.1 HT Detection using Backside Imaging

Three different HT detection approaches have been proposed for preventing HT insertion and detecting any inserted HT: protective designs before fabrication, HT detection after fabrication, and side channel detection method. A number of prefabrication protection designs have been proposed on both circuits and architecture levels. At the circuit level, the separation of fabrication, gate level obfuscations, and limitations of gate usage have been proposed to protection designs. Separation of fabrication (Vaidyanathan et al., 2014a; Vaidyanathan et al., 2014b; Valamehr et al., 2013) proposes that the device layer of IC is fabricated by one trusted vendor, while other layers are fabricated by untrusted vendors at a lower cost. The trusted vendor use high cost Through Silicon Vias (TSVs) to connect different layers of logic. HAR-POON (Chakraborty and Bhunia, 2009) provides netlist-level obfuscation, which can be integrated into the synthesis of Soc designs. Other techniques, (Roy et al., 2008; Baumgarten et al., 2010) and (Xiao et al., 2014; Xiao et al., 2015) also provide protective designs by replacing the filler cells with functional cells. That way there are no empty spaces for inserting HTs. Bao et al. proposed to both prevent and detect HTs in (Bao et al., 2015), by limiting the useable gate types in the standard library. All these proposed techniques either use a high-cost method or sacrifice area in order to protect designs from HTs. On the architecture level, logic state scrambling, power signatures in potential tampered logics, and circuitry encoding are the main techniques in protecting designs from HTs. ODETTE (Banga and Hsiao, 2011) protects the circuits from HTs by increasing the number and variations of the design. VITAMIN (Banga and Hsiao, 2009b) utilizes an inverted voltage scheme that aims to activate some targeted Trojans with a higher triggering rate. The power consumption of HTs will become prominent in the power analysis. Linear Complement Dual Codes (Ngo et al., 2015) is designed to encode the instructions inside the circuitry and to be resistant to error injection and side channel analysis. These methods potentially increase the complexity of logic designs, and they also increase the power consumptions of the overall system.

Post-fabrication detection includes reverse engineer (RE), timing and power analysis, and data monitoring during runtime. The generic detection method after fabrications is to reverse engineering the fabricated ICs. Scanning Electron Microscope (SEM) and FIB (Focused Ion Beam) (Tehranipoor and Koushanfar, 2010) have been proposed for HT Detection. However, the approaches are high in cost and low in speed. The process of RE the fabricated chip is only affordable to large semiconductor companies (Tehranipoor and Koushanfar, 2010; Karri et al., 2010). FANCI (Waksman et al., 2013) and FIGHT (Sullivan et al., 2014), flag possible HT wires, which reduces the complexity in reverse engineering. To detect HTs without reverse engineering the IC chips timing analyses and power analyses methods have been proposed. Timingbased analysis (Li and Lach, 2008; Jin and Makris, 2008; Exurville et al., 2015) detects the delay changes in the circuitry for HT Detection. Dynamic power detection, such as the sustained vector technique, measures the dynamic power consumption difference in the circuitry and identifies the gates that may contain Trojans (Banga and Hsiao, 2009a; Salmani et al., 2012; Wilcox et al., 2015). Such time and power based analysis (Potkonjak et al., 2009a; Wei et al., 2010; Wei and Potkonjak, 2012; Wei et al., 2012b; Rad et al., 2008; Alkabani and Koushanfar, 2009; Potkonjak et al., 2009b; Wei and Potkonjak, 2012) are not suitable at newer technology nodes, because the impact of process variations is larger than the impact by the HTs on power and delays. This introduces overhead in the performance in order to detect HTs.

Compared to electrical methods, side channel detection utilizes physical properties of ICs instead of electrical properties, which can help detect HTs that can hide from electrical tests. Emission measurements (Song et al., 2011; Stellari et al., 2014)

and thermal analysis (Nowroz et al., 2014; Forte et al., 2013) are good examples of side channel analysis. Emission measurements utilize the long wavelength imaging techniques resulting the low-resolution imaging. Thermal analysis requires the powering on the logic, which introduces the engineering of testing infrastructures. All these techniques are either not as fast, easy or high in resolution as our technique.

### 1.2.2 Cryptographic Engines for IoT Devices

Many previous works have implemented various algorithms on the FPGA to show the performance improvements, energy savings in these FPGA implementations. The FPGA implementation of AES was first shown to have benefits on both performance improvements and energy savings in 2004 (Rouvroy et al., 2004). The performance reached a speed of 204Mbps stream in AES encryption. Since then, FPGAs were explored as a potential solution to cryptographic applications for low power devices. Good et al. proposed a design of AES, which use only on 8-bit data-path in all the operations in AES (Good and Benaissa, 2006). This design made the entire AES fit on small programmable areas. Hamalainen et al. presented an upgraded version with the cost of using 3.1k gates (Hamalainen et al., 2006). With the increasing area of FPGA, more and more resources could be used for cryptographic designs. One 128-bit AES block operation consists of key expansions and SubBytes operations. Key expansions increase the key length for further data processing in SubBytes operations. SubBytes is a 16-by-16 matrix operated with a minimum unit of 8-bit for permutations and substitutions during AES encryption/decryption. SubBytes operations consist of substitutions of cells, shifts of rows, a mix of columns and exclusive or with the keys, which are operations to increase the pseudorandomness of the output text. AES encryption/decryption usually consists of  $10 \sim 14$  rounds of SubBytes operations according to the required security level. With fully integrated SubBytes operations in hardware, AES has much higher efficiency, as AES needs fewer cycles to finish the operations. Bulens et al. first put one full round of SubBytes operations in AES on FPGA in 2008 (Bulens et al., 2008). With pipelined designs, the plain text can be continuously streamed into the cryptographic units for encryption/decryption to achieve high throughput. Repetitive use of same hardware block cannot have the same high performance as pipelined design do since inputs in each round depend on results of previous round operations. Good et al. showed the designs from the fastest to the smallest, which can provide different design points on different hardware platforms, in order to achieve a trade-off between speed and area (Good and Benaissa, 2005). It achieved the speed of 358Mbps compared to encryption/decryption speed of 397Mbps in our implementation without streaming throughput. Today, modern FPGAs have enough programmable logic that can fit the expansion of 10 to 14 rounds of SubBytes operations. Hoang et al. showed a fast implementation of AES with a key size of 128-bit, with look-up table of SubByteses (Hoang et al., 2012). There are also partial and dynamic reconfigurable implementations for more flexible solutions on FPGA (Granado-Criado et al., 2010). As partial configurations are designed for high-end FPGA applications, low-energy FPGA has not yet widely adopted the partial configurations for their applications. Side channel attacks use power, time or other physical properties to break cryptographic algorithms. Once discovered, it is possible to prevent a given side channel attack by modifying the implementation of cryptographic algorithms. Robust designs, such as (Oswald et al., 2005; Shah et al., 2010), are resistant to Differential Power Analysis (DPA) leaking AES keys in their implementation. However, robustness and DPA resistant designs come at a higher cost in performance or energy consumption. Other cryptographic algorithms, such as Hummingbird (Fan et al., 2010) and Whirlpool (Pramstaller et al., 2006), have also been implemented on FPGA. Recent works have shown that FPGA can be an ideal solution for modern cryptographic computation. Saarinen et al. implemented Authenticated Encryption with Associated Data (AEAD), AES-GCM on Zedboard (Saarinen, 2014). Saarinen et al. also showed one variant implementation of Whirlpool (Saarinen and Brumley, 2014). These works contain detailed explanations of implementation and performance analysis, but lack of power and energy analysis and multi-crypto-engines implementation.

## 1.2.3 Malware Detection using Hardware Performance Counters with Machine Learning

Malware detection is the process of detecting malicious programs. Many previous works commonly utilize *sub-semantic features* in malware detection (Demme et al., 2013; Kazdagli et al., 2016; Wang et al., 2016; Ozsoy et al., 2015; Tang et al., 2014; Khasawneh et al., 2015; Khasawneh et al., 2017; Singh et al., 2017). Ozsoy et al. defined the term *sub-semantic features* as "micro-architectural information about an executing program that does not require modeling or detecting program semantics" (Ozsoy et al., 2015). These sub-semantic features are often aggregated in the HPCs to record the statistics of low-level events. All these previous works have several drawbacks to various extent. We categorize the drawbacks that we observed in the following classes.

- I Dynamic Binary Instrumentation (DBI)

- II Virtual Machines (VMs)

- III Division of Data By Traces (TTA1 in § 4.4.3)

- IV No Cross-Validations or Insufficient Validations

- V Few Data Samples

Besides HPCs, sub-semantic features can be extracted with dynamic binary instrumentation (DBI) tools such as Intel's Pin (Patil et al., 2004; Luk et al., 2005), QEMU (Bellard, 2005), Valgrind (Nethercote and Seward, 2007), or DynamoRIO (Dyn, 2017). Khasawneh, Ozsoy et al. use Pin to monitor the instructions executed on vir-

tual machines in their experimental setup (Ozsoy et al., 2015; Khasawneh et al., 2015; Khasawneh et al., 2017). Though DBI can extract sub-semantic features that are not available from HPCs, DBI introduces a substantial amount of performance overhead and is thus not suited to run in an *always-on*, online protection setting, which is the default use-case for current anti-malware suites. We denote the drawbacks of DBI as **Drawback I** in Table 1.1.

While DBI is not feasible in online detection systems, other methods in sampling HPCs can incur inaccurate measurements. A plethora of previous works that uses HPCs for malware detections run the evaluated programs on VMs (Demme et al., 2013; Ozsoy et al., 2015; Khasawneh et al., 2015; Khasawneh et al., 2017; Singh et al., 2017). While VMs provide significant benefits to analyze unknown programs (e.g., strong isolation guarantees), HPCs are limited and shared resource between the host and all VMs. Thus, virtualizing HPCs is a challenge in itself (Serebrin and Hecht, 2011). The measured HPC values obtained in VM are substantially different from HPC values obtained from the bare-metal environment that real-life users have. To make matters worse, evasive malware can detect whether it is running in a VM and ceases to exhibit malicious behavior (Kirat et al. (Kirat et al., 2014)). These observations motivate our experimental setup (§4.3) to run all experiments on bare-metal systems. We label the use of VM in the experimental setups as **Drawback II** in Table 1.1.

Due to inaccurate HPC measurements (Weaver and McKee, 2008), previous works (Demme et al., 2013; Kazdagli et al., 2016; Wang et al., 2016; Tang et al., 2014) choose to maximize the measuring granularity by using HPCs without time-multiplexing. Recall that as modern CPUs only have 6 (AMD) or 4 (Intel) registers for HPCs, malware detection methods must select the events from more than 100 available micro-architectural events (130 in AMD Bulldozer and 196 in Intel Skylake). Previous

|                                                 | Tool Choice                   | Experimental                 | Setups             | Event Choice                   | 4.4.3) Data                                             | Division                                  | Cross                            |                                                     |                          |                                 | Machine<br>Learning<br>Models |    |     |           |                                         | # of Programs                         | Opensource                          |                                        |

|-------------------------------------------------|-------------------------------|------------------------------|--------------------|--------------------------------|---------------------------------------------------------|-------------------------------------------|----------------------------------|-----------------------------------------------------|--------------------------|---------------------------------|-------------------------------|----|-----|-----------|-----------------------------------------|---------------------------------------|-------------------------------------|----------------------------------------|

| Paper                                           | Drawback I: DBI (Pin or QEMU) | Drawback II: Virtual Machine | Bare-metal Machine | Quantative Selection of Events | <b>Drawback III</b> : Data Divided By Traces (TTA1 in § | Data Divided By Samples (TTA2 in § 4.4.3) | Drawback IV: No Cross-validation | <b>Drawback IV</b> : $60 - 20 - 20\%$ Data Division | 10-fold Cross-validation | 1,000 10-fold Cross-validations | DT                            | RF | KNN | NN        | Ensemble Model (a collection of models) | Drawback V: Fewer than 1,000 programs | Release of Data and Codes to Public | Number of Drawbacks                    |

| (Demme et al., 2013)<br>(Kazdagli et al., 2016) | <b>♦</b>                      | <b>♦</b>                     | •                  | <b>♦</b>                       | •                                                       | <b>♦</b>                                  | •                                | <b>♦</b>                                            | <b>♦</b>                 | <b>♦</b>                        | •                             | •  | •   | •         | <b>♦</b>                                | •                                     | <b>♦</b>                            | $\begin{bmatrix} 3 \\ 2 \end{bmatrix}$ |

|                                                 | <b>♦</b>                      | <b>\Q</b>                    | •                  | <b>♦</b>                       | •                                                       | •                                         | <b>♦</b>                         |                                                     | ^                        | ♦                               | •                             | •  | •   | ♦         | ♦                                       | •                                     | ♦                                   | $\frac{2}{4}$                          |

| (Wang et al., 2016)<br>(Tang et al., 2014)      | ♦                             | •                            | ♦                  | •                              | •                                                       | ♦                                         | •                                | ♦                                                   | ♦                        | ♦                               | ♦                             | ♦  | ♦   | ♦         | ♦                                       | •                                     | ♦                                   | 3                                      |

| (Singh et al., 2017)                            | ♦                             | •                            | <b>\langle</b>     | •                              | •                                                       | <b>⋄</b>                                  | <b>♦</b>                         | •                                                   | ♦                        | <b>♦</b>                        | •                             | ♦  |     | ◇         |                                         | •                                     | $\diamond$                          | $\frac{3}{4}$                          |

| (Ozsoy et al., 2015)                            | •                             | •                            |                    | <b>⋄</b>                       | $\Diamond$                                              | •                                         | <b>\lambda</b>                   | •                                                   |                          |                                 | <b>♦</b>                      |    |     | •         |                                         | <b>♦</b>                              | $\diamond$                          | 2                                      |

| (Khasawneh et al., 2015)                        | •                             | •                            | <b> </b>           | <b>♦</b>                       | <b>→</b>                                                | •                                         | <b>♦</b>                         | •                                                   | ♦                        | <b>♦</b>                        | <b>→</b>                      | •  |     | <b>\$</b> | •                                       | <b>♦</b>                              | <b>♦</b>                            | 3                                      |

| (Khasawneh et al., 2017)                        | •                             | •                            | <b> </b>           | <b>♦</b>                       | <b>♦</b>                                                | •                                         | <b>♦</b>                         | •                                                   | <b>♦</b>                 | <b>♦</b>                        | <b>♦</b>                      | •  |     | <b>♦</b>  | •                                       | <b>♦</b>                              | <b>♦</b>                            | 3                                      |

| *                                               | <b>♦</b>                      | <b>♦</b>                     | •                  | •                              | •                                                       | •                                         | <b>♦</b>                         | <b>⋄</b>                                            | <b>♦</b>                 | •                               | •                             | •  | •   | •         | •                                       |                                       | Ť                                   | -                                      |

**Table 1.1:** Comparison between various previous works: Rows are various works in HPC-based malware detection and columns are design choices. The alternative shaded and white background represents different categories of tool/setup/model in malware detection using HPCs. Red texts highlight drawbacks, and black texts express the suggested tool/setup/model from this work. Solid dots ( $\bullet$ ) indicate the use of that tool/setup/model (column) by the reference (row), and hollow dimonds ( $\diamond$ ) indicate the non-use of that tool/setup/model by the reference. Star ( $\star$ ) is our work. Our work avoids the drawbacks discussed in the table, and quantitatively analyzes how these drawbacks lead to the conclusion that HPCs can reliably detect hardware.

works (Demme et al., 2013; Kazdagli et al., 2016; Ozsoy et al., 2015; Khasawneh et al., 2015; Khasawneh et al., 2017) have not provided a numerical analysis of how microarchitectural events are selected. After the selection of events, we need to track these events and transform the measured HPC values to examples in machine learning models, i.e. feature extraction. Dividing examples into training and testing datasets for machine learning models are training-and-testing split. Previous works (Demme et al., 2013; Kazdagli et al., 2016; Wang et al., 2016; Singh et al., 2017) have training-and-testing split based on the examples (TTA1 in § 4.4.3) that the testing dataset can have the same examples produced by programs in the training dataset. However, in real life, it is unlikely that the offline training dataset can include all the malware that a user might encounter. We mark the use of data division based on examples as Drawback III in Table 1.1.

We observe that there is no cross-validation in some of the previous works (Demme et al., 2013; Wang et al., 2016; Tang et al., 2014), while other works (Ozsoy et al., 2015; Khasawneh et al., 2015; Khasawneh et al., 2017; Singh et al., 2017) present insufficient cross-validation, i.e. not every example in the dataset is validated. None of these works report standard deviations of detection rates with cross-validations. Without a substantial amount of cross-validation, we cannot assert the reproducibility of detection rates, since a model can have its high detection rates with specific training and testing datasets. We refer to no cross-validation or insufficient validations as **Drawback IV** in Table 1.1.

Previous works reported their results with double decimal precision (Demme et al., 2013). However, double decimal precision require at least 100 experiments in testing. With 10-fold cross-validation in the experiments, the total number of programs (benignware and malware) should be more than 1,000 programs. Thus, at least 1,000 programs are required to evaluate the machine learning models within numer-

ical rounding error of less than 1%. There are several works that use fewer than 1,000 programs leading to over-generalization (training and testing with insufficient cross-validation), or over-interpretation of the results (comparisons beyond rounding errors) (Demme et al., 2013; Kazdagli et al., 2016; Wang et al., 2016; Tang et al., 2014; Singh et al., 2017). This insufficient number of programs in the experiments is **Drawback V** in Table 1.1.

In addition to the drawbacks of the previous works, we found that there is no public access to their data or codes, which makes it hard to perform a direct comparison and examinations of the methods applied in these works.

We present all the tools/setups/models in various previous works in Table 1.1. In Table 1.1, rows are various works in HPC-based malware detection and columns are design choices of the tools/setups/models. The alternative shaded and white background represents different categories of tool/setup/model in malware detection using HPCs. Red texts highlight drawbacks and black texts express the suggested tool/setup/model from this work. Solid dots ( $\bullet$ ) indicate the use of that tool/setup/model (column) by the reference (row), and hollow diamonds ( $\diamond$ ) indicate the non-use of that tool/setup/model by the reference. Star ( $\star$ ) is our work. The last column counts the drawbacks of the corresponding work. Table 1.1 shows that there are at least 2 drawbacks in each work.

# 1.3 Completed Research

The following work was completed as part of my Ph.D. Program:

• Hardware Trojan Detection using Backside Optical Imaging: In this work, we proposed to use backside optical imaging for HT detection. We first engineered fill cells to have maximum reflectance compared to standard cells. These highly reflective cells formed watermark. Any shifts, modifications to

these cells could be detected using backside imaging. By mapping the gate response to the locations and orientations of all the gates in the layout, we generated an optical response of the entire chip as the "golden response". We applied correlation between imaged results and generated "golden reference" to determine whether the chip has HTs (Chapter 2).

We then extended our work to create a library of responses of all the cells in the standard cell library. We illuminated multiple locations on each gate according to the size of the gates to have a unique response for each gate. We improved the accuracy and robustness of our method by using noise-based detection method in the comparisons between "golden reference" and imaged results. We also did process variation analysis and optimized the detection method.

Our approach does not require costly devices as low throughput techniques, such as delayering the metal layers and SEM. Compared to the traditional electrical detection method, our method images the layouts of ICs, which does not depend on the tests that are able to trigger the HTs. The ICs under test do not need to be powered up or calibrate for testing environments, such as thermal detection method. At the same time, backside imaging presents high-resistance against process variations during manufacturing. The infrared light imaging produces images with a resolution at the gate level. No previous imaging methods have been able to achieve.

• High-Performance Low Energy Implementation of Cryptographic Algorithms on a Programmable SoC for IoT Devices: In this work, we implemented various kinds of cryptographies on a programmable SoC for IoT devices. We measured the performance, power and energy consumption, and reconfigurability of our implementation. We implemented the same cryptographic algorithms in software and compared performance, power and energy to evaluate

the improvements achievable through hardware implementations. Our implementation showed that the Zedboard platform provided high performance, low energy consumption and reconfigurability for IoT devices (Chapter 3).

Our proposed FPGA implementation can replace the implementations in the existing library (OpenSSL), which enables performance boost and energy savings in various block cipher modes.

• Malware Detection using Hardware Performance Counters with Machine Learning: We identify the prevalent unrealistic assumptions and the insufficient analysis used in prior works that leverage HPCs for malware detection (Chapter 4). We perform thorough experiments with a program count that exceeds prior works (Demme et al., 2013; Kazdagli et al., 2016; Wang et al., 2016; Tang et al., 2014; Singh et al., 2017) by a factor of  $2 \times \sim 3 \times$ , and the number of experiments in cross-validations that is 3 orders of magnitude more than previous works. We harvest the HPC traces from 1,924 programs, 962 benignware and 962 malware, on our experimental setups. We achieve an F1score (a metric of detection rates) of 83.39%, 84.84%, 83.59%, 75.01%, 78.75%, and 14.32% for Decision Tree (DT), Random Forest (RF), K Nearest Neighbors (KNN), Adaboost, Neural Net (NN), and Naive Bayes, respectively. We crossvalidate our models 1,000 times and the F1-score of models in DT, RF, KNN, Adaboost, NN, and Naive Bayes is 80.22\%, 81.29\%, 80.22\%, 70.32\%, 35.66\%, and 9.903\%, respectively. To show how fragile the HPC malware detection system is, we show that one benignware (Notepad++) infused with malware (ransomware) cannot be detected by HPC-based malware detection. To ease the reproducibility and advance the community's efforts to assess the utility of HPC-based malware detection, we release all the code and data produced for this work under an open-source license.

# Chapter 2

# Hardware Trojan Detection Using Backside Imaging

# 2.1 Introduction

Integrated circuits (ICs) are the root of the trust in computing systems. Secure mechanisms rely on the trust on the hardware underneath software stacks. However, the trust is broken due to fragmented supply chain of IC manufacturing. The large demands for IC chips has led to the globalization of the IC chip supply chain. Over the past two decades, IC design and manufacturing has become increasingly distributed across the world (Tehranipoor and Koushanfar, 2010). The standard IC chip production process consists of specification, design, fabrication, testing and packaging phases (Dar, 2019; Chakraborty et al., 2009; Karri et al., 2010). Many U.S. companies still design their IC chips locally. However, given that overseas manufacturing can support a range of technology nodes at a significantly lower cost, these companies prefer to fabricate their IC chips overseas.

Highly fragmented and distributed production brings efficiency and productivity to IC design and fabrication (The, 2019). However, given the pervasive use of the IC chips in both commercial and military domains, it is mandatory to ensure that the security of these chips has not been compromised. During the different phases of IC production, the ICs face threats from HTs (Karri et al., 2010; Tehranipoor and Koushanfar, 2010; Love et al., 2012; Waksman and Sethumadhavan, 2011; Hicks et al.,

2010), IP privacy (Roy et al., 2008), IC chip overbuilding (Chakraborty and Bhunia, 2009), reverse engineering (Torrance and James, 2011; electroiq.com, 2019; DARPA, 2019; iPh, 2019; How, 2019; Rev, 2019), side-channel analysis (Kocher et al., 1999; Schlösser et al., 2012; Koeune and Standaert, 2005; Koeune and Standaert, 2005; Genkin et al., 2014; Rohatgi, 2009) and IC counterfeiting (Rostami et al., 2014). HTs are malicious modifications or insertions of unwanted circuitry into the chip designs to sabotage the functionality or leak secret information. IP privacy discloses the intellectual properties of IC designs and causes economic damages to the IC company. Foundries can overbuild ICs and sell them to make illegal profits. Reverse engineering recovers designs of the chips to steal intellectual property. Side channel analysis focuses on using physical properties other than electrical signals on the chip to extract secret information from ICs. IC counterfeiting refers to fabricating unqualified products but labeling them as products from other companies, which causes indirect loss to companies that originally design the chip. Among all these threats, HT attacks are the worst attacks in hardware security. Therefore, our approach targets detecting the HTs inserted during fabrication.

The HT attacks can directly cause information leakage, system compromise and failures. HTs can control, modify, disable or monitor the IC chips (Rostami et al., 2014). Common HT insertion approaches are insertions of the malicious IP cores, design modifications, and layout modifications during the fabrication phase (Rostami et al., 2014). We can detect the HTs inserted using the first two approaches with functional verifications at different stages of the IC chip design process. In the third type of HT insertion, the attackers reverse engineer the physical layout and modify the design during manufacturing. The HTs inserted during fabrication have a very small impact on the delay and power consumption of the overall IC chip. Besides, HTs inserted during fabrication are designed to have an extremely low triggering rate

to hide them from standard tests. Unless manufacturing is closely monitored, the IC design company needs to use expensive reverse engineering techniques like delayering the chip, SEM imaging, and etc. to check for HTs. Hence, there is a pressing need for a new detection method, which can detect and locate HTs inserted during fabrication in a fast, accurate, and robust manner (Tsoutsos and Maniatakos, 2014).

We propose a novel optical imaging method that can rapidly and accurately detect HTs inserted during the fabrication. In our proposed approach, we use backside imaging to detect HTs inserted during the fabrication. We measure the optical responses from post-fabricated ICs, and compare the results to the responses from FDTD simulations performed on the chip. We can detect any compromises to the chip by identifying differences between the generated responses and the measured results. To this end, we have completed the following work:

# • Backside Imaging using near-IR light

We propose a new approach to generate a backside image of an IC chip, which we call the "golden reference", using the detailed physical layout of the IC chip and FDTD simulations of individual standard cells. We model the process of backside imaging of the IC chips by FDTD simulations. We compose the reference responses by mapping individual gate FDTD responses to the locations of standard cells and interpolate the response image. Any inconsistencies between measurements and reference response correspond to changes in the designs.

#### • Noise-based Detection Method

We implement a noise-based detection method that compares the imaged data and "golden reference". This method performs better than our previously proposed correlation-based detection method. The noise -based detection exhibits robustness against noise, and is effective across different testbenches.

## • Engineering High Reflectance Fill Cells

We engineer fill cells as high reflectance cells and strategically insert them before placing the cells of the digital designs to increase the contrast of imaging responses. We demonstrate that the insertion of extra fill cells improves the HT detection accuracy against noise.

#### • Evaluations using Various Hardware Blocks

We use standard *Cadence* tool flows in *Nangate* 45nm technology to synthesize and place & route the circuits. The area of inserted HT vary from 0.1% to 12% of the total chip sizes. We use our method to detect the HTs in these testbenches under different signal to noise ratios. We also analyze the effects of process variations, different resolutions in imaging, and different detection window frame sizes on detection rates with different noise levels.

#### 2.2 Threat Model