## BOSTON UNIVERSITY COLLEGE OF ENGINEERING

Dissertation

# DESIGNING ENERGY-EFFICIENT COMPUTING SYSTEMS USING EQUALIZATION AND MACHINE LEARNING

by

## ZAFAR TAKHIROV

Specialist, Russian-Tajik (Slavonic) University, 2008 M.S., Boston University, 2012

Submitted in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

2018

© 2018 by ZAFAR TAKHIROV All rights reserved

## Approved by

First Reader

Ajay J. Joshi, PhD Associate Professor of Electrical and Computer Engineering

Second Reader

Venkatesh Saligrama, PhD Professor of Electrical and Computer Engineering Professor of Systems Engineering Professor of Computer Science

Third Reader

Ayse K. Coskun, PhD Associate Professor of Electrical and Computer Engineering

Fourth Reader

Joseph Wang, PhD Research Scientist, Amazon.com, Inc.

Fifth Reader

Michel Kinsy, PhD Assistant Professor of Electrical and Computer Engineering

Duo parabolas me servavit: Per aspera ad astra, et... Lingua latina non verpa canina...

### Acknowledgments

First and foremost, I am endlessly thankful to two people without whom this work would not have been possible – my advisor, professor Ajay Joshi, and my lovely wife, Alice. Their help and support, despite my constant resistance, was the only thing that brought me where I am right now. Ajay's guidance and help was crucial in every aspect of my academic work, while Alice's unconditional support will be the sole reason I managed to survive this confusing, head-bashing, excruciating path.

I would like to express gratitude to my parents, Gulnara and Mahmadzahir, as they were the ones who encouraged me to take on this path, and were very helpful both morally and financially throughout my life. Both of my brothers, Akbar and Askar, were there when I needed them the most, and thus should always be thanked for believing in me. On the same note, I would like to thank the Department of Electrical and Computer Engineering of Boston University, and especially the administration and the advisors of the Late Entry Accelerated Program (LEAP) for providing me with an opportunity to achieve something I never hoped to engage.

I would also like to use these pages to mention the people I collaborated with academically and professionally. It goes without saying that without numerous discussions with Joe Wang and Marcia S. Louis, the later part of this work would have been dull and unimpressive. My only regret is that I didn't meet them earlier in my career. Also, Yuhong Huang was incredibly supportive both as a manager and as a friend during my time at Analog Devices, Inc. She was an incredible mentor, and she is continuing being a great family friend. I would like to mention my colleagues in the infamous PHO 340 who I spent great amount of time with: discussing completely irrelevant topics (Boyou), being roommates and three-am-walk-home buddies (Chao), partying like it was the last thing in our life (Mahmoud), arguing till our noses started bleeding (Schuyler), learning how to curse in Chinese (Yenai), playing chess (Saiful - I will still always win), and of course I would not forget Leila for keeping my awesomeness in check and bringing me down to earth. The same goes to the rest of the PHO 340, where I spent the last several years and made a lot of friends. This goes to all members of the PEAC and CAAD labs without exception.

Many more people played an indirect, but crucial role during my work. In particular without the help of Aksana, Sveta, Leo, and Vlad I would probably spend a lot more nights sleeping on Fenway park benches. Ato and his team were the motivation and inspiration for all those sleepless nights me working with them, and still having the energy to work on more projects in the morning.

## DESIGNING ENERGY-EFFICIENT COMPUTING SYSTEMS USING EQUALIZATION AND MACHINE LEARNING

### ZAFAR TAKHIROV

Boston University, College of Engineering, 2018

Major Professor: Ajay Joshi, PhD Associate Professor of Electrical and Computer Engineering

### ABSTRACT

As technology scaling slows down in the nanometer CMOS regime and mobile computing becomes more ubiquitous, designing energy-efficient hardware for mobile systems is becoming increasingly critical and challenging. Although various approaches like near-threshold computing (NTC), aggressive voltage scaling with shadow latches, etc. have been proposed to get the most out of limited battery life, there is still no "silver bullet" to increasing power-performance demands of the mobile systems. Moreover, given that a mobile system could operate in a variety of environmental conditions, like different temperatures, have varying performance requirements, etc., there is a growing need for designing tunable/reconfigurable systems in order to achieve energy-efficient operation. In this work we propose to address the energyefficiency problem of mobile systems using two different approaches: circuit tunability and distributed adaptive algorithms.

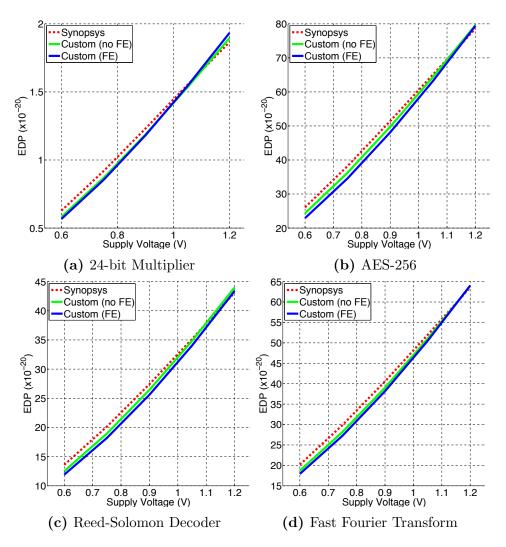

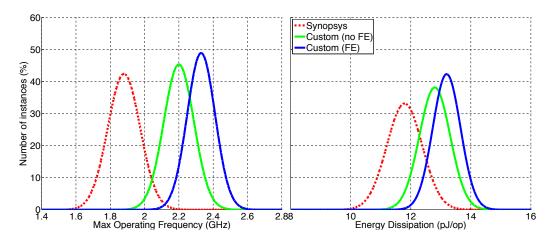

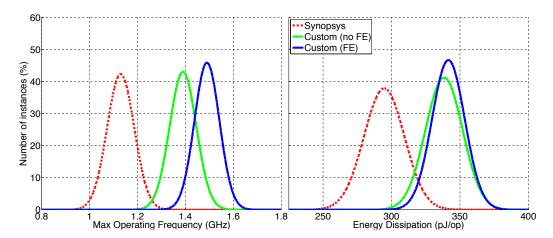

Inspired by the communication systems, we developed feedback equalization based digital logic that changes the threshold of its gates based on the input pattern. We showed that feedback equalization in static complementary CMOS logic enabled up to 20% reduction in energy dissipation while maintaining the performance metrics. We also achieved 30% reduction in energy dissipation for pass-transistor digital logic (PTL) with equalization while maintaining performance. In addition, we proposed a mechanism that leverages feedback equalization techniques to achieve near optimal operation of static complementary CMOS logic blocks over the entire voltage range from near threshold supply voltage to nominal supply voltage. Using energy-delay product (EDP) as a metric we analyzed the use of the feedback equalizer as part of various sequential computational blocks. Our analysis shows that for near-threshold voltage operation, when equalization was used, we can improve the operating frequency by up to 30%, while the energy increase was less than 15%, with an overall EDP reduction of  $\approx 10\%$ . We also observe an EDP reduction of close to 5% across entire above-threshold voltage range.

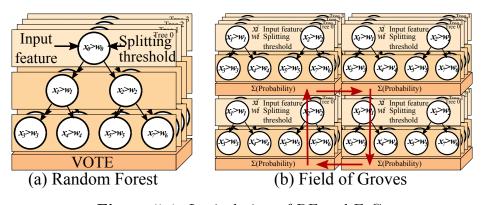

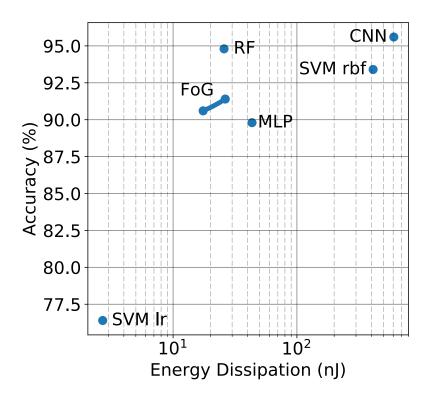

On the distributed adaptive algorithm front, we explored energy-efficient hardware implementation of machine learning algorithms. We proposed an adaptive classifier that leverages the wide variability in data complexity to enable energy-efficient data classification operations for mobile systems. Our approach takes advantage of varying classification hardness across data to dynamically allocate resources and improve energy efficiency. On average, our adaptive classifier is  $\approx 100 \times$  more energy efficient but has  $\approx 1\%$  higher error rate than a complex radial basis function classifier and is  $\approx 10 \times$  less energy efficient but has  $\approx 40\%$  lower error rate than a simple linear classifier across a wide range of classification data sets. We also developed a field of groves (FoG) implementation of random forests (RF) that achieves an accuracy comparable to Convolutional Neural Networks (CNN) and Support Vector Machines (SVM) under tight energy budgets. The FoG architecture takes advantage of the fact that in random forests a small portion of the weak classifiers (decision trees) might be sufficient to achieve high statistical performance. By dividing the random forest into smaller forests (Groves), and conditionally executing the rest of the forest, FoG is able to achieve much higher energy efficiency levels for comparable error rates. We also take advantage of the distributed nature of the FoG to achieve high level of parallelism. Our evaluation shows that at maximum achievable accuracies FoG consumes  $\approx 1.48 \times$ ,  $\approx 24 \times$ ,  $\approx 2.5 \times$ , and  $\approx 34.7 \times$  lower energy per classification compared to conventional RF, SVM<sub>RBF</sub>, Multi-Layer Perceptron Network (MLP), and CNN, respectively. FoG is  $6.5 \times$  less energy efficient than SVM<sub>LR</sub>, but achieves 18% higher accuracy on average across all considered datasets.

## Contents

| 1 Introduction |                  | roducti | ion                                                               | 1  |

|----------------|------------------|---------|-------------------------------------------------------------------|----|

|                | 1.1              | Backg   | round and Motivation                                              | 1  |

|                | 1.2              | Gener   | al Principles for Energy-Efficient System Design                  | 4  |

|                | 1.3 Related Work |         | ed Work                                                           | 12 |

|                |                  | 1.3.1   | Circuits and Architectures that Trade-Off Performance, Energy,    |    |

|                |                  |         | and Error Rate                                                    | 12 |

|                |                  | 1.3.2   | Adaptive Systems and Machine Learning Hardware                    | 15 |

|                | 1.4              | Contra  | ibutions                                                          | 20 |

| <b>2</b>       | Err              | or Mit  | igation in Digital Logic Using Feedback Equalization              | 25 |

|                | 2.1              | Introd  | luction                                                           | 25 |

|                | 2.2              | Error   | Manifestations in Digital Logic                                   | 26 |

|                | 2.3              | Equal   | ization Techniques                                                | 28 |

|                |                  | 2.3.1   | Feedback circuit                                                  | 29 |

|                |                  | 2.3.2   | Schmitt trigger                                                   | 30 |

|                |                  | 2.3.3   | Feedback Equalization with Schmitt Trigger (FEST) $\ . \ . \ .$ . | 31 |

|                | 2.4              | Exper   | imental Results                                                   | 33 |

|                |                  | 2.4.1   | Kogge-Stone Adder                                                 | 33 |

|                |                  | 2.4.2   | Finite Impulse Response Filter                                    | 36 |

|                | 2.5              | Exper   | imental Results for Near-Threshold Design                         | 38 |

|                |                  | 2.5.1   | Experimental Setup                                                | 38 |

|                |                  | 2.5.2   | Experimental Results                                              | 39 |

|   | 2.6                                                                   | Concl                                                               | usion                                                                | 41 |  |  |

|---|-----------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------|----|--|--|

| 3 | Energy Efficient Pass-Transistor Logic Using Decision Feedback Equal- |                                                                     |                                                                      |    |  |  |

|   | izat                                                                  | ion                                                                 |                                                                      | 45 |  |  |

|   | 3.1                                                                   | Introd                                                              | luction                                                              | 45 |  |  |

|   | 3.2                                                                   | Equal                                                               | ized Pass-Transistor Logic                                           | 47 |  |  |

|   | 3.3                                                                   | Model                                                               | ling and Design Automation of E-PTL                                  | 50 |  |  |

|   |                                                                       | 3.3.1                                                               | Power Modeling                                                       | 50 |  |  |

|   |                                                                       | 3.3.2                                                               | Error Rate Modeling                                                  | 51 |  |  |

|   |                                                                       | 3.3.3                                                               | Delay Modeling                                                       | 56 |  |  |

|   |                                                                       | 3.3.4                                                               | Optimization Tool-flow                                               | 56 |  |  |

|   |                                                                       | 3.3.5                                                               | Modeling vs. Simulation                                              | 57 |  |  |

|   | 3.4                                                                   | Evalu                                                               | ation                                                                | 58 |  |  |

|   | 3.5                                                                   | Concl                                                               | usion                                                                | 60 |  |  |

| 4 | Ada                                                                   | Adaptive Classification: Energy-Efficient Design for Machine Learn- |                                                                      |    |  |  |

|   | ing                                                                   |                                                                     |                                                                      | 61 |  |  |

|   | 4.1                                                                   | Introd                                                              | luction                                                              | 61 |  |  |

|   | 4.2                                                                   | Adapt                                                               | tive Classifier – Theory                                             | 64 |  |  |

|   |                                                                       | 4.2.1                                                               | Hardness of an Input and Penalty for Misclassification $\ . \ . \ .$ | 64 |  |  |

|   |                                                                       | 4.2.2                                                               | Training the "chooser" for a fixed energy budget                     | 67 |  |  |

|   |                                                                       | 4.2.3                                                               | Training the "chooser" for a changing energy budget $\ . \ . \ .$    | 71 |  |  |

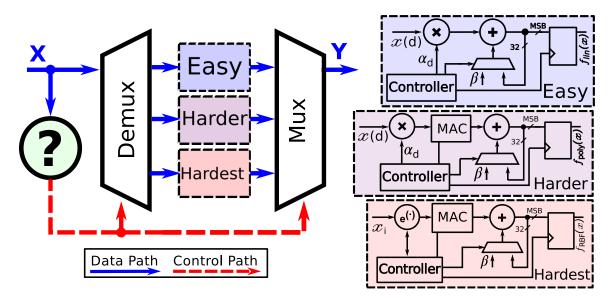

|   | 4.3                                                                   | Adapt                                                               | tive Classifier – Microarchitecture Description                      | 73 |  |  |

|   | 4.4                                                                   | Evalu                                                               | ation                                                                | 76 |  |  |

|   |                                                                       | 4.4.1                                                               | Experimental Setup                                                   | 78 |  |  |

|   |                                                                       | 4.4.2                                                               | Experimental Results of an approach with static energy budget        | 81 |  |  |

|   |                                                                       | 4.4.3                                                               | Experimental Results of the approach with dynamic energy             |    |  |  |

|   |                                                                       |                                                                     | budget                                                               | 85 |  |  |

|                     | 4.5           | Discus                         | ssion                                                         | 88  |

|---------------------|---------------|--------------------------------|---------------------------------------------------------------|-----|

|                     | 4.6           | Concl                          | usion                                                         | 89  |

| <b>5</b>            | Raı           | ndom l                         | Forest and the Field of Groves                                | 91  |

|                     | 5.1           | Introd                         | luction                                                       | 91  |

|                     | 5.2           | Energ                          | y-Efficient Computing using Random Forests                    | 93  |

|                     |               | 5.2.1                          | Field of Groves Algorithm                                     | 96  |

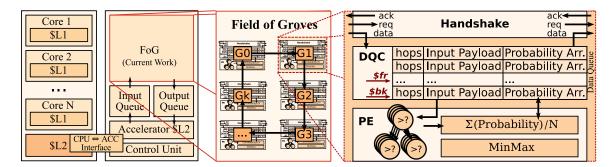

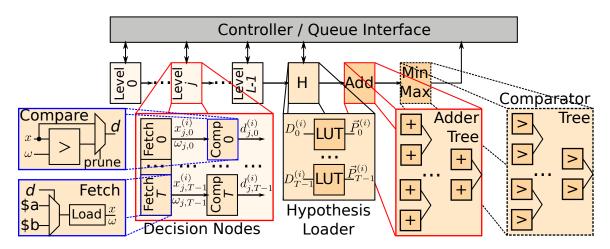

|                     |               | 5.2.2                          | Micro-architecture                                            | 100 |

|                     | 5.3           | Evalu                          | ation                                                         | 106 |

|                     |               | 5.3.1                          | Experimental Setup                                            | 106 |

|                     |               | 5.3.2                          | Experimental Results                                          | 112 |

|                     | 5.4           | 5.4 Conclusion                 |                                                               | 116 |

| 6                   | Cor           | nclusio                        | n and Future Work                                             | 118 |

|                     | 6.1           | Summ                           | nary of Contributions                                         | 118 |

|                     |               | 6.1.1                          | Feedback Equalization                                         | 118 |

|                     |               | 6.1.2                          | Machine Learning Accelerators                                 | 120 |

|                     | 6.2           | 6.2 Future Research Directions |                                                               | 122 |

|                     |               | 6.2.1                          | Feed-Forward Equalization in Pass-Transistor Logic            | 122 |

|                     |               | 6.2.2                          | Specialized Architectures for Machine Learning Acceleration . | 123 |

|                     |               | 6.2.3                          | Bridging the gap between Hardware and Machine Learning        | 124 |

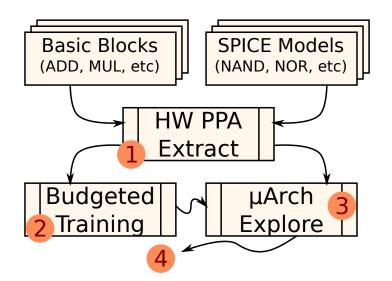

| R                   | References 12 |                                |                                                               | 125 |

| Curriculum Vitae 14 |               |                                |                                                               | 141 |

## List of Tables

| 2.1 | Inverter threshold values                                                     | 29  |

|-----|-------------------------------------------------------------------------------|-----|

| 2.2 | Switching thresholds of different designs                                     | 32  |

| 2.3 | Evaluation results of different designs                                       | 44  |

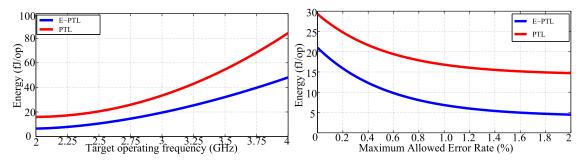

| 3.1 | Minimum energy comparison of different designs                                | 60  |

| 4.1 | Notation and variables used in the current work $\ldots \ldots \ldots \ldots$ | 64  |

| 4.2 | Pseudo-label assignment example: given different inputs "8", we gen-          |     |

|     | erate pseudo-labels depending on the correct predictions of the "core".       | 65  |

| 4.3 | Datasets used and the number of inputs misclassified during the train-        |     |

|     | ing phase.                                                                    | 66  |

| 4.4 | Energy and Delay for the adaptive classifier and conventional classifiers     |     |

|     | for different data sets. Each row corresponds to subplots in Figure 4.5.      |     |

|     | Energy results are shown in J/classification and delay is represented         |     |

|     | as $\mu s$                                                                    | 77  |

| 4.5 | Comparison of the proposed and SEC approaches (Venkataramani et al.,          |     |

|     | 2015a) trained for low energy subject to error rate budget. The time          |     |

|     | is in seconds.                                                                | 78  |

| 5.1 | Notation used in section 5.2.2                                                | 100 |

| 5.2 | Datasets used for FoG evaluation                                              | 107 |

| 5.3 | Accuracy and Energy dissipation for FoG                                       | 110 |

| 5.4 | CPU, GPU, and FPGA Results for FoG                                            | 117 |

# List of Figures

| $1 \cdot 1$  | Low-power parallel and pipelined computing                                    | 5  |

|--------------|-------------------------------------------------------------------------------|----|

| $1 \cdot 2$  | Order of Execution matters                                                    | 6  |

| $2 \cdot 1$  | DC response of the feedback equalizer circuit.                                | 27 |

| $2 \cdot 2$  | Variable threshold inverter circuit (Sridhara et al., 2008)                   | 28 |

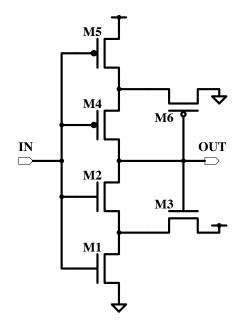

| $2 \cdot 3$  | Inverting Schmitt trigger circuit (Baker, 2004)                               | 30 |

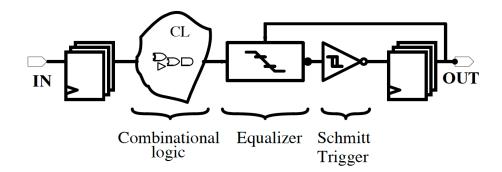

| $2 \cdot 4$  | Pipelined combinational logic with FEST circuit.                              | 31 |

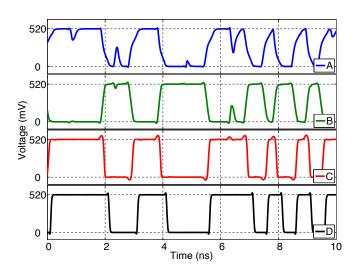

| $2 \cdot 5$  | Transients of KSA                                                             | 34 |

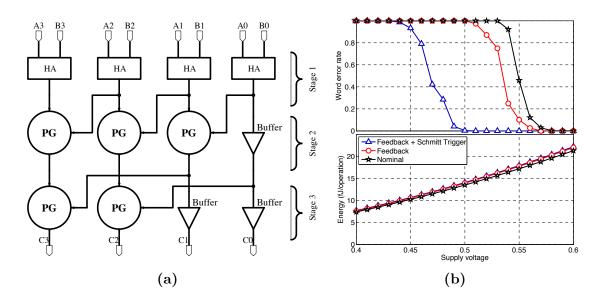

| $2 \cdot 6$  | 4-bit KSA                                                                     | 35 |

| $2 \cdot 7$  | 4-bit, 3-tap FIR                                                              | 36 |

| $2 \cdot 8$  | EDP results across entire above-threshold range $\ldots \ldots \ldots \ldots$ | 40 |

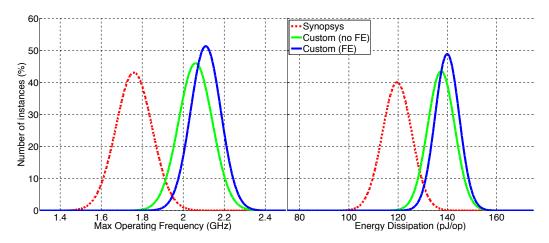

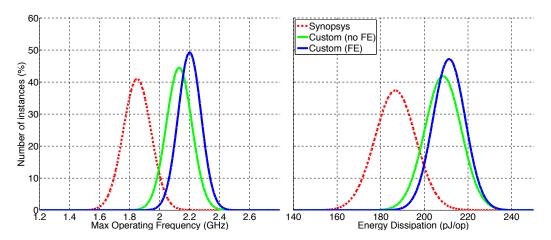

| $2 \cdot 9$  | Distribution of 24-bit multiplier                                             | 41 |

| $2 \cdot 10$ | Distribution of AES-256                                                       | 42 |

| $2 \cdot 11$ | Distribution of RS Decoder                                                    | 43 |

| 2.12         | Distribution of an FFT                                                        | 43 |

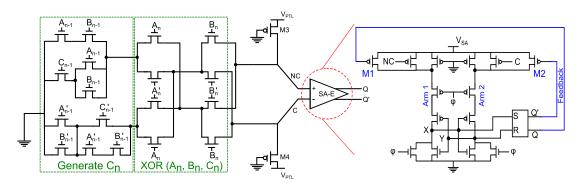

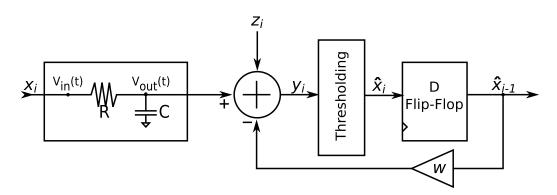

| $3 \cdot 1$  | Schematic diagram of a Equalized Pass-Transistor Logic (E-PTL) $$ .           | 47 |

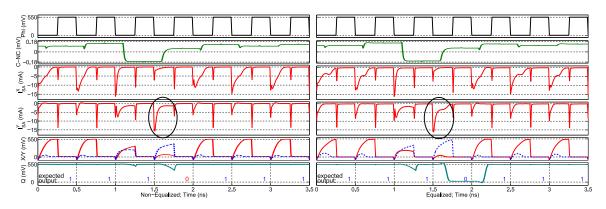

| $3 \cdot 2$  | Transients of equalized and non-equalized                                     | 47 |

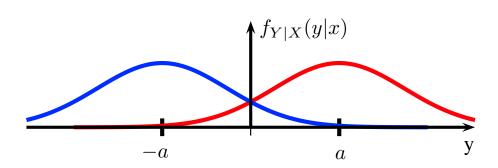

| $3 \cdot 3$  | PDF of noisy PTL                                                              | 51 |

| $3 \cdot 4$  | Model of the proposed E-PTL                                                   | 53 |

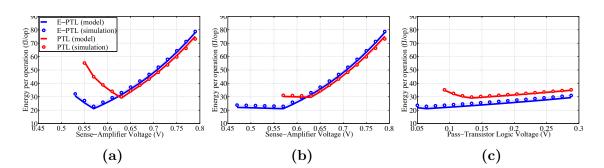

| 3.5          | Model vs. Simulation for 16-bit CLA                                           | 55 |

| $3 \cdot 6$  | 16-bit Carry-Look Ahead Adder                                                 | 57 |

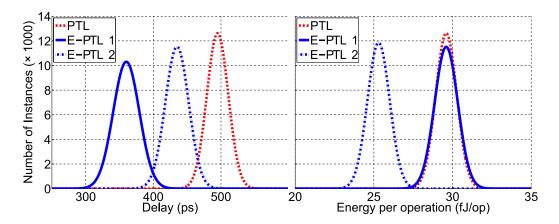

| 3.7          | Monte-Carlo simulation results for CLA                                        | 59 |

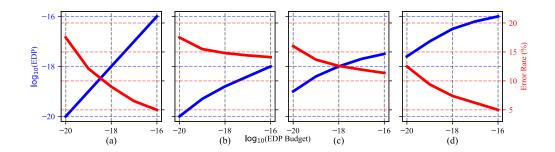

| $4 \cdot 1$ | EDP and Error rate vs. the budget of an adaptive classifier: (a) trained                        |

|-------------|-------------------------------------------------------------------------------------------------|

|             | with EDP budget as a feature; $(b,c,d)$ trained to maximize the accuracy                        |

|             | while meeting an energy constraint of $10^{-20}$ , $10^{-18}$ , and $10^{-16}$ respectively. 72 |

####

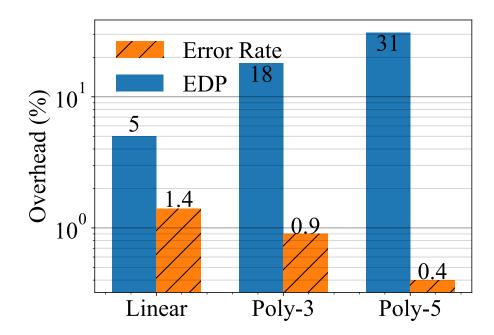

- 4.4 Average overheads of different types of "chooser" functions. The EDP overhead is average EDP contribution of the "chooser" with respect to an adaptive classifier where this "chooser" is implemented. The error rate overhead is the error rate contributed by the "chooser" function itself.

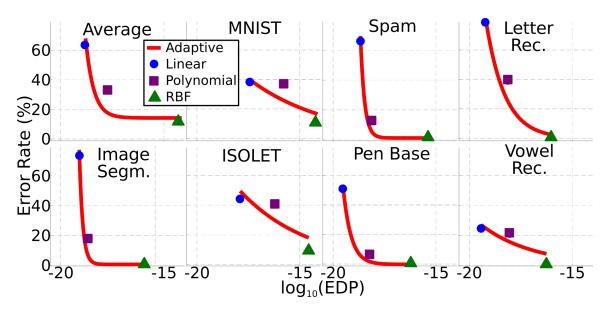

4.5 Error rate vs. Energy Delay Product (EDP) for adaptive classifier and

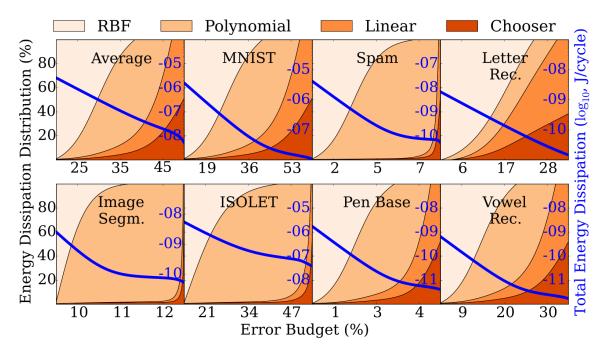

- 4.6 Energy dissipation distribution and the total energy dissipation vs.

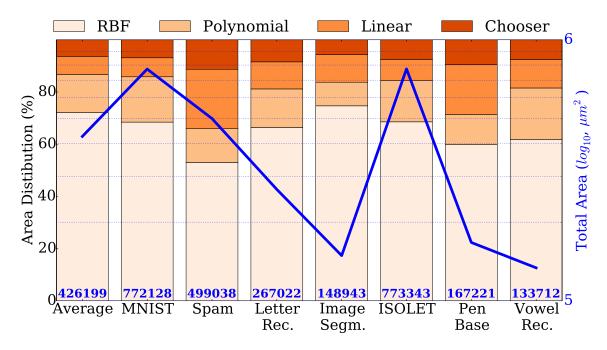

4.7 Relative area distribution of subblocks in adaptive classifier (bars) as

####

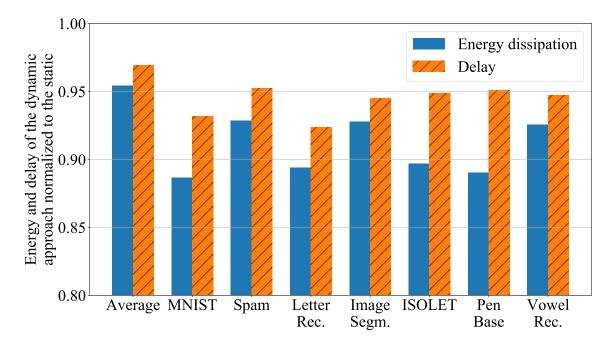

| $4 \cdot 8$ | Energy dissipation and accuracy for dynamic adaptive classifier nor-     |     |  |

|-------------|--------------------------------------------------------------------------|-----|--|

|             | malized to the adaptive classifier trained for the static energy budget. | 87  |  |

| $5 \cdot 1$ | Example of a Random Forest                                               | 93  |  |

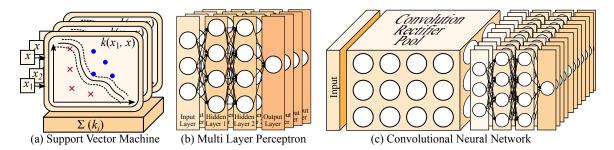

| $5 \cdot 2$ | Common Machine Learning Algorithms                                       | 94  |  |

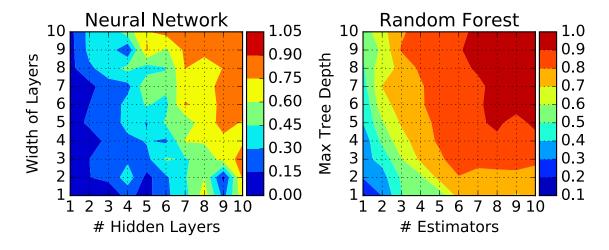

| 5.3         | Accuracy degradation for MLP and RF                                      | 94  |  |

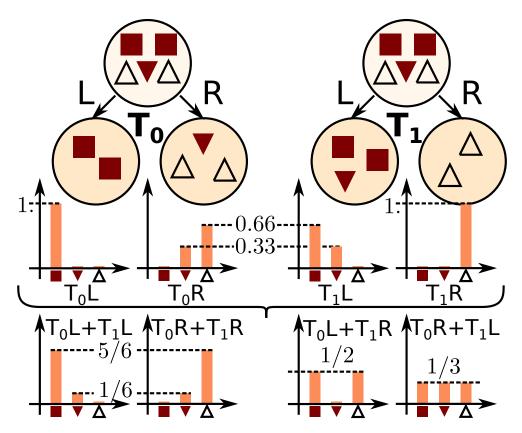

| $5 \cdot 4$ | Logical view of RF and FoG                                               | 99  |  |

| 5.5         | Field of Groves implementation                                           | 101 |  |

| $5 \cdot 6$ | FoG processing element (PE)                                              | 102 |  |

| 5.7         | FoG system design flow diagram                                           | 108 |  |

| 5.8         | Accuracy and Energy dissipation of different classifiers                 | 111 |  |

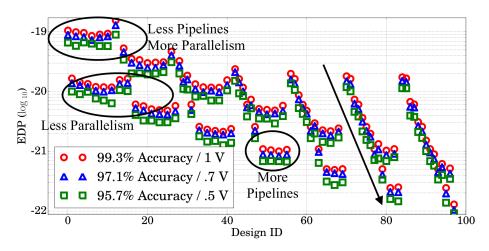

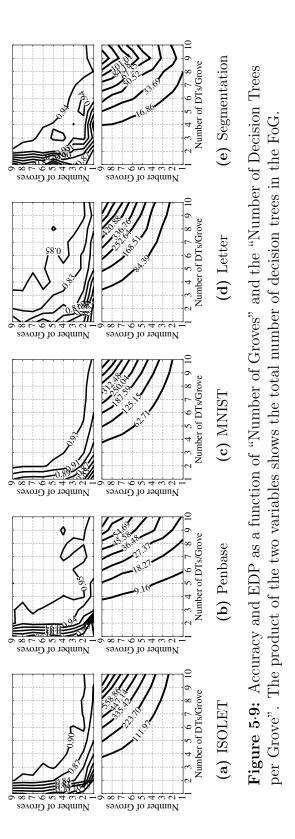

| 5.9         | Accuracy and EDP of FoG                                                  | 114 |  |

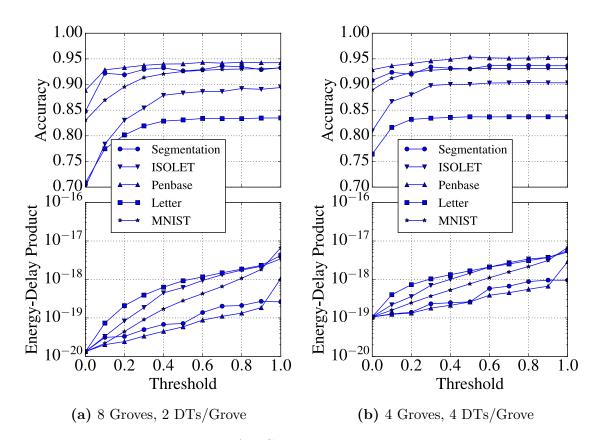

| 5.10        | Example of FoG run-time tuning using the "threshold" variable            | 115 |  |

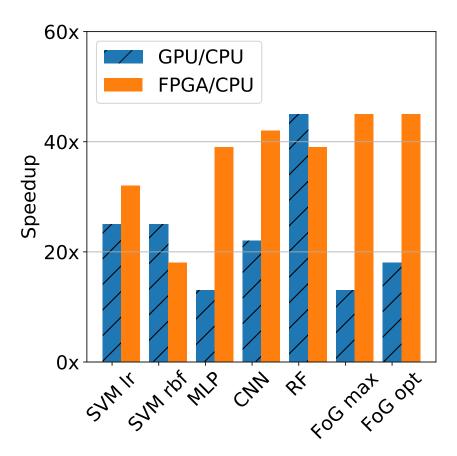

| 5.11        | Computational performance comparison between GPU, FPGA, and              |     |  |

|             | SIMD CPU                                                                 | 116 |  |

## List of Abbreviations

| AC     | Alternating Current                        |

|--------|--------------------------------------------|

| ACU    | Analog Computing Unit                      |

| AGC    | Automatic gain control                     |

| AI     | Artificial Intelligence                    |

| ALU    | Arithmetic Logic Unit                      |

| ANN    | Artificial Neural Network                  |

| API    | Application Programming Interface          |

| ASIC   | Application-specific Integrated Circuit    |

| BJT    | Bipolar Junction Transistor                |

| BLAS   | Basic Linear Algebra Subprograms           |

| BSD    | Berkeley Software Distribution             |

| BU     | Boston University                          |

| CMOS   | Complimentary Metal-oxide-semiconductor    |

| CNN    | Convolutional Neural Network               |

| CORDIC | Coordinate Rotation Digital Computer       |

| CPU    | Central Processing Unit                    |

| CUDA   | NVIDIA's Parallel Programming API for GPUs |

| DBN    | Deep Belief Network                        |

| DC     | Direct Current                             |

| DNN    | Deep Neural Network                        |

| DSP    | Digital Signal Processor                   |

| DVFS   | Dynamic Voltage and Frequency Scaling      |

| E-PTL  | Equalized Pass-Transistor Logic            |

| EDEP   | Energy-delay-error Product                 |

| EDP    | Energy-delay Product                       |

| EMC    | Or Dell $EMC^2$ – Egan-Marino Corporation  |

| EU     | Arbitrary energy dissipation unit          |

| FANN   | Fast Artificial Neural Network library     |

| FEST   | Feedback Equalization with Schmitt Trigger |

| FFE    | Feedforward Equalization                   |

| FoG    | Field of Groves accelerator                |

| FPGA   | Field Programmable Gate Array              |

| GPU    | Graphics Processing Unit                   |

| HDL    | Hardware Description Language              |

| HW     | Hardware                                   |

| IBM    | International Business Machines                       |

|--------|-------------------------------------------------------|

| ICSG   | Boston U. Integrated Circuits and Systems Group       |

| IEEE   | The Institute of Electrical and Electronics Engineers |

| IDC    | International Data Corporation                        |

| ISA    | Instruction Set Architecture                          |

| ІоТ    | Internet of Things                                    |

| JPEG   | Joint Photographic Experts Group                      |

| LEAP   | Boston U. Late Entry Accelerated Program              |

| LSTM   | Long Short Term Memory                                |

| MAC    | Multiply Accumulate                                   |

| ML     | Machine Learning                                      |

| MLP    | Multilayer Perceptron Neural Network                  |

| MOSFET | Metal-oxide-semiconductor Field-effect-transistor     |

| MSE    | Mean Squared Error                                    |

| NASA   | The National Aeronautics and Space Administration     |

| NN     | Neural Network                                        |

| NTC    | Near-Threshold Computing                              |

| NTV    | Near-Threshold Voltage                                |

| OS     | Operating System                                      |

| PC     | Personal Computer                                     |

| PE     | Processing Element                                    |

| PTL    | Pass Transistor Logic                                 |

| PVT    | Process, Voltage, Temperature (variations)            |

| RBF    | Radial Basis Function                                 |

| RISC   | Reduced Instruction Set Computer                      |

| RISC-V | Fifth Generation of RISC Instruction Sets             |

| RNN    | Recurrent Neural Network                              |

| RTL    | Register-transfer Level                               |

| RoCC   | Rocket Custom Coprocessor                             |

| SIMD   | Single Instruction Multiple Data                      |

| SNR    | Signal-to-Noise Ratio                                 |

| SVM    | Support Vector Machine                                |

| TPU    | Tensor Processing Unit                                |

| UART   | Universal Asynchronous Receiver/Transmitter           |

| VCD    | Value Change Dump                                     |

| VLSI   | Very Large Scale Integration                          |

|        |                                                       |

## Chapter 1

## Introduction

### 1.1 Background and Motivation

As we enter the 'Internet of Things' (IoT) regime, the computing industry is placing more and more emphasis on designing energy-efficient mobile systems (Wu, 2015). This increasing emphasis on energy-efficiency is driven by the need for the mobile systems to be able to process large quantities of data in real time (which requires proportional amount of energy) and also the slow development in battery technology. Moreover, these mobile systems are expected to operate in a variety of environments, and hence there is a need to develop tunable/adaptive systems that can dynamically adapt and maximize the system energy efficiency. The focus of this research is to address this energy efficiency problem by developing tunable digital logic circuits as well as developing hardware based on adaptive data processing algorithms.

In addition to IoT, emerging paradigm of "Big Data" is also driving research towards more energy-efficient designs. Big Data is a general name for data sets so large and complex that traditional approaches to computation become inadequate. A good example of "Big Data" is social media analysis – information whether someone "liking" company pages on Facebook or tweeting complaints about products needs to be harvested and processed in order to deliver the best customer interaction. Widespread access to information as well as ever increasing rate of information generation require new energy-efficient data-processing computation units (IDC and EMC2, 2012, Bell et al., 1972). This problem of Big Data and IoT is non-trivial - devices are getting smaller 100 times every decade (TSensors, 2013), and every year the number of active nodes connected to the Web is increasing by hundreds of thousands (Hilbert and Lopez, 2011, IDC and EMC2, 2013, TSensors, 2013). Fundamentally, this creates a demand for a new design paradigm in the area of mobile computing. Miniaturization of energy sources and "intelligent" power management, although being of research interest, is not growing as fast as the demand for computation, making energy-efficiency an immediate requirement.

Currently, there are multiple parallel efforts in place to design energy-efficient computing systems. At the device level, Complementary Metal Oxide Semiconductor (CMOS) technology scaling enabled us to lower power and improve performance every two years. However, CMOS technology scaling has slowed down and is expected to end in the next 10 years, thus limiting the improvements in energy efficiency (Williams, 2017). Hence, alternate switching devices like Tunnel Field Effect Transistors (TFETs), Carbon Nanotube FETs (CNFETS) are being explored (Richter et al., 2014, Paul et al., 2006). Other emerging technologies such as graphene FETs (Iannazzo et al., 2015, Khan et al., 2014), silicon NanoWire FETs (Turkyilmaz et al., 2013, Yazeer et al., 2016), Spintronics (Bishnoi et al., 2017), and Memristor-based systems (Zangeneh and Joshi, 2014a) have also shown promising results in pushing the boundaries of the Moore's law.

At the circuit level, (Zhai et al., 2004) and (Calhoun and Chandrakasan, 2004) have shown that there exists a minimum energy supply voltage, which lies in the subthreshold region (Wang and Chandrakasan, 2004). Although subthreshold design enables ultra-low energy dissipation, the drawback of subthreshold design is that energy reduction comes at a price of significant performance degradation, which lowers the energy efficiency. A better approach is to operate the circuits near the threshold voltage. This operating point provides the best balance between energy dissipation and performance (Dreslinski et al., 2010). However, we would like to note that this balanced operating point is highly dependent on the application and environmental conditions. As a result, the solution to this energy efficiency problem should 1) have the ability to operate at-or-near the maximum energy efficiency point, 2) have the ability to adapt to changing environmental conditions while satisfying condition 1, and 3) have the mechanism to change the current operating figures-of-merit if the environment (i.e. battery state) change. To tackle these requirements, we propose a multilayer approach to energy-efficient computing. In particular, we laid the grounds for the development of circuit-, architecture-, and algorithm-level mechanisms as given below:

- Circuit-level mechanism: While designing a circuit, we use a lot of optimization parameters, such as technology node, device dimensions, architecture, routing topology, etc. These parameters can be seen as pre-fabrication knobs for "static optimization". However, it is difficult to predict the exact operating conditions of a circuit. Hence it is necessary to provide a tuning capability in the circuit. In this work we developed a feedback equalization mechanism for computation blocks. In particular we have shown that feedback equalization with Schmitt Trigger and feedback equalization in pass-transistor logic are viable solutions for energy-efficient computation. We expanded this work to enable tunability (details in Chapters 2 and 3), which enables a more robust operation in changing environmental conditions.

- Algorithm-level mechanisms: Generally algorithmic approaches are application specific, however, we showed that is it possible to develop an adaptive system that would utilize machine learning in order to achieve adaptability. For example a mobile processor, that is manufactured without prior knowledge of

operating conditions might utilize machine learning algorithms to adapt to the changing environment. In this case the machine learning approach creates a "tuning knob" for trading off energy, performance, as well as error rate, where applicable. As shown in Chapter 4, machine learning algorithms can be utilized to adapt to changing operating conditions, such as change in workload, change in performance requirements, energy budget, etc. In our work we show that using machine learning approaches, a more energy-efficient operating point for supply voltage is achievable. We also show the implementation of a reconfigurable machine learning approach to enable adaptability for changing input data-sets.

• Architecture-level mechanisms: Ideally, one would like to have sight of the entire computing stack, and without the discussion of the architecture-level mechanisms the picture of energy-efficient computing is incomplete. In Chapter 5 we propose the use of distributed architecture to achieve lower energy dissipation using decision forest. In general we show that machine learning systems that benefit from graceful degradation of accuracy are logical choice to operate in ever-changing energy-budget conditions in mobile systems.

### **1.2** General Principles for Energy-Efficient System Design

To provide a little more general background on energy efficiency, let us share some insights that we have gathered with regard to the energy-efficient and low-power hardware design. In this subsection we would like to summarize some high level ideas that one must always consider, as well as some general "tips" that might be useful as stated in (Sarpeshkar, 2010, Rabaey, 2009, Lee, 2004, Chandrakasan, 1996). Note, that there is no "silver bullet" in designing energy-efficient circuits, architectures, and algorithms. However, the following key ideas might be a good starting point towards

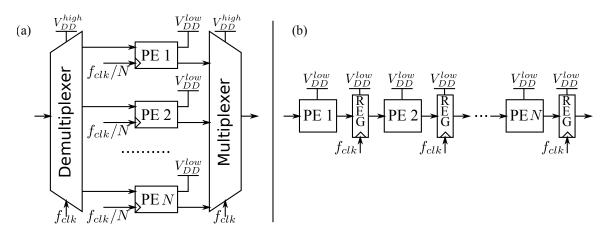

**Figure 1.1:** Conceptual diagrams of low-power computing architectures. (a) Parallel architecture with N low voltage slow processing elements (PEs); (b) Pipelined version of the computing unit with N slow elements operating at low voltage.

improving the energy related figures-of-merit (FoMs).

Two of the most popular ideas for energy-efficient circuit designs are **parallelism** and **pipelining**. Circuit level parallelism uses a demultiplexer to redirect a highbandwidth serial input to many low-throughput identical slow-and-parallel computing units. The outputs are then sequentially sampled by a fast multiplexer to recreate the high-throughput serial output. Figure 1·1(a) shows an illustration of this concept as proposed in (Chandrakasan and Brodersen, 1995). N processing elements (PEs) are operating at lower voltage and frequency ( $V_{DD}^{low}$  and  $f_{clk}/N$  respectively). This architecture has a multiplexer and a demultiplexer that operate at high voltage  $V_{DD}^{high}$ in order to support higher frequency  $f_{clk}$ . Figure 1·1(b) shows the pipelined version of the computing system. This architecture does not need to serialize the inputs and deserialize the outputs, and thus has no need for fast, high-voltage components. The dynamic power dissipation for parallel and pipelined architectures can be written as

$$P_{nominal} = \alpha f_{clk} C_{big} V_{DD}^{high^2} \tag{1.1}$$

$$P_{parallel} = \alpha f_{clk} \left( C_{PE} V_{DD}^{low^2} + C_{MUX} V_{DD}^{high^2} \right)$$

(1.2)

$$P_{pipeline} = N \cdot \alpha f_{clk} V_{DD}^{low^2} \left( C_{PE} + C_{REG} \right), \qquad (1.3)$$

where  $C_{big}$ ,  $C_{PE}$ ,  $C_{MUX}$ , and  $C_{REG}$  are the parasitic capacitances for a nominal (nonparallel, non-pipelined), small-and-slow PE, multiplexer/demultiplexer, and register designs respectively. Note that the pipelined version of the architecture introduces factor N in the dynamic power consumption, but does not include the high-voltage  $C_{MUX}$  as does the parallel architecture. The design choice between parallel and pipelined versions depends on how many slow PE elements are available and what the power dissipation of individual components in the system is.

The **order** in which the computations are done in an architecture also affects overall energy efficiency of a system. In general terms, computations that reduce the information bandwidth of the data should occur as early as possible. For example, spatial filtering or convolution that allows image information to be encoded in a compressed representation should occur early in the computational pipeline. One of the often overlooked principles of energy-efficient computing is the use of **intelligent**-

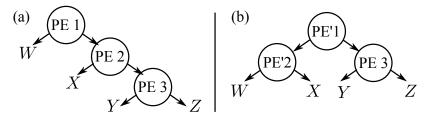

Figure 1.2: Order of execution is defined by the use of an applicable intelligent-and-efficient algorithm, especially in conditional execution: (a) Processing elements are arranged sequentially, and the results are identified conditionally after each PE; (b) Same results with modified conditional PEs arranged in a tree.

7

and-efficient algorithms with inherently low operation count. In general, this idea dictates the trade-offs that govern the choice of level of parallelism, pipelining, order of execution, and architecture topology. As a general example, algorithms with operations organized in a conditional tree may lead to only a logarithmic number of computing operations, which might be considered intelligent-and-efficient, and in a nutshell represents choice between pipelined vs. parallel execution. Figure 1.2 shows conceptual diagram of different ordering of the processing elements. In this example, if we assume conditional execution, we might choose either (a) sequential or (b) tree-like architecture. The average energy cost for executing architectures (a) and (b) could roughly be estimated as  $\mathbb{E}_{(a)} = \mathbb{E}_{PE} \cdot (P_W \cdot 1 + P_X \cdot 2 + P_Y \cdot 3 + P_Z \cdot 3)$  and  $\mathbb{E}_{(b)} = \mathbb{E}_{PE} \cdot (P_W \cdot 2 + P_X \cdot 2 + P_Y \cdot 2 + P_Z \cdot 2)$  respectively, where  $\mathbb{E}_{PE}$  is the average energy dissipation per conditional PE, and  $P_{\{W,X,Y,Z\}}$  is the probability of different conditionals.

To illustrate the choice between different architectures for conditional execution shown on figures 1.2 (a) and (b), consider an example when the cost of all PEs is 1 energy unit (EU), and conditions W, X, Y, and Z are equiprobable ( $P_{\{W,X,Y,Z\}} = 0.25$ ). In that case the average energy cost for (a) would be  $\mathbb{E}_{(a)} = 2.25$  EUs. However, the use of tree-like architecture (b) would yield  $\mathbb{E}_{(b)} = 2.0$  EUs. As a counter example, let us assume that the conditions happen with probabilities  $P_W = 0.5, P_X =$  $0.25, P_{\{Y,Z\}} = 0.125$ . In that case,  $\mathbb{E}_{(a)} = 1.75$  EU, while  $\mathbb{E}_{(b)} = 2.0$  EU. This example, although over-simplified, shows how the choice of architectures and algorithms can improve the overall energy efficiency.

In addition to the general ideas mentioned above, we can identify several principles or "tips" for low-power design. Although there is some overlap and redundancy in these principles, we are hoping these principles will capture the essence of the underlying idea of energy efficiency. The principles, in no particular order, are

- 1. Exploit preprocessing in an optimal way. Preprocessing a high-throughput input often improves all FoMs in a low-power or energy-efficient system. The preprocessing was shown to be very efficient in analog domain (Sarpeshkar et al., 2005, Avestruz et al., 2008). In digital domain convolutional layers in CNNs effectively preprocess the input to extract more information (Simard et al., 2003), thus improving the accuracy. Chapter 4 describes an adaptive classifier that has a "chooser" function that can be seen as preprocessing the input by identifying its "hardness" and selectively enabling different computational paths.

- 2. Find a technology that "encodes" your computation. Some functions, such as simple integration or even RBF (Tsividis et al., 1990) is possible to implement using a single bypolar junction transistor (BJT), which could significantly improve energy-efficiency. Another example is the use of emerging technologies such as memristive crossbar networks to mitigate the processor-memory bottleneck (Velasquez and Jha, 2014). "Technology encodings" were shown to be efficient in both analog and digital domains (Rabaey, 2009, Sarpeshkar, 2010)

- 3. Use parallel and pipelined architectures. As described earlier, parallel and pipelined systems implement complex computational systems through divideand-conquer approach. The speed, complexity, and accuracy of each PE can be significantly less than that needed in the overall computation. Chapter 5 describes an energy-efficient way of implementing random forest and field of groves algorithms using parallelization and pipelining.

- 4. Balance computation and communication costs. A frequent trade-off in many mobile and embedded systems is the balance between communication and computation energy costs. If one computes too little, there is too much information to transmit, increasing the communication cost. On the other hand,

if computing too much, one might be passing on the opportunity to save some energy by computing in the "cloud". The optimal solution for this problem is still in its infancy, and requires extensive analyses.

- 5. Use hybrid systems. In the mixed-signal domain, the concept of hybrid (Sarpeshkar, 1998) and collective analog (Mandal et al., 2009) is widely used to combine the best of the analog and digital worlds to design ultra low-power systems. The main idea is to separate the computation into multiple simpler blocks that communicate with each other, thus using parallelization and rebalancing the computation vs. communication costs. This principle overlaps with the principle of parallelism but does not assume that the processing elements in the system are identical. Expanding the definition of the hybrid systems, we would also include the notion of specialized accelerators under this bullet. A complex system can be separated into two parts:

- (a) General purpose processor: high ignorance of what is important; limited adaptation; no learning; highly energy-efficient for general tasks;

- (b) Specialized accelerator: high knowledge of what is important; supporting adaptation and live reprogrammability; high use of analog and mixedsignal components in addition to digital; highly energy-efficient for specialized tasks.

Chapters 4 and 5 describe accelerators that are specialized for machine learning classification, and achieve high energy-efficiency compared to general purpose processors.

6. Reduce the amount of information to be processed. Energy and information are naturally linked, and the overarching principle of information reduction could encompass all principles in low-power or energy-efficient design listed here. This principle is rather abstract, and its concrete implementation requires the knowledge of the algorithms, signal processing, architectures, circuit topologies, as well as prior knowledge of the types of data that would be processed, and application for the design.Many examples could be placed under this principle, ranging from purely analog circuits such as automatic gain control (AGC) (Baker and Sarpeshkar, 2006) and ending with efficient digital algorithms like clock gating (Rabaey, 2009). Adaptive classifier described in chapter 4 can be loosely seen as utilizing this principle by adaptively selecting how much information should be processed by linear, polynomial, or infinite order RBF blocks.

- 7. Use feedback and feedforward architectures. Feedback is an important concept in improving both the efficiency and robustness of an energy-efficient system. The energy-efficiency of the feedback stems from three primary mechanisms (Sarpeshkar, 2010): 1) a lowpass or integrator transfer function in a feedback path provides differentiation, delta encoding, highpass filtering, or "adaptation" such that unwanted information (usually DC) is removed, while desirable information (usually AC) is propagated; 2) non-linear feedback implements automatic gain control or compression, which allows relatively constant average information (as current or SNR) to be mapped from input to output even if environmental conditions change; 3) feedback attenuation of the device noise statistics. Chapters 2 and 3 describe our view of how the feedback loop is incorporated in the computational channels.

- 8. Separate speed and precision/accuracy. Recent advances in the domain of machine learning (Wang et al., 2017) have shown drastic improvement in all FoMs of energy-efficient approximate computing (see chapter 1.3). However, energy-efficiency is still a major bottleneck in the mobile and embedded systems.

Thus, it is important to remember that it costs power to be simultaneously fast and accurate (whether we are performing analog/digital processing, sensing, or actuating). It is advantageous to design architectures (as far as possible) where speed and precision are not simultaneously needed. For example, in case of the machine learning, it is possible to design systems where only the latch is precise, while the rest of the architecture would utilize low-power approximate computing units. This principle can be seen in nature: neurons "discretize" continuous analog vector inputs into a set of digital outputs. The process of sampling is performed using current-integrating comparator (Sarpeshkar et al., 1992), and is equivalent to an approximate integrator combined with accurate comparator. A typical neuron in the human brain operates on a  $\approx$ 6000-input vector with  $\approx$ 0.5nW of power, such that  $\approx$ 22 billion neurons in the brain consume  $\approx$ 15W of power (Aiello, 1997). Nature inspired a lot of theoretical and practical work (see chapter 1.3).

- Use subthreshold operation if possible. Although not the best tip for high-performance computing modes, operating in subthreshold regime is advantageous from the point of view of low-power operation. According to (Sarpeshkar, 2010, Mead, 1989, Enz and Vittoz, 2006) the main power dissipation reducing traits of operating in the subthreshold regime are 1) maximized speed per watt;

2) lower saturation voltage; 3) no velocity saturation; 4) low resistive and inductive drops dues to parasitics; 5) possibility of implementing machine learning computing blocks in this regime in a highly energy-efficient fashion blocks such as exponential/radial basis function (RBF), tanh, cosh, sinh, etc. can profitably use "leakage" currents as "analog computing units" (ACU).

- 10. **Operate slowly and/or adiabatically.** Although not necessarily energy efficient, operating slowly might be power efficient. One of the reasons why natural

neurons are extremely power efficient is because they operate relatively slowly, and do not dissipate power with the surrounding cells – so called adiabatic process. Operating far below nominal frequency  $f_{nom}$  was shown to be power efficient (Lee, 2004) in digital circuits. It is suggested that following this principle one must try and operate at a frequency the is at least five times below  $f_{nom}$ and because this principles assumes low computational performance, it is best suited to work well in subthreshold regimes as shown in (Sarpeshkar, 2010).

It is worth pointing out that the "No Free Lunch" theorem (Wolpert and Macready, 1997) is universal, and in our case robustness, flexibility, accuracy, and performance always trade-off with energy efficiency: the extra degrees of freedom necessary to maintain robustness or flexibility invariably hurt efficiency; increase in accuracy or performance almost always requires an increase in complexity, thus making the system less efficient. With that said, we employ the reader to accept the listed principles with a grain of salt – keeping the trade-off game in mind.

### 1.3 Related Work

### 1.3.1 Circuits and Architectures that Trade-Off Performance, Energy, and Error Rate

The tunability and adaptability of a system is best described in the context of its operating condition. For example, in high performance computing it is rarely expected for performance to be tuned down, while in medical applications, implant systems are almost always expected to operate in low energy dissipation modes. Mobile systems, however, need and can take advantage of tunability and adaptability where we can trade off for low power dissipation or high performance. A mobile device that is running out of battery can reduce its energy requirements by turning off some of its components to save power. A more intelligent and efficient algorithm for a mobile device would be to collect run-time statistics in order to be able to predict which parts of the system it is more optimal to switch off.

Mobile computing makes an ideal candidate application for dynamically tunable and adaptable systems which could determine the optimal trade off between power dissipation and computational performance at run-time (Gautschi et al., 2017). One can switch the voltage anywhere between nominal voltage to achieve high computational performance and near-threshold voltage (NTC) to achieve the most energy savings (Dreslinski et al., 2010). Operating in the near-threshold regime provides the best energy-performance trade off. One of the main challenges to be addressed in the NTC region is the PVT variability as well as finding the right combination of circuit and architecture solutions that meet the energy-performance specifications. Seok et al. (Seok et al., 2011) have shown several established techniques in mitigating variability from different perspectives: logic, memory, and clock distribution. They have shown that techniques such as body biasing and soft edge clocking are good circuit techniques to minimize the effects of the variability. Karpuzcu et al. (Karpuzcu et al., 2013) proposed an algorithmic approach to NTC, while it was also shown that the energy could be traded-off for reliability and vice versa (Takhirov et al., 2013, Zangeneh and Joshi, 2014b). Although their work does not focus on variability, the algorithm is tunable to trade-off energy for reliability, thus making the trade-off problem three dimensional: while designing a system in near-threshold regime, it is possible to sacrifice one of the three FoMs (energy, performance, or error rate) while improving the other two. Dynamic voltage and frequency tuning (DVFS) is an important part of the run-time tunability, and its precision suffers from temperature variations. Kiamehr et al. have shown that ambient temperature has a huge impact on DVFS in NTC (Kiamehr et al., 2017). The have also proposed a low-cost, ambient temperature aware voltage scaling technique to reduce the unnecessary energy overhead caused by temperature variation. Some recent works provide analysis of process variation effect on the adiabatic logic in NTC (Lu and Kazmierski, 2016), as well as impact of FinFET on NTC scalability (Pinckney et al., 2017).

As the performance of a digital system is limited by error rates, some works are focused on mitigating or detecting and correcting errors due to timing faults in the system. Timing errors happen when some of the timing constraints, such as setup or hold time, are violated (Valadimas et al., 2013). In tunable systems and NTC that happens when the data path delay increases due to aggressive voltage scaling. A number of existing techniques were shown to manage timing errors at the **circuit** level. For example, Razor is a mechanism to tolerate PVT variation induced errors and soft errors by flagging spurious transitions followed by recovery at the architecture level (Ernst et al., 2004, Das et al., 2005, Das et al., 2009). he Razor based approach requires an extra memory element per flip-flop and suffers from high silicon area cost and power consumption. Moreover, in order to treat metastability phenomena in the main flip-flop, a metastability detector is required to guarantee high levels of reliability. Other approaches introduce the use of spatial or temporal computation redundancy at the circuit level (Naeimi and DeHon, 2008, Bowman et al., 2009), timing and delay redistribution (Kahng et al., 2010, Mohapatra et al., 2011), and even circuit level error correcting codes (Lala, 2001, Mathew et al., 2008, Poolakkaparambil et al., 2011). To monitor and mitigate degradation due to HCI, BTI, and dielectric breakdown (TDDB), numerous techniques, such as silicon odometer, in-situ sensors, etc. were proposed (Agarwal et al., 2007, Karl et al., 2008, Keane et al., 2010, Qi and Stan, 2008).

At the architectural level N-modular redundancy with voting mechanism has been widely used to tolerate error (Avirneni et al., 2009, Chen et al., 2011, Sartori et al., 2009). Other approaches used on the architecture level of hierarchy is

the use of stochastic processing platform with multiple functional units (Leem et al., 2010, Narayanan et al., 2010) and instruction-level error correction used in NTC to achieve timing error resilience (Wang et al., 2017), while (Pan and Teodorescu, 2014) presented energy-efficient STT-RAM implementation. These approaches avoid the timing errors by utilizing error-resilient algorithms and their architectural implementations in many-core and many-processor systems. Given the multitude of the approaches to error mitigation and power-performance trade-off techniques, we can combine some of those techniques while using the error rate as a figure-of-merit rather than a constraint: consider an example, where the architecture has some level of error correction. In that case the circuit level constraints could be relaxed in order to achieve better power-specifications (Akturk et al., 2015). At the same time, some applications are error-tolerant by nature, which could allow for error rate to be another dimension in the "trade-off game" (Tagliavini et al., 2016). Our feedback equalization technique (described in chapters 2 and 3) uses variable threshold to mitigate timing errors while maintaining the goal power-performance specifications. In addition to that it enables the possibility of dynamic threshold voltage readjustment by biasing the feedback into the base of the CMOS transistors, which would widen the power-performance tunability range in digital circuits.

#### 1.3.2 Adaptive Systems and Machine Learning Hardware

Apart from the circuit level tunable systems described in this section, it is also important to look into the research performed in the area of adaptive systems. In particular those related to energy efficient adaptive machine learning algorithms. This is motivated by the "Big Data" problem as combined with the problem of "Internet of Things" (IoT), where massive amount of data is being generated, and its processing is required in an energy-constrained environment. Machine Learning (ML) algorithms are one of the most useful tools in the age of the "Big Data" and IoT and are getting more pervasive in the mobile space (ComScore Report 2016, 2016, Abadi et al., 2015). However, because the operating conditions of the mobile devices constantly change during the run-time, the figures-of-merit also change. This means that it is very important to improve the run-time parameters adaptively, rather than statically.

There has been prior work in the implementation of the machine learning algorithms in all levels of abstraction of the hardware design. Some works have focused on application-specific solutions (Kaul et al., 2012, Lin et al., 2005). In general, approximate computing (Grigorian et al., 2015, Venkataramani et al., 2013, Narayanan et al., 2010, Sidiroglou-Douskos et al., 2011, Esmaeilzadeh et al., 2012) leverages the fact that computational effort can be scaled at different levels of abstraction by exploiting the resilience of applications to inexact solutions (Düben et al., 2015, Chippa et al., 2010, Chippa et al., 2011). However, generalizing such approaches to a broader spectrum of applications is a non-trivial task, that current research focuses on.

Recent works have shown that although GP-GPUs are still the most commonly used platform in accelerating machine learning algorithms (Cireşan et al., 2011, Yazdanbakhsh et al., 2015), other platforms are also a viable option. Specifically, neuromorphic approaches are getting more traction, and more works focus on accelerating neural networks. Emulation of the biological linear-leak integrate-and-fire (LLIF) spiking neurons was shown to be possible in basic digital circuits (Nere et al., 2013). It is possible to achieve similar neuromorphic functionality using analog computing with resistive crossbars (Liu et al., 2015), which adopts a rate-coding scheme where pre- and post-neuron signals are represented in digitized pulses. Unfortunately, due to their large computational requirements, purely digital hardware implementations of larger neuromorphic architectures prove to be challenging (Du et al., 2015).

Multiple works tackle the large-scale neuromorphic architectures from different angles. Rahman et al. (Rahman et al., 2016) proposed a flexible and highly efficient

3D neuron array architecture on an FPGA and is a natural fit for convolutional layers of a neural network. One of the main challenges with such an approach is the size of the network, and memory requirements for their acceleration. Techniques like factorization and pruning were proposed to compress the neural network models as well as maintain the form of the models for the execution of neuromorphic architectures (Chung and Shin, 2016). Another way to reduce the size of a model is to remove the near-zero weights, which was shown in (Kim et al., 2016) to improve the energy efficiency of the design without loss in accuracy. In their work, the weights in a neural network were also scaled, and the activation function was embedded in the accumulator, which makes this approach suitable for ultra low power accelerator design. Cambricorn-X (Zhang et al., 2016) exploits sparsity and irregularity in neural networks to achieve energy-efficient neural network acceleration. Their work utilizes an indexing module that efficiently selects and transfers needed neurons to appropriate processing elements. A more general purpose accelerators such as DaDianNao (Chen et al., 2014) uses multiple multi-stage processing elements to achieve energy-efficient acceleration of machine-learning algorithms in general. This approach inspired a whole family of DianNao accelerators (Chen et al., 2016a).

Another field that is of high interest in hardware design, is the application of the emerging technologies in neuromorphic computing and in machine learning in general (Panda et al., 2016b). Memristive devices have been proven to be useful in mimicking spiking neurons, and were used in memristive crossbar structures to speed up the executions of artificial neural networks (Xia et al., 2016, Liu et al., 2015). A more general work by Hu et al. (Hu et al., 2016) have shown that memristive devices are useful in accelerating matrix-vector multiplication in general. In their work they proposed a memristive crossbar array programming for arbitrary matrix values multiplication. This would allow for any machine learning algorithm to be accelerated. Other works focus more on emerging applications such as Resistive RAM (ReRAM or RRAM) to either implement supervised (Chi et al., 2016) or unsupervised (Bojnordi and Ipek, 2016) machine learning algorithms to achieve better energy-performance metrics. These works use metal-oxide ReRAM to store the synaptic weights and improve the efficiency of the matrix dot product, which is in the core of neural computing. ReRAM uses memristors as a memory unit, and recent works show that it could be used as an in-memory computing device (Tang et al., 2015, Song et al., 2017, Hamdioui et al., 2015).

Recent research has shown that adaptive machine learning acceleration is a positive step towards energy efficient computing. The classification system proposed by Venkataramani et al. (Venkataramani et al., 2015b) centers on using increasingly complex classifiers in a pipeline fashion on examples close to the decision boundary. Their approach assumes that complex classifiers will always correctly classify examples, potentially using multiple complex classification functions on inherently noisy examples. That means that if the input "hardness" is very high, all classififiers have to try to identify the labels, before sending the input to the complex classifier. Panda et al. (Panda et al., 2015, Panda et al., 2017) introduce an object detection mechanism using energy-efficient neural computing. The hierarchical framework of classifiers were set up in an increasing level of complexity, making the dynamic trade-off between classification performance and energy efficiency hard. Similarly, the classification system proposed by Park et al. (Park et al., 2015a) uses dynamic threshold adjustment in deep neural networks (DNN) to achieve low power operation. In this work, a "little" DNN is used, and if it fails, a "big" DNN is used, etc. Because of the little-big topology it is not possible to automatically enable the appropriate DNN without running all other DNNs (Sampson, 2015).

The approach proposed in the current work could be viewed as the energy-efficient

learning problem, which in turn is a variation of the problem of learning under testtime budgets (Trapeznikov and Saligrama, 2013, Wang et al., 2014b, Wang et al., 2014a). Here, learning under test-time budgets is a family of approaches that focus on minimizing the costs at test time. In general, these approaches focus on selecting sensors as opposed to energy expenditure and ignore the energy usage associated with selection system. As the main obstacle in the test-time budget problem is the sequential revelation of information, the energy expenditure of the selection system is generally not accounted for. Additionally, many approaches to test-time budgeted learning require design of both the resource allocation as well as the classification functions, preventing the use of optimized modular systems (Xu et al., 2013, Kusner et al., 2014, Nan et al., 2015).

Our work could be contrasted by other works that focus on adaptive classification. In (Judd et al., 2016) authors propose an adaptive neural network that allows onthe-fly trade-off among accuracy, performance, and energy. Similarly Panda et al. (Panda et al., 2016a) focus on dynamic adjustment of computational efforts in neural networks. Unlike these works, our work is not restricted to using one type of machine learning algorithm such as neural networks. We use a notion of a "core" classifier, which we treat as a black box, and use another classifier ("chooser") to achieve the adaptive functionality.

Our work on adaptive systems is closely related to works on learning under testtime budgets (Wang et al., 2014b, Trapeznikov and Saligrama, 2013). Although our work falls in the same category as the works by Venkataramani et al., Panda et al., and Park et al., and we cast the energy efficiency learning problem in a similar fashion, our approach is fundamentally different as it does not ignore the energy usage associated with selecting a classification model. We also don't focus on the sequential learning problem as new information is revealed, but consider a non-sequential selection process and account for the energy consumed in selecting the most energy-efficient classifier.

The contribution of the current work also includes the use of distributed and parallel architectures. Algorithmically, our proposed approach is based on random forest (RF) classifiers (Breiman, 2001). Traditionally, energy efficiency has not been considered when designing random forests; however, recent work has studied learning of the RFs as a subject to test-time constraints (Nan et al., 2015). This approach centers on reducing feature/sensor acquisition cost, however it does not address the system energy constraints. Similar approaches to learning decision rules to minimize error subject to a budget constraint during prediction-time have been proposed (Kusner et al., 2014, Xu et al., 2012, Wang et al., 2015). Although closely related, these approaches also ignore the energy usage and disregard computational cost, making them of limited use in an energy constrained settings.

The state of the art machine learning techniques for image processing, video processing, object recognition, etc. are CNN and DNN, and custom hardware accelerator design have been proposed for the same (Chakradhar et al., 2010, Park et al., 2015b). In addition to that, a variety of techniques including stochastic computing (Kim et al., 2016), dataflow architecture (Chen et al., 2016b, Nowatzki et al., 2015), data reuse (Rahman et al., 2016), custom sparse matrix-vector multiplication (Han et al., 2016) and run-time adaptivity (Venkataramani et al., 2015a, Takhirov et al., 2016) have been adopted to achieve energy-efficient machine learning based operation.

## **1.4** Contributions

In the light of the current developments in the field of energy-efficient computing described in subsection 1.1, and the principles of energy-efficient system design rules laid out by us in subsection 1.2, we developed several mechanisms to achieve better energy-related figures-of-merit in digital design.

The following work was completed leading up to this dissertation:

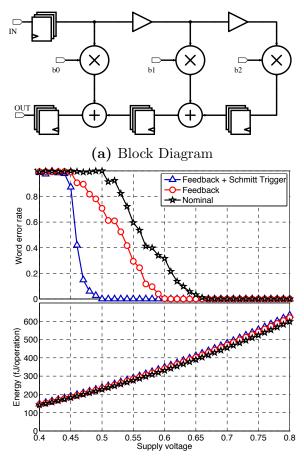

#### Error Avoidance using Feedback Equalization and Schmitt Trigger

In this work we have implemented the feedback equalizer to improve the performance of digital CMOS logic. The improvement is achieved by eliminating the inter-symbol interference (ISI) between successive outputs of the digital logic. Our simulations have shown that at nominal frequency  $f_{nom}$  and 0% error rate the design with the feedback was able to operate at the voltages close to the threshold, while the baseline design (without feedback) saw higher degradation in error rates at voltages other than super-threshold. The results of the work were presented at the  $13^{th}$  International Symposium on Quality Electronic Design 2012. The work has shown that a system with feedback equalization achieves lower energy dissipation while maintaining the error rate and computational performance. For example, in complex circuit blocks like FIR, the use of feedback equalization reduced the energy dissipation by up to 40% when operating at threshold voltage  $V_T = 0.55V$  and nominal frequency of  $f_{nom} = 500 MHz$ . This work was extended to evaluate the use of equalization for entire voltage range above threshold voltage  $V_T$ . The use of equalized FF at above threshold voltage enables an increase in operating frequency (up to 30%) and decrease in the overall energy-delay product (up to 10%) making it possible to operate the digital block at its near-optimal operating point from the EDP perspective over the entire above-threshold voltage range.

#### Decision Feedback Equalization in Pass-Transistor Logic

We proposed a novel differential "equalized pass-transistor-logic" (E-PTL) circuit that enables aggressive voltage scaling to lower energy consumption. Conversely the same approach could be used to enable aggressive overclocking to improve performance at the cost of error rate and/or energy dissipation. In our approach a differential Flip-Flop based Strong-Arm register was modified to accommodate for equalization. For a 16-bit Kogge Stone Adder (KSA), using convex optimization toolbox (CVX Research, Inc., 2012, Grant and Boyd, 2008) the minimum energy design point for a given performance and error rate goal was found and implemented. It was shown that the proposed design reduces energy consumption by up to 30% while operating close to the threshold voltage (a.k.a. near-threshold). The results of the work were published in the IEEE International Symposium on Low Power Electronics and Design in 2013.

#### Machine Learning on a Budget using Adaptive Effort Classifiers

In this work we have investigated adaptive machine learning classification systems and their implementation in digital hardware. The results of this work have shown that adaptive systems can be tuned along the energy efficiency vs. accuracy curve at run-time. Here, the data throughput (number of classifications per unit time) of adaptive system could be readjusted to be anywhere between 0.5x to 3x as compared to non-adaptive approaches. The same way the energy dissipation is adjustable (post-fabrication) from 0.01x to 10x as compared to the non-adaptive classifiers. The readjustment in adaptive classifier is as simple as changing a bias variable to enable more frequent use of one classifier vs. another. This allows for machine learning techniques to be used to adapt to changing environment while maintaining optimal power-performance metrics. This work was released for public in International Symposium on Low Power Electronics and Design 2016, and was further extended by allowing the host CPU report the current environmental conditions which is used as extra information in deciding the best operating mode. This enabled the adaptive classifier to be aware of the current energy reserves, which further optimized the trade-off between energy-dissipation and accuracy rates. This work is being prepared to be submitted to the Transactions on VLSI systems.

#### Distributed Computing using the Field of Groves approach

We also introduced a field of groves (FoG) implementation of random forests (RF) that achieves an accuracy comparable to Convolutional Neural Networks (CNN) and Support Vector Machines (SVM) under tight energy budgets. The FoG architecture takes advantage of a property of random forests that a small portion of the weak classifiers (decision trees) might be sufficient to achieve high statistical performance. By dividing the random forest into smaller forests (Groves), and conditionally executing the rest of the forest, FoG is able to achieve much higher energy efficiency levels for comparable error rates. We also take advantage of the distributed nature of the FoG to achieve high level of parallelism. Our evaluation shows that at maximum achievable accuracies<sup>1</sup> FoG consumes  $\approx 1.48 \times$ ,  $\approx 24 \times$ ,  $\approx 2.5 \times$ , and  $\approx 34.7 \times$  lower energy per classification compared to conventional RF, SVM<sub>*RBF*</sub>, Multi-Layer Perceptron (MLP), and CNN, respectively. FoG is  $6.5 \times$  less energy efficient than SVM<sub>*LR*</sub>, but achieves 18% higher accuracy on average across all considered datasets.

The remainder of the current dissertation is outlined as follows: Chapter 2 provides a detailed analysis of the feedback equalization in CMOS circuits. It also provides a comparison of sequential logic with feedback equalization with Schmitt trigger (FEST) circuit and sequential logic without FEST circuit. Chapter 3 introduces the feedback mechanisms in pass-transistor logic (PTL). It includes the modeling of the energy, performance, and error rate of an equalized system. We also present a comparison of

<sup>&</sup>lt;sup>1</sup>Maximum achievable accuracies are different for all classifiers. Although highly dependent on the datasets, we can assume (with great caution) that RF,  $SVM_{RBF}$ , MLP, and CNN have comparable maximum accuracies; the accuracy of  $SVM_{LR}$  is generally much lower than the other presented algorithms.

static CMOS logic with equalized and non-equalized PTL circuits. Chapter 4 and 5 present novel machine learning architectures and algorithms: an adaptive classification algorithm and evaluation of its implementation in digital hardware and Field of Groves implementation of RF algorithms and the detailed evaluation of its hardware implementation. Chapter 6.2 concludes the current dissertation and discusses the future directions for the completed research.

# Chapter 2

# Error Mitigation in Digital Logic Using Feedback Equalization

## 2.1 Introduction

Inter-symbol Interference (ISI) is a common problem in the long-distance<sup>1</sup> wired digital communication systems, which emerges due to finite rise and fall times of the logical *HIGH* and *LOW*. Parasitic resistances and capacitances in a long wire reshape the square-wave signals of the digital logic to have long "tails". This causes increased delays in the circuit, and conversely limits the minimum operating voltage, as delay in digital CMOS is a function of the supply voltage. A commonly used approach to the timing problems caused by ISI in communication systems is to use equalization.