# BOSTON UNIVERSITY COLLEGE OF ENGINEERING

#### Dissertation

# ENERGY-EFFICIENT ARCHITECTURES FOR CHIP-SCALE NETWORKS AND MEMORY SYSTEMS USING SILICON-PHOTONICS TECHNOLOGY

by

#### ADITYA NARAYAN

B.E., Birla Institute of Technology and Science, Pilani, 2012

M.S., University of Pennsylvania, 2014

Submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

2021

#### Approved by

First Reader

Ayse K. Coskun, Ph.D.

Professor of Electrical and Computer Engineering

Second Reader

Ajay J. Joshi, Ph.D.

Associate Professor of Electrical and Computer Engineering

Third Reader

Pascal Vivet, Ph.D.

Scientific Director of Digital Systems and Integrated Circuits Division, CEA-LIST

Fourth Reader

Milos A. Popovic, Ph.D.

Associate Professor of Electrical and Computer Engineering

Nobody ever figures out what life is all about, and it doesn't matter. Explore the world. Nearly everything is really interesting if you go into it deeply enough. Richard Feynman

#### Acknowledgments

This thesis is the result of a rich blend of mentorship of my research advisors, guidance from my committee members, interesting discussions with collaborators, and the constant support and encouragement from friends and family.

I express my deepest gratitude to my PhD advisor, Prof. Ayse K. Coskun for her guidance and support throughout my PhD studies. Her advising style has helped me evolve into a critical thinker and develop a research aptitude that has greatly influenced me in maturing as a researcher. She has provided me with positive feedback to improve my writing and presentation skills. Our research discussions have been very engaging, and I appreciate the time and effort she put in my work. Her constant encouragement has enabled me to develop my ideas into research publications and deliver well-received talks at conferences.

I want to thank my PhD co-advisor, Prof. Ajay Joshi for his valuable feedback and suggestions on my research. I enjoyed the lively discussions and brainstorming sessions during my work on optically-controlled phase change memory. His inputs on addressing a problem from different angles has greatly shaped my way of thinking about a problem.

I want to extend my gratitude to Dr. Pascal Vivet, who was my manager at CEA-Leti during my internship. He and his team at CEA-Leti made me extremely comfortable during my stay in France and ensured a great educational experience. His feedback on thermal modeling and characterization of 2.5D and 3D chips improved my understanding of thermal implications in manycore chips. I would also like to acknowledge the rest of my committee members, Prof. Milos Popovic and Prof. Martin Herbordt, who provided insightful comments and feedback that helped me improve my dissertation significantly.

I want to extend special thanks to Dr. Tiansheng Zhang for being a great mentor

during my initial PhD years, and a good friend with whom I exchanged many interesting discussions. I also acknowledge Yvain Thonnart, who was my mentor during my internship at CEA-Leti. He has been instrumental in my understanding of silicon-photonic link technology. He patiently explained the operation of optical devices, and provided essential feedback on the device-level implications of my architectural and system proposals.

I owe many thanks to my collaborators and co-authors for our joint productive work during my PhD: Prof. Satish Narayanasamy and Dr. Shaizeen Aga from University of Michigan, Ann Arbor; Dr. Cesar Fuguet Tortolero from CEA-Leti; Prof. Andrew Kahng and Dr. Vaishnav Srinivas from University of California, San Diego; Dr. Yenai Ma and Furkan Eris from Boston University.

I thank my good friend, fellow PhD candidate and my flatmate, Soham Sinha, with whom I have shared both the fun moments and the struggles during my PhD years. I thoroughly enjoyed all our technical discussions on computer architecture and operating systems, and on various other topics including movies, politics, and economics. I am very thankful to all my lab mates and colleagues from PeacLab, ICSG group, CAADLab, and SeclaBU who made my PhD cheerful and memorable.

I want to extend sincere thanks to my parents, my brother, my parents in-law, and my brother-in-law, whose constant support has guided me through my PhD journey. Finally, I thank my wife, Sravya Kotaru, who has been my true source of inspiration to pursue a PhD. Her passion for science fueled a desire in me to explore the beautiful world of computing systems ever so deeply. She has stood by me through the difficult ordeals, always cheered me, and brought out the best in me. It would also be remiss of me not to mention her editing skills that have made me a better writer.

The research that forms the basis of this dissertation has been partially funded by NSF and the CARNOT Institute in France. The contents of Chapter 3 contains reprints from the papers Aditya Narayan, Yvain Thonnart, Pascal Vivet, Cesar Fuguet Tortolero, and Ayse K. Coskun, "WAVES: Wavelength selection for Power-efficient 2.5D-integrated Photonic NoCs", in Design, Automation & Test in Europe Conference & Exhibition (DATE), 2019; Aditya Narayan, Yvain Thonnart, Pascal Vivet, and Ayse K. Coskun, "PROWAVES: Proactive Runtime Wavelength Selection for Energy-efficient Photonic NoCs", in Transactions on Computer-Aided Design (TCAD), 2020; Aditya Narayan, Yvain Thonnart, Pascal Vivet, Ajay Joshi, and Ayse K. Coskun, "System-level Evaluation of Chip-Scale Silicon Photonic Networks for Emerging Data-Intensive Applications", in Design, Automation & Test in Europe Conference & Exhibition (DATE), 2020; and Aditya Narayan, Ajay Joshi, and Ayse K. Coskun, "Bandwidth Allocation in Silicon-Photonic Networks Using Application Instrumentation", in High Performance Extreme Computing Conference (HPEC), 2020.

The contents of Chapter 5 are part reprints of the paper Aditya Narayan, Tiansheng Zhang, Shaizeen Aga, Satish Narayanasamy, and Ayse Coskun, "MOCA: Memory Object Classification and Allocation in Heterogeneous Memory Systems", in International Parallel and Distributed Processing Symposium (IPDPS), 2018.

# ENERGY-EFFICIENT ARCHITECTURES FOR CHIP-SCALE NETWORKS AND MEMORY SYSTEMS USING SILICON-PHOTONICS TECHNOLOGY

#### ADITYA NARAYAN

Boston University, College of Engineering, 2021

Major Professors: Ayse K. Coskun, Ph.D.

Professor of Electrical and Computer Engineering

Ajay Joshi, Ph.D.

Associate Professor of Electrical and Computer

Engineering

#### ABSTRACT

Today's supercomputers and cloud systems run many data-centric applications such as machine learning, graph algorithms, and cognitive processing, which have large data footprints and complex data access patterns. With computational capacity of large-scale systems projected to rise up to 50GFLOPS/W, the target energy-per-bit budget for data movement is expected to reach as low as 0.1pJ/bit, assuming 200bits/FLOP for data transfers. This tight energy budget impacts the design of both chip-scale networks and main memory systems. Conventional electrical links used in chip-scale networks (0.5-3pJ/bit) and DRAM systems used in main memory (> 30pJ/bit) fail to provide sustained performance at low energy budgets. This thesis builds on the promising research on silicon-photonic technology to design system architectures and system management policies for chip-scale networks and main memory systems. The adoption of silicon-photonic links as chip-scale networks, however,

is hampered by the high sensitivity of optical devices towards thermal and process variations. These device sensitivities result in high power overheads at high-speed communications. Moreover, applications differ in their resource utilization, resulting in application-specific thermal profiles and bandwidth needs. Similarly, optically-controlled memory systems designed using conventional electrical-based architectures require additional circuitry for electrical-to-optical and optical-to-electrical conversions within memory. These conversions increase the energy and latency per memory access. Due to these issues, chip-scale networks and memory systems designed using silicon-photonics technology leave much of their benefits underutilized.

This thesis argues for the need to rearchitect memory systems and redesign network management policies such that they are aware of the application variability and the underlying device characteristics of silicon-photonic technology. We claim that such a cross-layer design enables a high-throughput and energy-efficient unified silicon-photonic link and main memory system. This thesis undertakes the crosslayer design with silicon-photonic technology in two fronts. First, we study the varying network bandwidth requirements across different applications and also within a given application. To address this variability, we develop bandwidth allocation policies that account for application needs and device sensitivities to ensure powerefficient operation of silicon-photonic links. Second, we design a novel architecture of an optically-controlled main memory system that is directly interfaced with siliconphotonic links using a novel read and write access protocol. Such a system ensures low-energy and high-throughput access from the processor to a high-density memory. To further address the diversity in application memory characteristics, we explore heterogeneous memory systems with multiple memory modules that provide varied power-performance benefits. We design a memory management policy for such systems that allocates pages at the granularity of memory objects within an application.

# Contents

| 1 | Intr | oduct   | ion                                                | 1  |

|---|------|---------|----------------------------------------------------|----|

|   | 1.1  | Design  | ning Energy-efficient Silicon-Photonic Links       | 4  |

|   | 1.2  | Design  | ning Scalable and High-throughput Main Memory      | 6  |

|   | 1.3  | Disser  | rtation Organization                               | 9  |

| 2 | Bac  | kgrou   | nd and Context                                     | 10 |

|   | 2.1  | 2.5D I  | Manycore Computing Systems                         | 10 |

|   |      | 2.1.1   | Chip-scale Networks in 2.5D Manycore Systems       | 11 |

|   |      | 2.1.2   | Main Memory in 2.5D Manycore Systems               | 12 |

|   | 2.2  | Silicon | n-Photonic Link Technology                         | 13 |

|   |      | 2.2.1   | Operation of WDM Silicon-Photonic Link             | 13 |

|   |      | 2.2.2   | Device-level Characteristics                       | 15 |

|   |      | 2.2.3   | Thermal Management in Silicon-Photonic Links       | 16 |

|   |      | 2.2.4   | Bandwidth Allocation in Silicon-Photonic Links     | 19 |

|   | 2.3  | Optica  | ally-controlled Phase Change Memory                | 20 |

|   |      | 2.3.1   | Properties of Phase Change Materials               | 21 |

|   |      | 2.3.2   | Issues with an Electrically-controlled PCM Cell    | 23 |

|   |      | 2.3.3   | Operation of an Optically-controlled PCM Cell      | 24 |

|   |      | 2.3.4   | High-throughput Access with Silicon-Photonic Links | 26 |

|   | 2.4  | Memo    | bry Management in Heterogeneous Memory Systems     | 26 |

|   |      | 2.4.1   | Heterogeneous Memory Systems                       | 27 |

|   |      | 2.4.2   | Page Allocation in Heterogeneous Memory Systems    | 28 |

|   | 2.5 | Distin  | guishing Aspects of this Thesis                                              | 31 |

|---|-----|---------|------------------------------------------------------------------------------|----|

| 3 | Sys | tem-le  | vel Management of Silicon-Photonic Links                                     | 33 |

|   | 3.1 | 2.5D I  | Manycore System with Silicon-Photonic Links                                  | 34 |

|   | 3.2 | Cross-  | -layer Simulation Framework for Silicon-Photonic                             |    |

|   |     | Links   |                                                                              | 37 |

|   |     | 3.2.1   | Device-level Modeling                                                        | 37 |

|   |     | 3.2.2   | Architecture-level Modeling                                                  | 39 |

|   |     | 3.2.3   | System-level Performance, Power and Thermal Modeling $\ .\ .\ .$             | 41 |

|   | 3.3 | Wavel   | length Selection for Energy-efficient Silicon-Photonic Links                 | 44 |

|   |     | 3.3.1   | Static Policy: SO-WAVES                                                      | 45 |

|   |     | 3.3.2   | Dynamic Policy with Time-series Prediction: $\ensuremath{\textit{PROWAVES}}$ | 46 |

|   |     | 3.3.3   | MRR Locking with Wavelength Selection                                        | 49 |

|   |     | 3.3.4   | Hardware Cost of Wavelength Selection                                        | 51 |

|   |     | 3.3.5   | Experimental Results and Analysis                                            | 53 |

|   | 3.4 | Silicon | n-Photonic Links for Graph Workloads                                         | 61 |

|   |     | 3.4.1   | Evaluation of Wavelength Selection for Graph Workloads                       | 62 |

|   |     | 3.4.2   | Architectural Exploration for Graph Workloads                                | 63 |

|   | 3.5 | Wavel   | length Selection using Application Instrumentation                           | 66 |

|   |     | 3.5.1   | Application Instrumentation                                                  | 67 |

|   |     | 3.5.2   | Simulation Results and Analysis                                              | 69 |

|   | 3.6 | Chapt   | ser Summary                                                                  | 70 |

| 4 | Arc | hitecti | ing Optically-controlled Phase Change Memory                                 | 72 |

|   | 4.1 | Challe  | enges with Adapting DRAM Architecture for OPCM                               | 73 |

|   | 4.2 | COSM    | MOS: OPCM Memory System with Silicon-Photonic links                          | 76 |

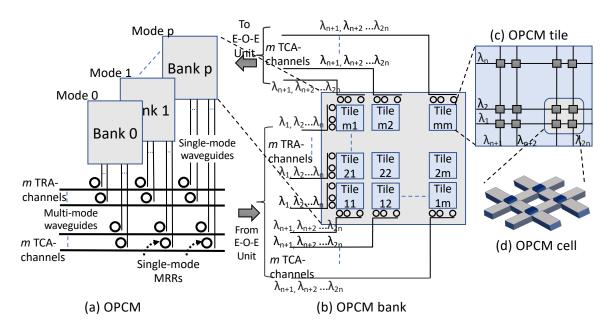

|   | 4.3 | OPCN    | M Array Microarchitecture in COSMOS                                          | 78 |

|   |     | 131     | OPCM Tile                                                                    | 70 |

|   |     | 4.3.2  | OPCM Bank                                      | 80  |

|---|-----|--------|------------------------------------------------|-----|

|   |     | 4.3.3  | Multi-banked OPCM Array                        | 80  |

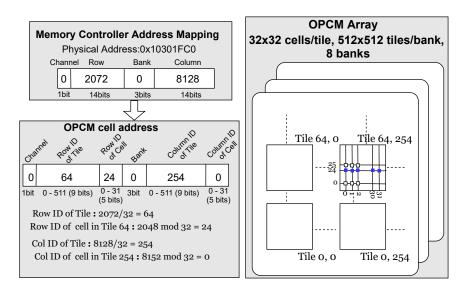

|   |     | 4.3.4  | Address Mapping in $COSMOS$                    | 81  |

|   | 4.4 | Access | s Protocol in COSMOS                           | 82  |

|   |     | 4.4.1  | Writing a Cache Line to OPCM Array             | 82  |

|   |     | 4.4.2  | Reading a Cache Line from OPCM Array           | 83  |

|   |     | 4.4.3  | Opportunistic Writeback for Read Operation     | 84  |

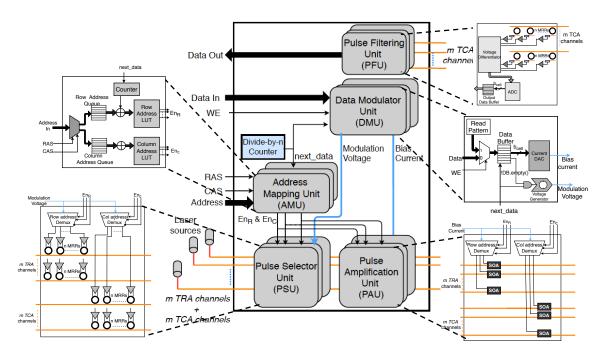

|   | 4.5 | E-O-E  | Control Unit Architecture                      | 85  |

|   |     | 4.5.1  | Data Modulation Unit (DMU)                     | 85  |

|   |     | 4.5.2  | Address Mapping Unit (AMU)                     | 87  |

|   |     | 4.5.3  | Pulse Selector Unit (PSU)                      | 87  |

|   |     | 4.5.4  | Pulse Amplification Unit (PAU)                 | 88  |

|   |     | 4.5.5  | Pulse Filtering Unit (PFU)                     | 88  |

|   | 4.6 | Exper  | imental Evaluation and Analysis                | 88  |

|   |     | 4.6.1  | Evaluation Methodology                         | 88  |

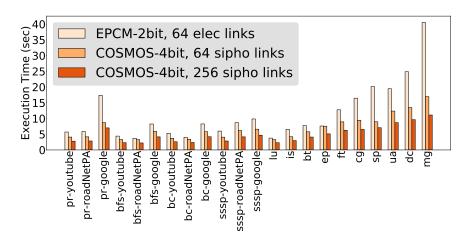

|   |     | 4.6.2  | Performance Comparison with EPCM               | 90  |

|   |     | 4.6.3  | Sensitivity Analysis with Optical Parameters   | 94  |

|   |     | 4.6.4  | OPCM Endurance Analysis                        | 97  |

|   |     | 4.6.5  | Area Efficiency of COSMOS                      | 98  |

|   |     | 4.6.6  | Performance and Energy Comparison with DRAM    | 99  |

|   | 4.7 | Chapt  | er Summary                                     | 101 |

| 5 | Mei | mory I | Management in Heterogeneous Memory Systems     | 103 |

|   | 5.1 | Memo   | ry Access Characteristics of Heap Objects      | 104 |

|   | 5.2 | MOC    | 4: Memory Object Classification and Allocation | 105 |

|   |     | 5.2.1  | Memory Object Naming                           | 106 |

|   |     | 5.2.2  | Statistics Collection                          | 107 |

|    |                      | 5.2.3  | Memory Object Classification                            | 107 |

|----|----------------------|--------|---------------------------------------------------------|-----|

|    |                      | 5.2.4  | Binary Instrumentation                                  | 108 |

|    |                      | 5.2.5  | Page Allocation                                         | 108 |

|    | 5.3                  | Impler | mentation of MOCA                                       | 109 |

|    |                      | 5.3.1  | Offline Profiling and Classification                    | 110 |

|    |                      | 5.3.2  | Runtime Page Allocation                                 | 110 |

|    |                      | 5.3.3  | Overheads of $MOCA$                                     | 111 |

|    | 5.4                  | Experi | imental Evaluation and Analysis                         | 111 |

|    |                      | 5.4.1  | Simulation Framework                                    | 111 |

|    |                      | 5.4.2  | Performance and Energy Benefits for Single-core Systems | 114 |

|    |                      | 5.4.3  | Performance and Energy Benefits for Multicore Systems   | 115 |

|    |                      | 5.4.4  | Classifying Stack Data and Code Segment                 | 116 |

|    | 5.5                  | Chapt  | er Summary                                              | 116 |

| 6  | Con                  | clusio | ns and Future Directions                                | 118 |

|    | 6.1                  | Summ   | ary of Thesis Contributions                             | 118 |

|    | 6.2                  | Future | e Research Directions                                   | 122 |

|    |                      | 6.2.1  | Designing Efficient Silicon-Photonic Links              | 122 |

|    |                      | 6.2.2  | Architectural Opportunities with $COSMOS$               | 124 |

|    |                      | 6.2.3  | Memory Management in Heterogeneous Memory Systems       | 128 |

| Re | efere                | nces   |                                                         | 131 |

| Cı | Curriculum Vitae 152 |        |                                                         |     |

# List of Tables

| 3.1 | Notations used in modeling of silicon-photonic links                  | 37  |

|-----|-----------------------------------------------------------------------|-----|

| 3.2 | Power consumption of a laser source and the different active elements |     |

|     | in TxRx chiplet for E-O-E conversion (Polster et al., 2016)           | 40  |

| 3.3 | Description of applications from the HPC and Graph Benchmarks used    |     |

|     | in system simulations of silicon-photonic links                       | 42  |

| 3.4 | Material properties and dimensions of different layers in $POPSTAR$ . | 44  |

| 3.5 | Summary of modeling parameters and results of different wavelength    |     |

|     | selection policies                                                    | 61  |

| 4.1 | Architectural details of the computing system for $COSMOS$ evaluation | 89  |

| 4.2 | Optical power budget for $2GB$ $COSMOS$ . The table shows optical     |     |

|     | power losses and SOA gain along the optical path from laser source    |     |

|     | to OPCM cells                                                         | 92  |

| 4.3 | Energy-per-bit for read and write operations in EPCM and $COSMOS$     |     |

|     | with 4-bit OPCM cells                                                 | 94  |

| 4.4 | Bit density $(bits/mm^2)$ of different memory technologies            | 99  |

| 5.1 | Microarchitectural details of AMD Magny Cours processor used in       |     |

|     | Gem5 simulations                                                      | 112 |

# List of Figures

| 1.1 | Energy-per-bit consumption in silicon-photonic links with increasing          |    |

|-----|-------------------------------------------------------------------------------|----|

|     | data rate (Bahadori et al., 2017b).                                           | 5  |

| 1.2 | (a) DRAM technology scaling from 2005 to 2018 adapted from (Bergal,           |    |

|     | 2019). (b) Price per GB of DRAM from 1991 to 2019, according to               |    |

|     | the Objective Analysis graph (Hertz, 2021)                                    | 7  |

| 2.1 | An example WDM silicon-photonic link. An off-chip laser emits 3 different     |    |

|     | optical signals. 3 MRRs at Tx modulate the data onto these 3 optical signals, |    |

|     | and 3 MRRs at Rx filter out the data from these 3 optical signals. $\dots$    | 14 |

| 2.2 | MRR sensitivity to TV and PV. MRRs are designed to resonate at                |    |

|     | peak resonant wavelength of an optical signal. TV and PV induces              |    |

|     | shifts in the MRR resonant wavelength. The MRRs are supplied with             |    |

|     | heating power to tune back to laser wavelength                                | 15 |

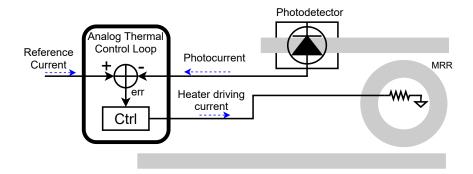

| 2.3 | An analog thermal control loop compares the photocurrent with a reference     |    |

|     | current and drives a heater current to thermally tune an MRR                  | 17 |

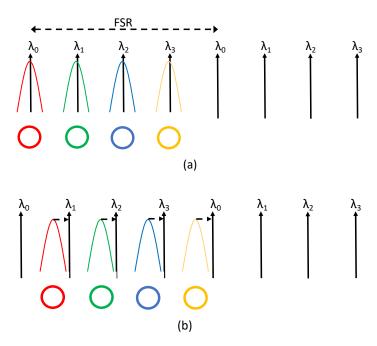

| 2.4 | (a) The thermal control loop maintains the 4 MRRs at the resonant             |    |

|     | wavelength of 4 optical signals. (b) A large TV induces a high MRR            |    |

|     | resonance shift, and the thermal control loop performs thermal remap-         |    |

|     | ping to a new set of optical signals                                          | 18 |

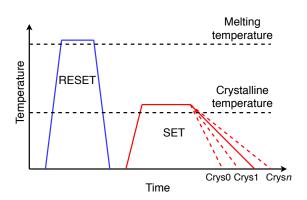

| 2.5 | Operating principle of a GST element. <b>RESET:</b> The GST element is                                                   |    |

|-----|--------------------------------------------------------------------------------------------------------------------------|----|

|     | heated to its melting temperature and rapidly cooled to change to a-                                                     |    |

|     | GST. <b>SET:</b> The GST element is heated to its crystalline temperature                                                |    |

|     | and gradually cooled to change to c-GST                                                                                  | 21 |

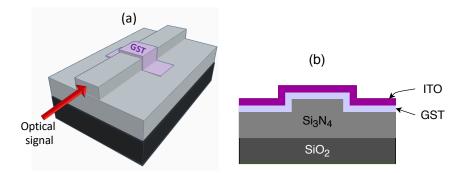

| 2.6 | (a) 3D view of a GST-based PCM cell that is controlled using opti-                                                       |    |

|     | cal signals. (b) Cross-sectional view of OPCM cell, where the GST                                                        |    |

|     | deposited on a $Si_3N_4$ waveguide                                                                                       | 24 |

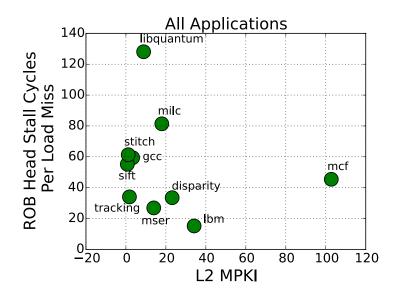

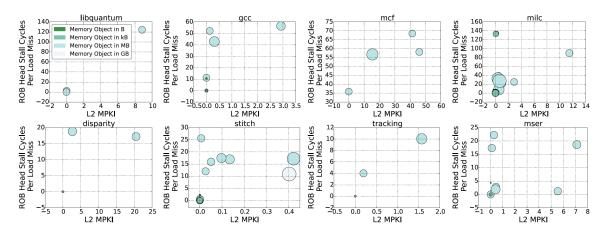

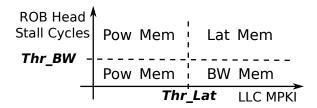

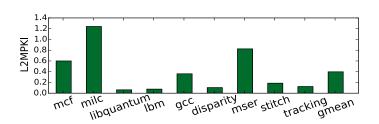

| 2.7 | Memory access behavior of selected applications from SPEC CPU2006                                                        |    |

|     | and SDVBS benchmarks. A high L2 MPKI indicates that the appli-                                                           |    |

|     | cation is memory-intensive. A low number of ROB stall cycles for a                                                       |    |

|     | memory-intensive application implies high memory-level parallelism. $\boldsymbol{.}$                                     | 29 |

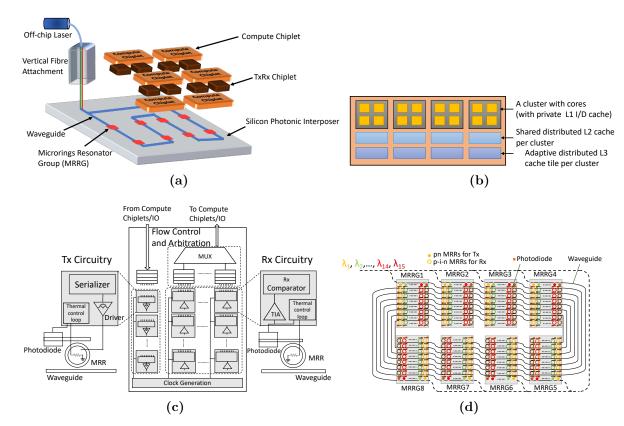

| 3.1 | POPSTAR architecture. (a) 2.5D manycore chip with six compute                                                            |    |

|     | chiplets and eight TxRx chiplets that are integrated on a photonic in-                                                   |    |

|     | terposer. (b) Architecture of a compute chiplet, with four clusters and                                                  |    |

|     | four cores per cluster. (c) Architecture of a TxRx chiplet, with cir-                                                    |    |

|     | cuitry for data modulation, data filtering, flow control and arbitration.                                                |    |

|     | (d) SWMR routing of optical channels and MRRG assignment. $\ \ldots \ \ldots$                                            | 34 |

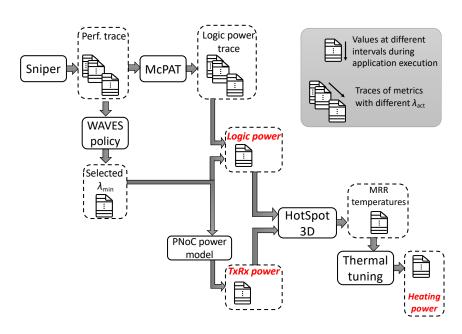

| 3.2 | Simulation framework for modeling performance, power and tempera-                                                        |    |

|     | ture of <i>POPSTAR</i>                                                                                                   | 41 |

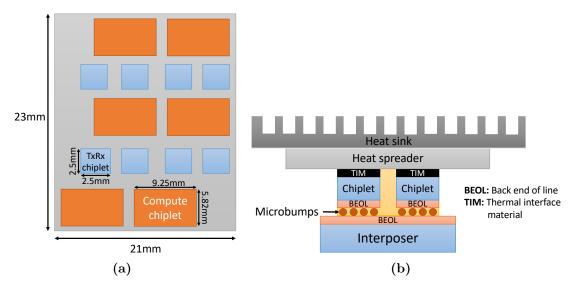

| 3.3 | (a) Layout of $POPSTAR$ along with the dimensions of compute and                                                         |    |

|     | $\operatorname{TxRx}$ chiplets, (b) $\operatorname{Cross-sectional}$ view of $\operatorname{POPSTAR}$ with the different |    |

|     | layers in 2.5D integration                                                                                               | 43 |

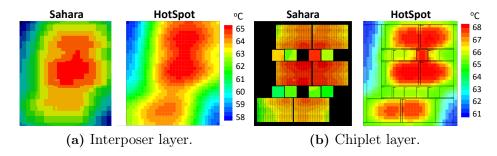

| 3.4 | Thermal map of $POPSTAR$ in Sahara tool (Parry and Wang, 2018) and                                                       |    |

|     | HotSpot tool (Skadron et al., 2003)                                                                                      | 44 |

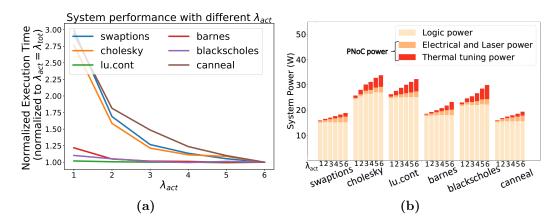

| 3.5 | (a) Normalized execution time and (b) system power breakdown with dif-                                                   |    |

|     | ferent number of active optical channels $(\lambda_{act})$ in the silicon-photonic link.                                 | 45 |

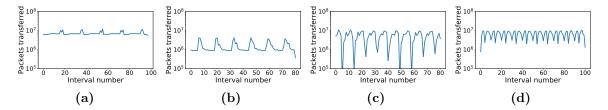

| 3.6  | Inter-chiplet packets transferred during application execution for (a) $bt$ , (b)                    |    |

|------|------------------------------------------------------------------------------------------------------|----|

|      | ep, (c) $shock$ , and (d) $lu$ . Applications have phases where a higher number of                   |    |

|      | packets are transferred compared to other phases and these phases exhibit                            |    |

|      | periodic behavior                                                                                    | 47 |

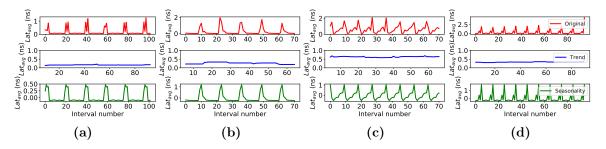

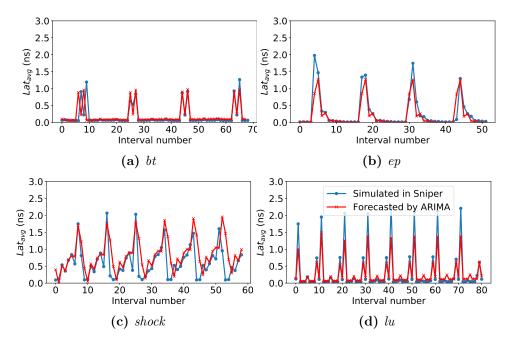

| 3.7  | Trends and seasonality in the $Lat_{avg}$ time series for (a) $bt$ , (b) $ep$ , (c) $shock$ ,        |    |

|      | and (d) lu                                                                                           | 47 |

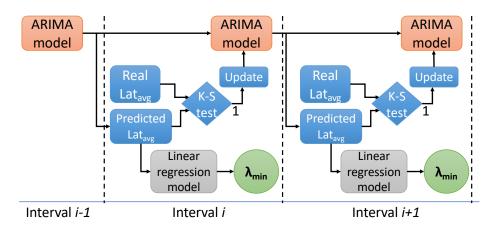

| 3.8  | Flow of $PROWAVES$ . Every interval, the ARIMA model forecasts the $Lat_{avg}$ .                     |    |

|      | The linear regression model selects the $\lambda_{min}$ from the forecasted $Lat_{avg}$ . A          |    |

|      | K-S test is applied to update the ARIMA model in case of divergence                                  | 48 |

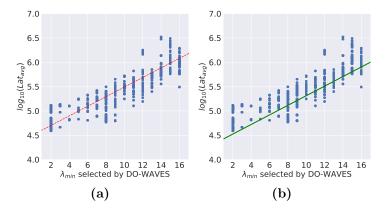

| 3.9  | Scatterplots of $Lat_{avg}$ vs $\lambda_{min}$ selected by $DO\text{-}WAVES$ for $L_{thr}=5\%$ . (a) |    |

|      | shows the line with least mean square error, (b) shows the line such that                            |    |

|      | 90% of the points are above the line                                                                 | 49 |

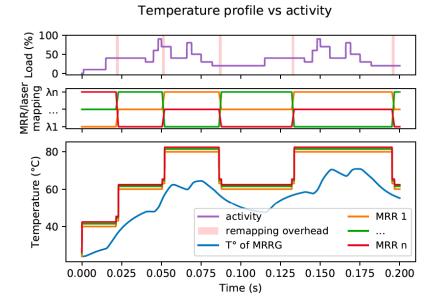

| 3.10 | Thermal remapping of MRRs to $\lambda_{act}$ . As chip activity varies during execu-                 |    |

|      | tion, the thermal profile of MRRGs varies, causing MRRs within an MRRG                               |    |

|      | to map to different optical channels                                                                 | 50 |

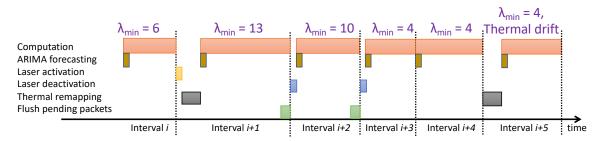

| 3.11 | Latency overhead of <i>PROWAVES</i> . Increasing $\lambda_{min}$ involves laser activation           |    |

|      | $(2ns)$ and thermal remapping $(100\mu s)$ . Decreasing $\lambda_{min}$ involves laser de-           |    |

|      | activation $(2ns)$ and flushing pending packets $(100ns - 1\mu s)$ , both of which                   |    |

|      | are hidden in the computation time                                                                   | 52 |

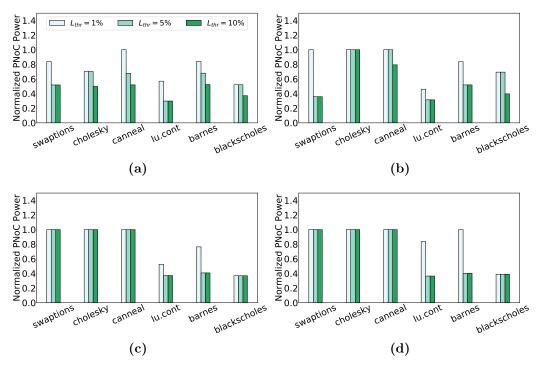

| 3.12 | Photonic power consumption of $POPSTAR$ with $SO\text{-}WAVES$ for (a) 25%                           |    |

|      | system utilization, (b) $50\%$ system utilization, (c) $75\%$ system utilization,                    |    |

|      | and (d) 100% system utilization                                                                      | 54 |

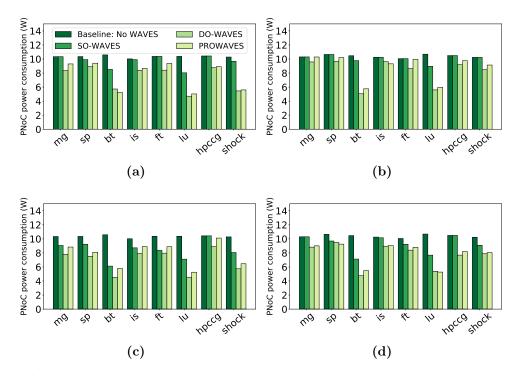

| 3.13 | Photonic power consumption of $POPSTAR$ with different WAVES policies                                |    |

|      | for (a) 50% system utilization, $L_{thr}=1\%,$ (b) 100% system utilization,                          |    |

|      | $L_{thr}=1\%,$ (c) 50% system utilization, $L_{thr}=5\%,$ and (d) 100% system                        |    |

|      | utilization $L_{\perp} = 507$                                                                        | 55 |

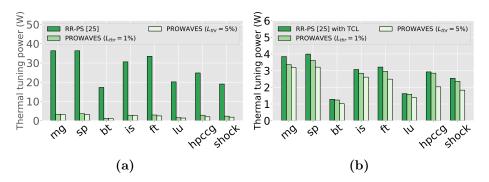

| 3.14 | Thermal tuning power comparison between $RR\text{-}PS$ and $PROWAVES$ . In (a),                                               |    |

|------|-------------------------------------------------------------------------------------------------------------------------------|----|

|      | $RR	ext{-}PS$ does not model thermal control loop that enables thermal remapping,                                             |    |

|      | as initially proposed in (Van Winkle et al., 2018). In (b), $RR\text{-}PS$ is updated                                         |    |

|      | to include a thermal control loop model as $PROWAVES$ , but does not select                                                   |    |

|      | best $\lambda_{min}$ that accounts for PV                                                                                     | 57 |

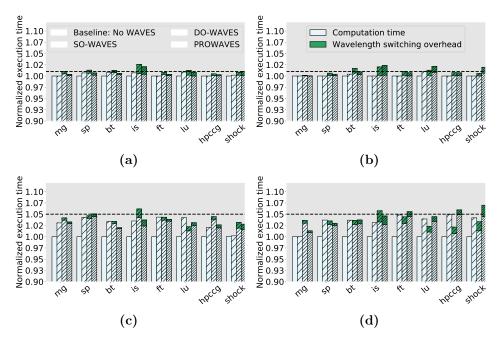

| 3.15 | Normalized execution time and wavelength switching overhead with different                                                    |    |

|      | WAVES policies for (a) 50% utilization, $L_{thr}=1\%$ , (b) 100% utilization,                                                 |    |

|      | $L_{thr}=1\%,$ (c) 50% utilization, $L_{thr}=5\%,$ and (d) 100% utilization, $L_{thr}=$                                       |    |

|      | 5%. The dotted line indicates $L_{thr}$                                                                                       | 58 |

| 3.16 | Comparison of $\lambda_{min}$ selected by DO-WAVES and PROWAVES with $L_{thr}=$                                               |    |

|      | $5\%$ for applications (a) $\mathit{bt},$ (b) $\mathit{is},$ (c) $\mathit{sp},$ and (d) $\mathit{mg}.$ During periods of high |    |

|      | bandwidth needs, a higher $\lambda_{min}$ is activated, and during periods of lower                                           |    |

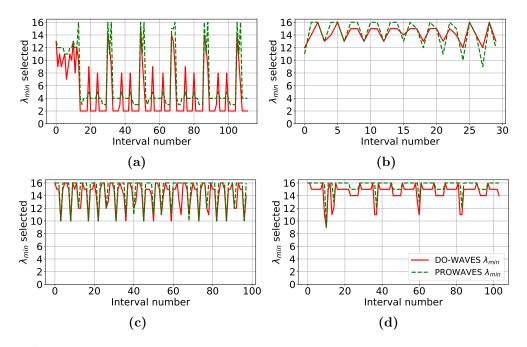

|      | bandwidth needs, a lower $\lambda_{min}$ is activated                                                                         | 59 |

| 3.17 | $Lat_{avg}$ values from Sniper simulations and forecasted $Lat_{avg}$ values using                                            |    |

|      | ARIMA model for applications (a) $bt$ , (b) $ep$ , (c) $shock$ , and (d) $lu$ running                                         |    |

|      | 96 threads                                                                                                                    | 60 |

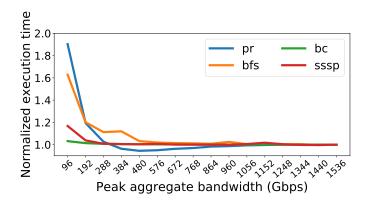

| 3.18 | Normalized performance with increasing inter-chiplet bandwidth for                                                            |    |

|      | graph applications on Google web graph. The performance is normal-                                                            |    |

|      | ized to the performance with peak bandwidth of $1.536Tbps.$                                                                   | 63 |

| 3.19 | Photonic power consumption with $SO\text{-}WAVES$ for graph applications                                                      |    |

|      | on three different datasets. Power numbers are normalized to baseline                                                         |    |

|      | case where all laser wavelengths are activated                                                                                | 63 |

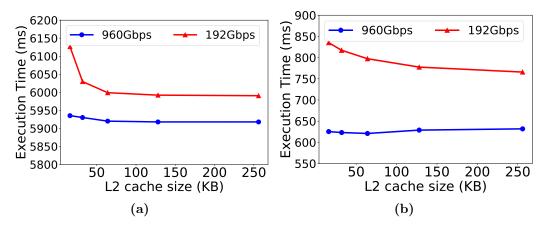

| 3.20 | Performance of (a) $bc$ and (b) $pr$ with different inter-chiplet bandwidth,                                                  |    |

|      | when executed on 2 systems with different L2 cache sizes                                                                      | 64 |

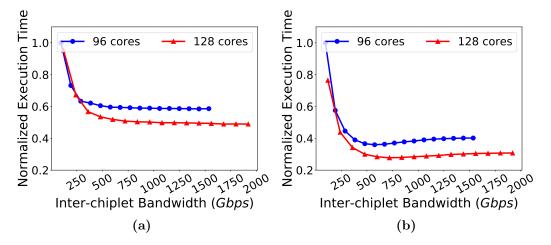

| 3.21 | Performance of (a) $\it bfs$ and (b) $\it pr$ with different inter-chiplet band-                                              |    |

|      | width when executed on 2 systems with different core counts                                                                   | 65 |

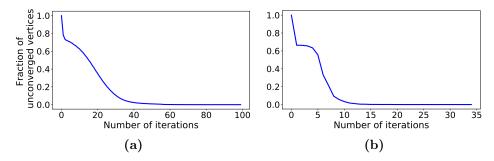

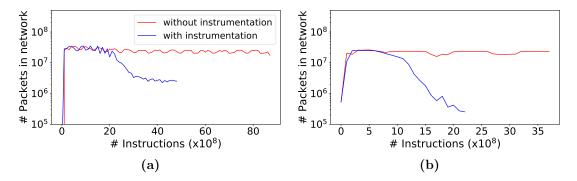

| 3.22 | Number of unconverged vertices with iterations for PageRank on (a)             |    |

|------|--------------------------------------------------------------------------------|----|

|      | Google webgraph, (b) Kronecker graph with $2^{18}$ vertices                    | 67 |

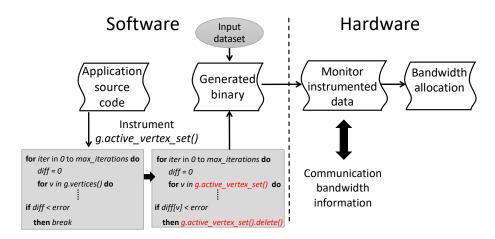

| 3.23 | Framework of bandwidth allocation using application instrumentation.           | 68 |

| 3.24 | Number of packets transferred in the photonic network during applica-          |    |

|      | tion execution for (a) Google webgraph and (b) Kronecker graph with            |    |

|      | $2^{18}$ vertices                                                              | 69 |

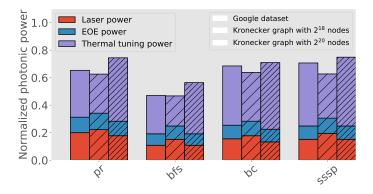

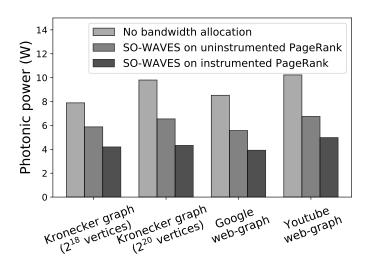

| 3.25 | Photonic power savings using application instrumentation-assisted band-        |    |

|      | width allocation                                                               | 70 |

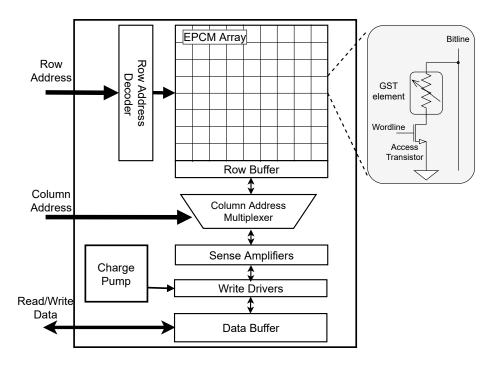

| 4.1  | A typical EPCM architecture (Lee et al., 2009)                                 | 73 |

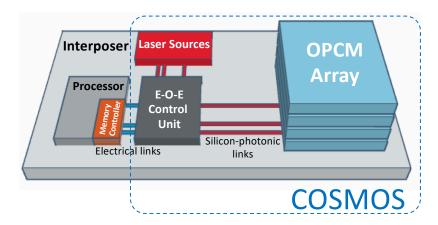

| 4.2  | Overview of a 2.5D integrated computing system with $\it COSMOS$ as the        |    |

|      | main memory                                                                    | 76 |

| 4.3  | COSMOS architecture. (a) A multibanked-OPCM uses $p$ optical modes             |    |

|      | to access $p$ banks. (b) An OPCM bank is an array of $m \times m$ tiles. Every |    |

|      | tile is accessed by a TRA-channel and a TCA-channel, each channel              |    |

|      | containing $n$ optical signals. (c) An OPCM tile is an array of $n \times n$   |    |

|      | cells. Every cell is accessed by a unique pair of optical signals. (d)         |    |

|      | OPCM cells are placed at every waveguide crossing                              | 78 |

| 4.4  | Mapping of the physical address in the memory controller to the phys-          |    |

|      | ical location of the OPCM cell in the OPCM array                               | 81 |

| 4.5  | (a) E-O-E control unit design. DMU: Generates the modulation volt-             |    |

|      | age and the bias current corresponding to read/write data. AMU: De-            |    |

|      | termines optical signals that correspond to read/write address. PSU:           |    |

|      | Selects the optical signals. PAU: Amplifies the optical signals using          |    |

|      | the bias current. PFU: Filters the optical signals to read cell data           | 86 |

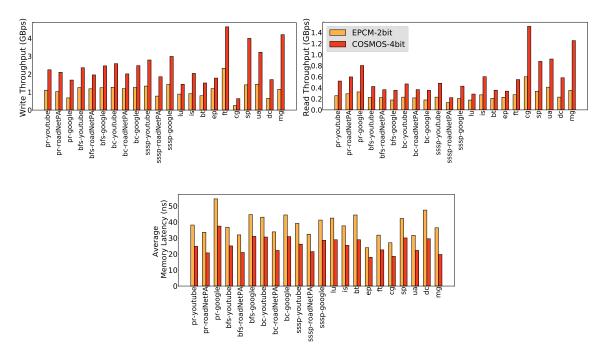

| 4.6  | Performance comparison of COSMOS with EPCM                                     | 90 |

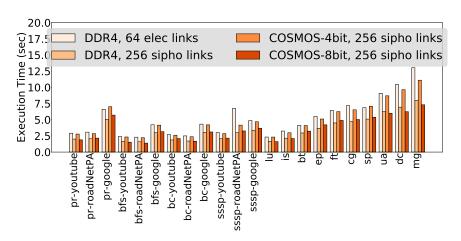

| 4.7  | Comparison of EPCM-2bit with 64 electrical links and COSMOS-4bit         |     |

|------|--------------------------------------------------------------------------|-----|

|      | in terms of (a) write throughput, (b) read throughput, (c) average       |     |

|      | memory latency                                                           | 91  |

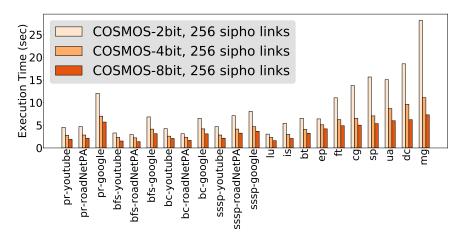

| 4.8  | Performance comparison of $COSMOS$ with different MLC OPCM cells.        | 95  |

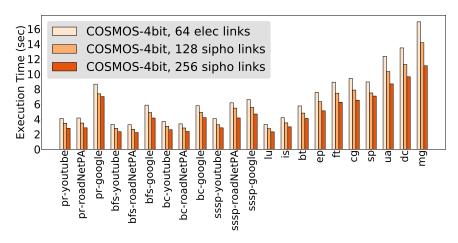

| 4.9  | Performance comparison of COSMOS with different number of optical        |     |

|      | channels in the silicon-photonic link.                                   | 95  |

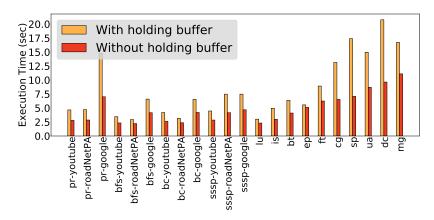

| 4.10 | Performance comparison of $COSMOS$ with and without holding buffer       |     |

|      | for opportunistic writeback in read operation                            | 96  |

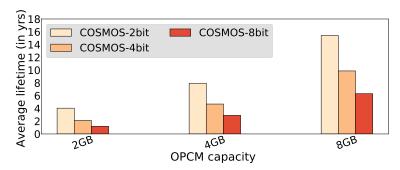

| 4.11 | Average lifetime (in years) of $COSMOS$ with different MLC capabilities  |     |

|      | for different memory capacities                                          | 98  |

| 4.12 | Performance comparison of DDR4 and $COSMOS$ with OPCM-4bit array.        | 100 |

| 5.1  | Access intensity and memory-level parallelism of heap memory objects for |     |

|      | applications from SPEC CPU2006 and SDVBS benchmarks                      | 104 |

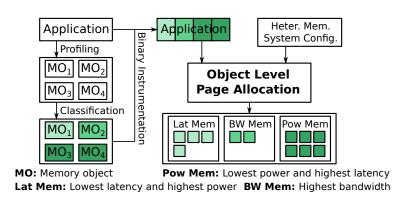

| 5.2  | The flow of $MOCA$ . The profiling stage uniquely names memory objects   |     |

|      | and characterizes the memory intensity and memory level parallelism.     |     |

|      | Classification stage uses this information to classify objects. At run-  |     |

|      | time, each memory object is allocated with pages from the best-fitting   |     |

|      | memory module based on object's type                                     | 105 |

| 5.3  | An example of memory object naming convention                            | 106 |

| 5.4  | Classification of memory objects into different types based on latency   |     |

|      | and bandwidth thresholds                                                 | 108 |

| 5.5  | Mapping of virtual pages in the heap space to multiple memory mod-       |     |

|      | ules in physical memory in MOCA                                          | 109 |

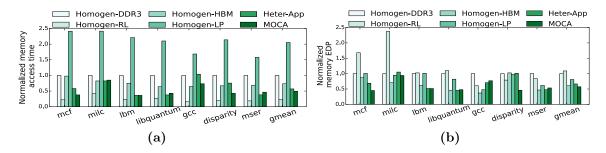

| 5.6  | (a) Memory performance in access time, and (b) memory energy effi-       |     |

|      | ciency in EDP of homogeneous and heterogeneous memory systems for        |     |

|      | single-program workloads                                                 | 114 |

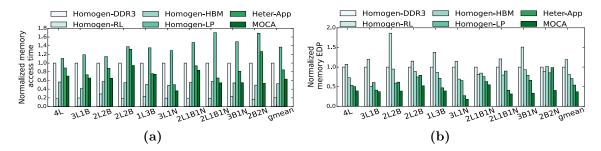

| 5.7 | (a) Memory performance in access time, and (b) memory energy effi-    |     |

|-----|-----------------------------------------------------------------------|-----|

|     | ciency in EDP of homogeneous and heterogeneous memory systems for     |     |

|     | multi-program workloads                                               | 115 |

| 5.8 | L2 MPKI of stack and code segment for all applications                | 116 |

| 6.1 | (a) Multiplication and (b) Addition operation of two values stored in |     |

|     | two OPCM cells in COSMOS.                                             | 126 |

### List of Abbreviations

| 3D    | <br>3 Dimensional                            |

|-------|----------------------------------------------|

| 2.5D  | <br>2.5 Dimensional                          |

| AI    | <br>Artificial Intelligence                  |

| ALU   | <br>Arithmetic Logic Unit                    |

| ARIMA | <br>Autoregressive Integrated Moving Average |

| BEOL  | <br>Back End of Line                         |

| DRAM  | <br>Dynamic Random Access Memory             |

| EDP   | <br>Energy-Delay Product                     |

| FWHM  | <br>Full-Width at Half Maximum               |

| HBM   | <br>High-Bandwidth Memory                    |

| HMC   | <br>Hybrid Memory Cube                       |

| HPC   | <br>High Performance Computing               |

| LLC   | <br>Last Level Cache                         |

| LUT   | <br>Lookup Table                             |

| MLP   | <br>Memory-level Parallelism                 |

| MPKI  | <br>Misses per kilo Instructions             |

| MRR   | <br>Microring Resonator                      |

| MRRG  | <br>Microring Resonator Group                |

| NLP   | <br>Natural Language Processing              |

| NVM   | <br>Non-Volatile Memory                      |

| OS    | <br>Operating System                         |

| PCM   | <br>Phase Change Memory                      |

| PTE   | <br>Page Table Entry                         |

| PV    | <br>Process Variations                       |

| RAM   | <br>Random Access Memory                     |

| ROI   | <br>Region of Interest                       |

| SCC   | <br>Single-chip Cloud Computer               |

| TIA   | <br>Transimpedance Amplifier                 |

| TLB   | <br>Translation Lookaside Buffer             |

| TSV   | <br>Through-silicon Vias                     |

| TV    | <br>Thermal Variations                       |

| - •   | <br>                                         |

#### Chapter 1

#### Introduction

We currently live in an age of unprecedented amounts of data. Data is ubiquitous. Generation over generation, human ingenuity to store data has advanced exponentially, beginning with the ancient cave paintings to the Voyager Golden Record to a flash drive that is the size of a thumb. Our ability to develop means to store and process data has been a major driving force behind societal advancement.

With the digital revolution in the 21<sup>st</sup> century, the ability to efficiently generate, process, and store this data is becoming critical across many sectors. Computational genomics is a field that is fast progressing towards extreme data-centric computing. Since the inception of the Human Genome Project in 2003 to map the entire human genomic sequence, the genomic data has been doubling every 11 months and is expected to surpass the total data requirements of Youtube and Twitter by 2025 (Cirillo and Valencia, 2019). As another example, a year of particle collisions at the Large Hadron Collider generates about one million petabytes (Hesla, 2012). Scientists now record only part of the raw data, but imagine the level of our understanding of the universe if they had the means to store the entire raw data. As a final example, to study the interaction between humans and computers, natural language processing models have seen major breakthroughs in linguistics, artificial intelligence, and cryptography techniques. In 2019, Nvidia released a model, Megatron, with 8.5 billion parameters (Nvidia, 2019), while Microsoft developed Turing-NLG with 17 billion parameters (Microsoft, 2019). The GPT-3 model developed by OpenAI in 2021 uses

174 billion parameters and requires 350GB of memory (Floridi and Chiriatti, 2020). It seems inevitable that we will reach levels of petabytes of data per day within the next decade.

Rapid proliferation in application datasets and their computational complexity has been pushing the demand for denser integration of compute cores and memory modules on a single chip. Manycore chips are already a big part of modern supercomputers and data centers. Mellanox's TILE-Gx72 is a 72-core system-on-chip that is used in intelligent networking, multimedia, and cloud applications (Mellanox, 2015). Intel's Xeon Phi series integrates up to 72 cores and multiple memory modules in a single chip (Sodani, 2015; Bradford et al., 2017), while AMD's EPYC processor family integrates 64 cores in a single chip (Lepak et al., 2017). The emergence of GPUs for machine learning and AI applications have yielded chip designs with thousands of lightweight cores. Nvidia's Turing GPUs have more than 4000 CUDA cores (Nvidia, 2018) and AMD's Navi/RDNA GPUs have more than 2500 cores (AMD, 2019).

The data-centric nature of emerging applications is pushing the design focus of manycore systems from how fast tasks can be executed to how fast data can be moved and how efficiently data can be accessed from memory systems. This has prompted the design of cost-effective and energy-efficient integration of compute cores, memory modules, and chip-scale networks in computer systems that serve supercomputers, data centers, and cloud systems. Critical design challenges in such dense manycore chips arise from 1 how fast the communication network can service requests among the different compute units and memory units, 2 how fast data can be read from and written to the memory unit, and 3 what degree of parallelism is offered by the network system and the memory unit in servicing these requests.

The prominent communication network in many core chips relies on electrical link technology, which provides a maximum bandwidth of 112Gb/s at 10-50pJ/bit (Wade et al., 2020; Pasricha and Nikdast, 2020). With roadmaps for on-chip bandwidth suggesting upwards of 1Tbps (Kim and Kim, 2014), it is impractical that electrical links can meet such demands due to their technological limitations, cost challenges, and energy constraints. On the main memory front, DRAM is the conventional technology used in most commercial servers and data centers. DDR4 DRAM provides a capacity of tens of GB with a bit density of  $0.14Gb/mm^2$  at 40pJ/bit for read/write accesses. However, power consumption in DRAM, especially the leakage power, grows substantially with technology scaling, with current DRAM consuming 40% of total system power (Mutlu, 2018; Paul et al., 2015). Moreover, DRAM internal bandwidth is not scaling at the same rate as application requirements. Thus, the challenges in data movement and data access are forcing a paradigm shift in the network and memory design to attain energy-efficient execution of data-centric applications.

This thesis explores emerging chip-scale network and memory system solutions based on silicon-photonic link and optical integration technology. Device research has demonstrated silicon-photonic links as high-bandwidth and low-latency fabrics for chip-scale communication, and phase change materials with optical control as a scalable and non-volatile memory technology. A key missing link has been adapting such devices in manycore chips and developing the necessary architecture and system-level solutions that are tailored to the optical properties of these devices. This thesis claims that designing system architectures and management policies that are aware of the application variabilities and device characteristics is essential towards achieving an energy-efficient unified "silicon-photonic link and optically-controlled memory" system. To this end, this thesis develops runtime power-management policies for silicon-photonic links, architectural designs to integrate optically-controlled phase change memory with silicon-photonic links, and memory management policies for improving the energy efficiency of heterogeneous memory systems.

#### 1.1 Designing Energy-efficient Silicon-Photonic Links

The rapid data growth and resulting compute and memory capacity in manycore systems make data movement a significant burden in chip-scale networks. Using conventional electrical links, an L1/L2 cache access on the same chip takes only about 0.1 - 0.2pJ/bit for data transfers, whereas the chip-scale data access to an L3 cache or main memory can often take up to 10 - 50pJ/bit (Pasricha and Nikdast, 2020). The latter energy numbers are  $100 \times$  higher than the energy efficiency budgets of supercomputers, cloud systems and data centers (Bergman, 2018). Enabling faster data movement at improved energy-per-bit over the chip-scale networks is, therefore, a key goal to address.

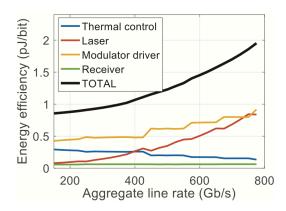

With advances in CMOS integration of silicon-photonics technology, chip-scale networks using silicon-photonic links are being developed. In 2020, Ayar Labs commercialized TeraPHY, a system that uses silicon-photonic links for chip-scale communication, providing up to 2Tbps bandwidth, and that is currently integrated into Intel's Stratix10 FPGA (Wade et al., 2020). Mellanox, now part of Nvidia, developed an optical transceiver of data rates up to 500Gps for GPU-accelerated computing (Rumley et al., 2017). Unlike electrical links, silicon-photonic links are able to deliver bandwidths on the order of > 1Tbps at reduced latency and negligible data-dependent power. Despite these promising benefits, silicon-photonic links suffer from increased power overhead at higher data rates. This overhead results from laser sources emitting optical signals and the power dissipated in electrical circuitry for serialization, modulation, and filtering of optical signals. Furthermore, optical devices such as MRRs are highly sensitive to thermal variations, requiring additional heating power for thermal tuning. This power overhead increases the network energy-per-bit for chip-scale communication. Figure 1.1 demonstrates the increasing energy-per-bit of silicon-photonic links with increasing data rates (Bahadori et al., 2017b).

Figure  $1 \cdot 1$ : Energy-per-bit consumption in silicon-photonic links with increasing data rate (Bahadori et al., 2017b).

Power management in silicon-photonic links is a challenging task due to this direct trade-off between bandwidth and energy. Using a cross-layer approach enables a deeper understanding of the device-level sensitivities of optical devices, architectural and design parameters, impact of system-level bandwidth requirements, power and thermal profile, and implementation of the software stack. We, therefore, introduce three primary techniques for energy-efficient operation of silicon-photonic links as chip-scale networks:

1. Bandwidth allocation for silicon-photonic links: We propose WAVElength Selection (WAVES) policies for power-efficient execution of silicon-photonic links. WAVES uses the bandwidth requirement of an application to activate the minimum number of optical channels for that application. Our first WAVES policy, Static Oracle-WAVES (SO-WAVES) uses the average bandwidth requirement for an application to select the number of optical channels (Narayan et al., 2019). However, SO-WAVES does not account for the runtime dynamic trends in application's bandwidth requirement. Our PROactive WAVES policy (PROWAVES) predicts the network activity for future application phases using a time-series forecasting model to select the number of optical channels (Narayan et al., 2020b). Using graph and HPC workloads from standard

benchmark suites, we demonstrate substantial power savings with SO-WAVES and PROWAVES compared to a system that uses all of its optical channels.

- 2. MRR thermal remapping during runtime application execution: Due to the high sensitivity of MRRs towards PV and TV, we develop a method that accounts for the fabrication PV and chip-scale TV at each application phase. This thesis models the low-level thermal control loop at the system-level for the first time to capture the effects of TV-induced shifts and the resultant heating power. Modeling the thermal control loop enables SO-WAVES and PROWAVES to perform MRR remapping due to TV-induced shifts at application runtime and activate the optimal set of optical channels with lowest heating power (Narayan et al., 2020b).

- 3. Application instrumentation assisted bandwidth allocation: The communication traffic in chip-scale networks highly depends on the software implementation of the application. Our proposed system-level policies, SO-WAVES and PROWAVES, do not account for this dependence. We, therefore, design a framework to perform application instrumentation at the software-level that can assist our runtime WAVES policies to further improve the energy efficiency of silicon-photonic links (Narayan et al., 2020a).

#### 1.2 Designing Scalable and High-throughput Main Memory

In addition to data movement, the key factors affecting the energy efficiency of datacentric applications are data storage and data access in the main memory. DRAM has been the prominent main memory used in the majority of computing systems. Unfortunately, DRAM technology faces critical scaling challenges at sub 20nm nodes. At lower technology nodes, leakage current in DRAM is higher, resulting in high idle power in DRAM cells (Mutlu, 2013; Kang et al., 2014; Lefurgy et al., 2003).

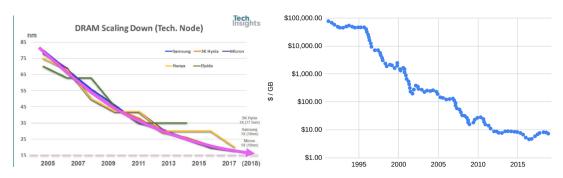

Figure 1.2: (a) DRAM technology scaling from 2005 to 2018 adapted from (Bergal, 2019). (b) Price per GB of DRAM from 1991 to 2019, according to the Objective Analysis graph (Hertz, 2021).

Moreover, DRAM cells uses capacitors to store charge, which leak charge over time and require periodic refresh to rewrite the data. These challenges put a significant burden on memory vendors working to scale down the technology nodes of memory chips. Figure 1·2 shows that DRAM scaling and the price per DRAM capacity have slowed down since 2010. To compound these issues, the limited memory bandwidth of DRAM systems fails to meet the increased bandwidth demands arising from parallel accesses of most data-centric applications.

We, therefore, need a main memory system that is amenable to technology scaling, has high bit density, meets the high capacity and bandwidth demands of data-centric applications, and uses low energy for memory accesses. NVM systems provide a scalable and non-volatile memory alternative with increased bit density and zero leakage power. A promising class of NVMs are PCMs with electrical control (EPCMs) owing to their higher reliability, increased bit density, and better write endurance (Bedeschi et al., 2008; Burr et al., 2010; Wuttig et al., 2017; Nirschl et al., 2007). Though EPCMs are highly scalable with increased bit density than DRAM, incur significant performance and energy overhead. Recent advances in device research have demonstrated phase change materials with optical control. These optically-controlled PCM cells, OPCM cells, demonstrate significantly higher bit density per cell compared

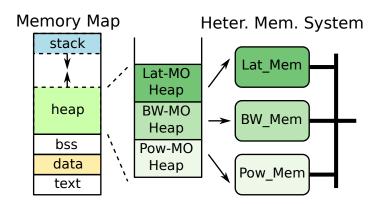

to other NVM cells, in addition to data non-volatility and high scaling. Moreover, the OPCM cells provide the opportunity for direct access with silicon-photonic links, thereby providing orders of magnitude higher memory bandwidth. Unfortunately, the current memory architectures for DRAM and EPCM systems are designed for electrical addressing and encounter major design challenges (such as increased latency, high energy, thermal issues) when adapted for OPCM cells. A main memory system using OPCM cells, therefore, requires a complete redesign of the microarchitecture, read/write access protocol, and address mapping.

In addition to the high bandwidth requirements in data-centric applications, these applications also exhibit significant diversity in their memory characteristics. For example, a highly parallel video rendering application exhibits high memory parallelism, while an iterative graph application exhibits very poor memory parallelism. Since memory modules are primarily designed to optimize either latency, bandwidth or power, a homogeneous memory system (such as DDRx, HBM, RLDRAM, LPDDRx, etc.) falls substantially short of addressing the diverse memory characteristics of applications. It is, therefore, beneficial to design a heterogeneous memory system with multiple memory modules, where different modules are optimized for different metrics. The performance of such a heterogeneous memory system is contingent on the memory management policy that can allocate pages based on the heterogeneity in memory characteristics within a given application.

The major contributions of this thesis towards designing an energy-efficient and high-throughput main memory system focus on two fronts.

1. Architecting OPCM memory system with silicon-photonic links: This thesis presents the first architectural design of a main memory system using OPCM cells that is directly accessed using silicon-photonic links. Our proposed COmbined System of Optical Phase Change Memory and Optical LinkS

(COSMOS) uses a novel read and write access protocol for accessing the memory cells in a multibanked OPCM array. COSMOS also uses an E-O-E control unit to map the standard DRAM protocol commands, data and addresses into optical signals to access the OPCM array. Owing to the increased bit density of OPCM cells and the high-bandwidth-density of silicon-photonic links, COSMOS demonstrates significant performance and energy benefits over EPCM systems. Moreover, COSMOS is the first NVM system with comparable performance and energy as DRAM systems, with increased bit density, higher scalability, non-volatility and zero leakage power.

2. Memory management for heterogeneous memory systems: We demonstrate that memory objects allocated in heap space exhibit substantial diversity in their memory characteristics. To address this diversity, this thesis presents Memory Object Classification and Allocation (MOCA) (Narayan et al., 2018). MOCA uses the memory intensity and MLP of memory objects to classify their memory characteristics, and uses this information at runtime to allocate them in the appropriate memory module in a heterogeneous memory system.

#### 1.3 Dissertation Organization

The remainder of the thesis begins with a background on silicon-photonic link technology and optically-controlled phase change memory cells, and a review of related work in Chapter 2. Chapter 3 presents our system-level power-management policies for reducing the photonic power in silicon-photonic links. Chapter 4 describes the architecture of COSMOS, a non-volatile OPCM main memory system, where the memory cells are directly interfaced using silicon-photonic links. Chapter 5 presents our memory management policy, MOCA, for heterogeneous memory systems. Chapter 6 concludes this thesis and discusses the open problems and future research directions.

#### Chapter 2

### **Background and Context**

This chapter starts with an introduction on 2.5D-integrated manycore systems as a promising alternative to 2D and 3D-stacked systems. We discuss the challenges for data-centric applications running on manycore systems arising from the limitations of chip-scale networks and main memory. The chapter then introduces silicon-photonic links as high-bandwidth-density and low-latency networks and reviews the existing works on designing energy-efficient silicon-photonic links. We then present the operation of an optically-controlled PCM cell and its promise in designing a non-volatile and high-throughput main memory that can be directly interfaced with silicon-photonic links. Later, the chapter discusses heterogeneous memory systems with different power-performance characteristics and the existing works on memory manegement in such systems. The chapter concludes with an overview of the distinguishing aspects of this thesis compared to the existing works.

#### 2.1 2.5D Manycore Computing Systems

The growing need for data-centric processing is driving the design of manycore chips with hundreds of logic cores. The design of such a densely integrated manycore chip in conventional 2D fabrication results in large die sizes and reduced manufacturing yields, contributing to high fabrication costs (Gelsinger, 2001). Since the late 2000s, 3D integration has been explored as an alternative to 2D manycore chips. 3D-integrated chips enable vertical stacking of multiples dies using dense TSVs, which

provide high-bandwidth-density between multiple dies. However, the increased transistor density with vertical stacking leads to high power density and high chip temperatures. Consequently, sophisticated cooling techniques and complex packaging solutions for 3D-integrated chips contribute to increased costs (Kandlikar, 2014).

2.5D integration has gained popularity as an alternative technology to 2D and 3D integration. In 2.5D-integrated manycore chips, multiple smaller chiplets are integrated on a large interposer. 2.5D-integrated chips are more cost-effective than 2D chips, as breaking down a large monolithic chip into multiple smaller chiplets improves the manufacturing yield (Stow et al., 2016). 2.5D-integrated chips also result in a lower power density than 3D-integrated chips, thereby resulting in lower chip temperatures (Stow et al., 2016). 2.5D integration further decouples the design of compute cores, accelerators (GPUs, APUs, etc.) and the memory systems (Kannan et al., 2015). Such an approach enables flexible integration of homogeneous or heterogeneous dies. 2.5D integration has, therefore, become prominent in commercial chips such as Xilinx Vertex 7 (Saban, 2011), Nvidia Tesla and Pascal GPUs (Hu et al., 2018), ARM CoWoS (Lin et al., 2020) and AMD Fiji GPU series (Lee et al., 2016a). Intel has also developed a 2.5D stacking technology called Embedded Multi-die Interconnect Bridge for their FPGA products (Mahajan et al., 2016) and Foveros for their LakeField CPU (Ingerly et al., 2019).

#### 2.1.1 Chip-scale Networks in 2.5D Manycore Systems

A critical performance bottleneck with integrating higher number of cores and chiplets in 2.5D manycore systems arises from the data movement in the network. Such a bottleneck could crop up due to several factors ranging from many-to-few network patterns blocking critical packets (Li and Chen, 2020), non-uniformity of the transmission data sizes (Shamim et al., 2019), redundancy of transmitted data, or local congestions in the network blocking other packets (Liu et al., 2018). Increasing the

number of cores and chiplets in 2.5D manycore systems, therefore, demands an efficient design of the chip-scale network. Vivet et al. design flexible and scalable system network topologies between the chiplets using an active interposer (Vivet et al., 2020). NoD is an independent network chiplet for 2.5D manycore chips that is responsible for routing packets from a source router to a destination router (Ebrahimi et al., 2017). Jerger et al. develop an asymmetric network-on-chip organization that accounts for the various network attributes (Jerger et al., 2014). Though these works implement efficient communication network designs, the basic fabric underneath such designs uses electrical link technology that underperforms severely due to its constrained bandwidth and long latencies.

#### 2.1.2 Main Memory in 2.5D Manycore Systems

A primary benefit with 2.5D manycore chips is the integration of memory modules on the same interposer as compute chiplets in contrast to 2D manycore chips that have processors and memory as separate dies. An interposer-based design in 2.5D chips also decouples the size of the processor chip from the memory stacks, which is an issue with 3D-integrated memory-processor chips (Loh et al., 2015). As a result, a larger size of memory chips can be integrated on the interposer. Current memory chips provide fixed bandwidth per stack. Integrating multiple such memory modules on an interposer increases the overall memory capacity as well as the peak memory bandwidth of the system. As an example, the HBM has a data transfer rate of 1024 bits operating at 1GT/s, yielding a memory bandwidth of 128GB/s (JEDEC, 2013). With 8 HBM stacks integrated on the interposer and exposed to the compute chiplets, the total available bandwidth grows to 1TB/s (Loh et al., 2015).

#### 2.2 Silicon-Photonic Link Technology

Silicon-photonic links enable data transfers at the speed of light. Compared to conventional electrical links, silicon-photonic links provide high-bandwidth-density at lower latencies and negligible data-dependent power. Silicon-photonic links are, therefore, emerging as a promising network solution in 2.5D manycore systems for data-centric applications. The feasibility of on-chip integration of optical devices such as photodiodes, low-loss waveguides, grating couplers, and MRR modulators and filters through slightly adapted or unmodified CMOS process has revolutionized the design of silicon-photonic links (Virot et al., 2014; Cardenas et al., 2009; Wade et al., 2015; Bogaerts et al., 2012).

With the maturity of silicon-photonic links for chip-scale communication, several industrial and academic efforts have focused on designing 2.5D manycore systems with such links. Oracle developed the *Macrochip* (Koka et al., 2010), which integrates multiple manycore processors in a single package with silicon-photonic links, yielding high inter-die communication bandwidth. *Galaxy* is a multi-chip architecture that integrates multiple small chiplets through optical fibers and incorporates local electrical signaling for near-communication and photonic waveguides for distant intrachiplet communication (Demir et al., 2014). Grani *et al.* implement a crossbar-based PNoC using arrayed waveguide grating router on a silicon interposer and demonstrate high bisection bandwidth at low energy-per-bit values (Grani et al., 2017).

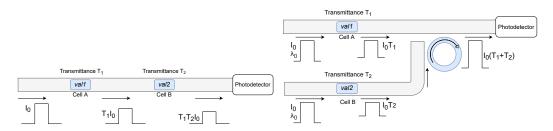

#### 2.2.1 Operation of WDM Silicon-Photonic Link

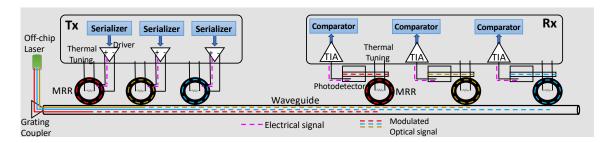

Figure 2·1 illustrates communication via a silicon-photonic link. A laser source emits multiple optical signals with n different resonant wavelengths  $\lambda_1$ ,  $\lambda_2$ , ...,  $\lambda_n$ . An optical fiber carries these n signals from the laser source to an on-chip waveguide,

<sup>&</sup>lt;sup>1</sup>The laser source can be either off-chip or integrated on-chip. In our work, we consider off-chip laser sources to simplify thermal management (Werner et al., 2017).

**Figure 2.1:** An example WDM silicon-photonic link. An off-chip laser emits 3 different optical signals. 3 MRRs at Tx modulate the data onto these 3 optical signals, and 3 MRRs at Rx filter out the data from these 3 optical signals.

where optical coupling is achieved using grating couplers. Owing to WDM, multiple optical signals, each with a distinct resonant wavelength, can coexist in the same waveguide with minimal crosstalk. Prior works have demonstrated up to 32 optical signals in a single waveguide, resulting in dense WDM and, consequently, higher bandwidth density for on-chip communication (Lee et al., 2008).

In Figure 2·1, data is sent over the silicon-photonic link from Tx to Rx. MRRs are used for data modulation at Tx and data filtering at Rx. An MRR utilizes a coupling mechanism to access the optical signal in a waveguide. When the coupled optical wave in an MRR builds up a round trip phase that is an integral multiple of  $2\pi$ , the MRR is in resonance with it and most of the optical power is diverted from the waveguide to the MRR. A cascade of n MRRs are placed at Tx, each with a resonant wavelength matching one of the n optical signals from the laser. A data packet is first serialized and modulated by an MRR on to one of the optical signals. Similarly, another data packet is serialized and modulated by another MRR on to a second optical signal. The modulated optical signals traverse the silicon-photonic link to Rx. At Rx, another set of n MRRs are placed, each of which resonates as the n optical signals. Each MRR can filter out a modulated optical signal with matching resonant wavelength from the waveguide. The filtered optical signal is then captured by a

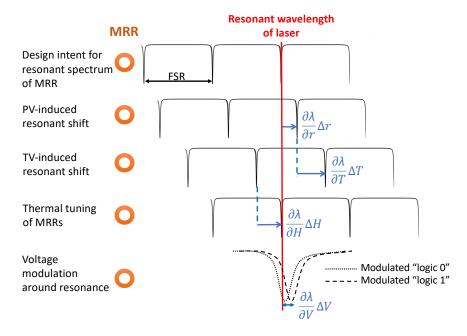

Figure 2.2: MRR sensitivity to TV and PV. MRRs are designed to resonate at peak resonant wavelength of an optical signal. TV and PV induces shifts in the MRR resonant wavelength. The MRRs are supplied with heating power to tune back to laser wavelength.

photodetector (Lischke et al., 2015) that converts the optical signal into an electrical signal. This electrical signal is amplified by a TIA, and read by a set of comparators as either logic 0 or logic 1.

### 2.2.2 Device-level Characteristics

MRRs are typically fabricated using silicon, which has a high thermo-optic coefficient  $(1.86 \times 10^{-4} K^{-1})$  (Densmore et al., 2009). With changes in temperature, the high thermo-optic coefficient induces variations in the refractive index of the MRR, which in turn shifts the MRR resonant wavelength to a higher value, as shown in Figure 2·2. As a result, the MRR moves out of resonance with its coupled optical signal's wavelength. Silicon MRRs have been demonstrated to have a high sensitivity to TV, about 70 - 100 pm/K (Padmaraju and Bergman, 2014). With chip temperature gradients rising as high as 20 - 25K, the MRR resonant wavelength shift due to

TV becomes critically high. Moreover, the MRRs at Tx and Rx experience different resonant wavelength shifts due to the on-chip thermal gradients. The resulting mismatches in the MRR resonant wavelengths at Tx and Rx, therefore, impact the link integrity during data transmission in the silicon-photonic link.

Furthermore, the non-idealities associated with CMOS fabrication process introduce variations in the thickness, width and roughness of the MRRs (Chen et al., 2013). Krishnamoorthy et al. quantify the intrawafer and interwafer variations on the resonant wavelengths of MRRs (Krishnamoorthy et al., 2011). Their study shows that absolute resonances of MRRs cannot be controlled across the wafers or even across reticles within a wafer. Due to variations in waveguide width, silicon thickness and etch-depth non-uniformities, the effective refractive index of silicon changes. As a result, the resonant wavelengths of MRRs shift significantly from the design intent, as shown in Figure 2·2. Therefore, during the fabrication process of a die reticle, two distant MRRs in the same die experience completely different shifts in their resonant wavelengths. These PV-induced shifts further add to the TV-induced mismatches in Tx and Rx MRR resonant wavelengths.

It is, therefore, critical to mitigate the effect of TV- and PV-induced resonant wavelength shifts to ensure reliable communication using silicon-photonic links.

### 2.2.3 Thermal Management in Silicon-Photonic Links

Active control of MRR resonant wavelengths is carried out by thermally tuning an MRR to the higher order resonant wavelength of an optical signal. Figure 2·2 shows the thermal tuning of an MRR, which is achieved by controlled local heat injection using resistive heaters inside the MRRs. These heaters supply energy to the MRRs using Joule effect, thereby increasing the MRR temperature and right-shifting the MRR resonant wavelength (Bahadori et al., 2017a). The MRR, thus, locks on to the higher order wavelength of the optical signal in the wavelength spectrum.

Figure 2·3: An analog thermal control loop compares the photocurrent with a reference current and drives a heater current to thermally tune an MRR.

### Thermal Control Loop

Thermal tuning with controlled local heat injection requires a closed-loop feedback system that monitors the MRR resonance shift and the tuning required for an MRR to lock on to an optical signal. As shown in Figure 2·3, this is done by measuring the optical power on the drop port of the MRR with a photodetector. An analog control compares the photocurrent to a reference current that is set based on the MRR resonance. The error signal drives a heater current to thermally tune the MRR using Joule heating. The heater maintains a fixed temperature within the MRR, so that the MRR resonance remains fixed to the resonant wavelength of the optical signal. Several design techniques exist for analog thermal control to close the feedback loop and derive a heating level from the optical monitoring of the drop port (Rakowski et al., 2015; Yu et al., 2015; Sun et al., 2016; Thonnart et al., 2018; Li et al., 2015).

Additionally, a second level of control is required to handle the large temporal TV occurring at runtime. When the large TV introduces an increased shift in the MRR resonant wavelength, thermally tuning the MRR to its original optical channel requires a high heater power. Fortunately, with WDM, the resonant wavelengths of optical channels are evenly spaced in the FSR as shown in Figure 2.4. It is, therefore, possible to thermally tune  $MRR_0$  and lock it to  $\lambda_1$  instead of  $\lambda_0$ . This

**Figure 2.4:** (a) The thermal control loop maintains the 4 MRRs at the resonant wavelength of 4 optical signals. (b) A large TV induces a high MRR resonance shift, and the thermal control loop performs thermal remapping to a new set of optical signals.

additional level of control enables the wavelength remapping of MRRs to a different set of optical channels. During an application execution, when the chip temperature increases close to the target MRR temperature, the analog thermal control forces a remapping of MRRs to a different set of optical channels. These remappings between n wavelengths are only possible if the heater efficiency is high enough that it can shift by more than FSR/n with some margin. As remapping requires larger amounts of thermally-controlled shifts, it is a relatively slow process of about  $100\mu s$ , but occurs less than once per second due to the thermal inertia of chips (Thonnart et al., 2018).

### System-level Management

The analog thermal control to thermally tune the MRRs is an effective thermal management technique in silicon-photonic links. However, such device-level techniques do not account for the runtime characteristics of workloads. There is a strong diversity in workloads' runtime bandwidth and resource utilization that result in highly workload-specific power and thermal profiles. The heating power for MRR thermal tuning is, therefore, a strong function of the system architecture and runtime application behavior. Prior work on system-level management focuses on cross-layer optimization methodologies that model device and design-level thermal management strategies under different system-level constraints.

RingAware (Zhang et al., 2014), Therma (Beigi and Memik, 2016) and FreqAlign (Abellán et al., 2017) employ thread allocation and migration to reduce the thermal variations around communicating MRRs. Aurora (Li et al., 2015) encompasses a cross-layer approach at the device, system and OS-level to control the thermal tuning power. LIBRA (Thakkar and Pasricha, 2018) uses a reactive technique at device-level and a proactive thread migration policy at system-level to reduce the impact of TV- and PV-induced MRR resonant shifts.

### 2.2.4 Bandwidth Allocation in Silicon-Photonic Links

In addition to the heating power for MRR thermal tuning, the power consumed in the laser sources and the circuitry for E-O and O-E conversion form a major portion of the overall photonic power. A high density of multiplexed optical signals is used in WDM silicon-photonic link to deliver increased bandwidth for data-centric applications. Consequently, the photonic power increases linearly with the number of optical signals in the silicon-photonic link (Bahadori et al., 2016). It is, therefore, critical to address the trade-off between achieving high bandwidth and reducing photonic power consumption and ensure sub-pJ operation at > 1Tbps on-chip bandwidths.

System-level bandwidth allocation techniques are implemented by assigning optical channels depending on the bandwidth requirements of applications. Several studies perform bandwidth allocation in different contexts by enabling a higher number of channels for maximum aggregated bandwidth (Bahadori et al., 2016), or via

optimized wavelength allocation in silicon-photonic links based on application task graph (Luo et al., 2018), or using an arbitration-free shared-channel silicon-photonic link (Zulfiqar et al., 2013), among others. Winkle et al. design a learning-based technique using silicon-photonic link utilization to determine the optimal number of channels (Van Winkle et al., 2018). Chen et al. perform runtime bandwidth allocation on clos and butterfly network topologies based on latency at each application phase (Chen and Joshi, 2013). R-3PO is a reconfigurable 3D-integrated silicon-photonic network that monitors the bandwidth availability and performs runtime reconfiguration of network bandwidth (Morris et al., 2012).

A key missing aspect in these bandwidth allocation policies arises from a lack of characterization models of MRR device-level sensitivities. The thermal control loop uses a continuous mechanism to monitor the TV and PV sensitivities of on-chip MRRs. A large temperature drift during an application execution results in a major shift in MRR resonant wavelength and, therefore, requires MRR remapping to a new set of optical channels. This remapping provides the opportunity to remap to a new set of optical channels that result in minimal thermal tuning power. The prior works for bandwidth allocation do not model the thermal control loop, leaving an open opportunity to incorporate MRR remapping to reduce the thermal tuning power.

# 2.3 Optically-controlled Phase Change Memory

Though silicon-photonic links enable high-bandwidth and low-latency chip-scale network designs, the system performance is still hampered by internal bandwidth and latency of main memory systems. With DRAM technology facing critical scaling challenges at lower technology nodes (Kim et al., 2010; Kim and Popovici, 2018), memory vendors and academic researchers are focusing their efforts towards developing non-volatile and scalable memory systems. Non-volatile memories such as memresistor

**Figure 2.5:** Operating principle of a GST element. **RESET:** The GST element is heated to its melting temperature and rapidly cooled to change to a-GST. **SET:** The GST element is heated to its crystalline temperature and gradually cooled to change to c-GST.

arrays, spin-transfer torque magnetic RAM, NAND Flash memory, and PCM have emerged as promising non-volatile alternatives to DRAM (Rho et al., 2017; Kwon et al., 2015; Lee et al., 2009; Kim et al., 2019; Zhang et al., 2019; Bhattacharjee et al., 2017). PCMs outperform many other NVM candidates owing to their higher reliability, increased bit density, and better write endurance (Bedeschi et al., 2008; Burr et al., 2010; Wuttig et al., 2017; Nirschl et al., 2007). In this section, we first study the properties of phase change materials. We then look at the operation and challenges of conventional electrically-controlled PCM cells. We contrast OPCM cells to EPCM cells and present promising opportunities to design high-throughput and scalable main memory systems using OPCM technology.

### 2.3.1 Properties of Phase Change Materials