## BOSTON UNIVERSITY COLLEGE OF ENGINEERING

Dissertation

## ENERGY-EFFICIENT ELECTRICAL AND SILICON-PHOTONIC NETWORKS IN MANYCORE SYSTEMS

by

### CHAO CHEN

B.E., Shanghai Jiao Tong University, 2005 M.S., Pohang University of Science and Technology, 2007

Submitted in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

2014

UMI Number: 3581011

All rights reserved

### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

UMI 3581011 Published by ProQuest LLC 2014. Copyright in the Dissertation held by the Author. Microform Edition © ProQuest LLC. All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346 Approved by

First Reader

Ajay Joshi, PhD Assistant Professor of Electrical and Computer Engineering

Second Reader

Ayse K. Coskun, PhD Assistant Professor of Electrical and Computer Engineering

Third Reader

Martin Herbordt, PhD Associate Professor of Electrical and Computer Engineering

Fourth Reader

Jonathan Klamkin, PhD Assistant Professor of Electrical and Computer Engineering

The interconnection network is the heart of parallel architecture Chuan-Lin and Tse-Yun Feng Interconnection Networks for Parallel and Distributed Processing (1984)

### Acknowledgments

I would like to express my deepest appreciation to the committee members for reviewing this dissertation and providing me precious feedback. Then I want to thank my adviser, Prof. Ajay Joshi, who led my research and worked with me for many interesting research topics. Also it is my pleasure to work with Dr. Abellan Jose, the post-doctoral fellow in our group, who provided many experimental results and valuable suggestions. I want to thank members in our group, Zafar takhirov, Mahmoud Zangeneh, and Schuyler Eldridge for making our research in the lab enjoyable.

Also I wish to thank Prof. Ayse Coskun and Prof. Jonathan Klamkin for their suggestions in my research. They helped me overcome many technical obstacles when we were writing papers together. I also want to thank several members in their groups, including Tiansheng Zhang, Dr. Jie Meng, and Dr. Pietro Contu, for all their contributions when we were working on research projects together.

In addition, a thank you to thank Prof. Martin Herbordt and Prof. Roscoe Giles. I worked as a teaching fellow for their classes in the first year at Boston University. I enjoyed when helping undergraduate students with their homework and lab projects, and I also obtained a lot of useful knowledge for my later research.

Finally, I want to thank my father, Shunjin Chen, my mother, Wenin Liu, and my wife, Xiaodan Zhang for their continuous support and encouragement. They helped me focus on the research and work hard for achieving my education and career goals. Especially, my wife gave up a very good job opportunity in China and chose to stay with me in the United States. I hope to provide my parents and wife better lives after graduation and spend more time with them.

#### I dedicate this dissertation to my parents and my beloved wife.

## ENERGY-EFFICIENT ELECTRICAL AND SILICON-PHOTONIC NETWORKS IN MANYCORE SYSTEMS

### CHAO CHEN

Boston University, College of Engineering, 2014

Major Professor: Ajay Joshi, PhD, Professor of Electrical and Computer Engineering

### ABSTRACT

During the past decade, the very large scale integration (VLSI) community has migrated towards incorporating multiple cores on a single chip to sustain the historic performance improvement in computing systems. As the core count continuously increases, the performance of network-on-chip (NoC), which is responsible for the communication between cores, caches and memory controllers, is increasingly becoming critical for sustaining the performance improvement. In this dissertation, we propose several methods to improve the energy efficiency of both electrical and silicon-photonic NoCs. Firstly, for electrical NoC, we propose a flow control technique, Express Virtual Channel with Taps (EVC-T), to transmit both broadcast and data packets efficiently in a mesh network. A low-latency notification tree network is included to maintain the order of broadcast packets. The EVC-T technique improves the NoC latency by 24% and the system energy efficiency in terms of energy-delay product (EDP) by 13%. In the near future, the silicon-photonic links are projected to replace the electrical links for global on-chip communication due to their lower datadependent power and higher bandwidth density, but the high laser power can more than offset these advantages. Therefore, we propose a silicon-photonic multi-bus NoC architecture and a methodology that can reduce the laser power by 49% on average through bandwidth reconfiguration at runtime based on the variations in bandwidth requirements of applications. We also propose a technique to reduce the laser power by dynamically activating/deactivating the L2 cache banks and switching ON/OFF the corresponding silicon-photonic links in a crossbar NoC. This cache-reconfiguration based technique can save laser power by 23.8% and improves system EDP by 5.52% on average. In addition, we propose a methodology for placing and sharing on-chip laser sources by jointly considering the bandwidth requirements, thermal constraints and physical layout constraints. Our proposed methodology for placing and sharing of on-chip laser sources reduces laser power. In addition to reducing the laser power to improve the energy efficiency of silicon-photonic NoCs, we propose to leverage the large bandwidth provided by silicon-photonic NoC to share computing resources. The global sharing of floating-point units can save system area by 13.75% and system power by 10%.

## Contents

| 1        | Bac | kgrou                                     | nd and Introduction                                                                               | 1  |  |  |

|----------|-----|-------------------------------------------|---------------------------------------------------------------------------------------------------|----|--|--|

|          | 1.1 | Trend                                     | s in VLSI Computing System                                                                        | 1  |  |  |

|          | 1.2 | Electr                                    | ical NoC                                                                                          | 2  |  |  |

|          | 1.3 | Silicor                                   | n-photonic NoC                                                                                    | 4  |  |  |

|          |     | 1.3.1                                     | Laser Power Management                                                                            | 4  |  |  |

|          |     | 1.3.2                                     | On-chip Laser Source                                                                              | 8  |  |  |

|          |     | 1.3.3                                     | The Use of Large Bandwidth                                                                        | 9  |  |  |

|          | 1.4 | Contr                                     | ibution and Organization                                                                          | 10 |  |  |

| <b>2</b> | Bro | adcast                                    | through Express Virtual Channel with Taps in Electrical                                           | L  |  |  |

|          | No  | C                                         |                                                                                                   | 14 |  |  |

|          | 2.1 | Introd                                    | luction $\ldots$ | 14 |  |  |

|          | 2.2 | Target                                    | t System                                                                                          | 16 |  |  |

|          | 2.3 | Notification Trees for Broadcasting Order |                                                                                                   |    |  |  |

|          | 2.4 | EVC-'                                     | T Flow Control Mechanism                                                                          | 22 |  |  |

|          |     | 2.4.1                                     | Express Virtual Channels (EVC)                                                                    | 22 |  |  |

|          |     | 2.4.2                                     | Express Virtual Channels with Taps (EVC-T) $\ldots$                                               | 24 |  |  |

|          |     | 2.4.3                                     | Flit Organization for EVC-T                                                                       | 28 |  |  |

|          |     | 2.4.4                                     | Credit Channels for EVC-T                                                                         | 29 |  |  |

|          | 2.5 | Evalua                                    | ation                                                                                             | 29 |  |  |

|          |     | 2.5.1                                     | Simulation Methodology                                                                            | 31 |  |  |

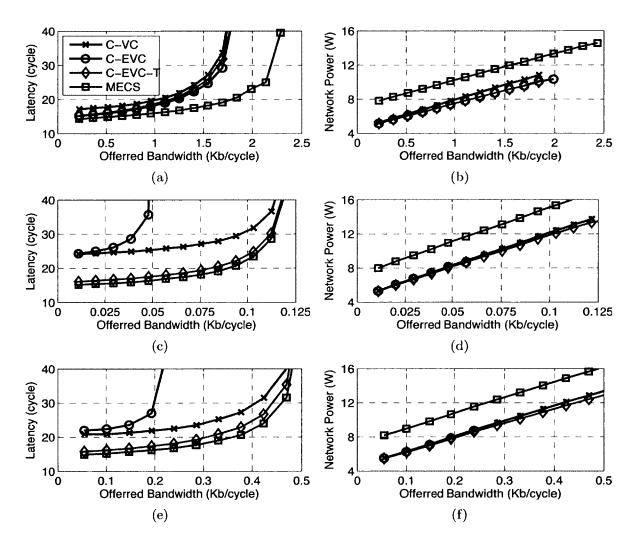

|          |     | 2.5.2                                     | Evaluation Results with Synthetic Benchmarks                                                      | 33 |  |  |

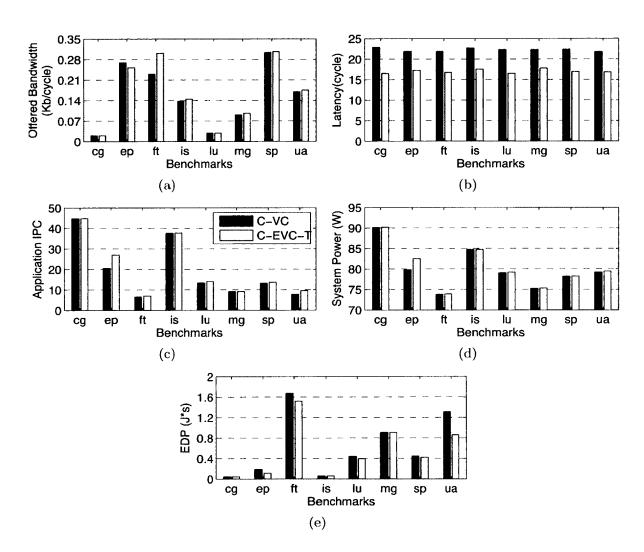

|   |     | 2.5.3 Evaluation Results with NAS Benchmarks                            | . 36       |

|---|-----|-------------------------------------------------------------------------|------------|

|   | 2.6 | Summary                                                                 | . 38       |

| 3 | Bar | dwidth Reconfiguration for Managing Laser Power in Silic                | on-        |

|   |     | onic NoC                                                                | 40         |

|   | 3.1 | Introduction                                                            | . 40       |

|   | 3.2 | Target System                                                           | . 43       |

|   | 3.3 | Photonic Technology                                                     | . 44       |

|   | 3.4 | Multi-bus NoC Architecture                                              | . 47       |

|   | 3.5 | Laser Power Management                                                  | . 52       |

|   |     | 3.5.1 Runtime Network Reconfiguration                                   | . 53       |

|   |     | 3.5.2 Bandwidth Weight Calculation                                      | . 55       |

|   | 3.6 | Evaluation                                                              | . 58       |

|   |     | 3.6.1 Simulation Methodology                                            | . 58       |

|   |     | 3.6.2 Evaluation Results with NAS Benchmarks                            | . 59       |

|   | 3.7 | Discussion                                                              | . 66       |

|   |     | 3.7.1 Large Core Counts                                                 | . 66       |

|   |     | 3.7.2 Simultaneously Executing Applications                             | . 67       |

|   |     | 3.7.3 Distributed L2 Cache vs. Private L2 Cache                         | . 67       |

|   |     | 3.7.4 Alternate NoC Architectures                                       | . 68       |

|   | 3.8 | Summary                                                                 | . 69       |

| 4 |     | time Cache Reconfiguration for Managing Laser Power in Sili<br>onic NoC | con-<br>70 |

|   | 4.1 | Introduction                                                            | . 70       |

|   | 4.2 | Target System, Simulation tools                                         | . 72       |

|   | 4.3 | Runtime Reconfiguration                                                 |            |

|   |     | 4.3.1 Reconfiguration Controller                                        |            |

|   |          | 4.3.2    | Reconfiguration Decision Process                                          | 76        |

|---|----------|----------|---------------------------------------------------------------------------|-----------|

|   |          | 4.3.3    | L2 Bank Activation/Deactivation Process                                   | 79        |

|   | 4.4      | Evalua   | ation                                                                     | 81        |

|   |          | 4.4.1    | Simulation Methodology                                                    | 81        |

|   |          | 4.4.2    | Reconfiguration Opportunities                                             | 82        |

|   |          | 4.4.3    | Reconfiguration Benefits                                                  | 84        |

|   | 4.5      | Summ     | nary                                                                      | 88        |

| 5 |          | 0        | nd Placement of On-chip Laser Sources for Managing Lase                   | er        |

|   | Pov      | ver in S | Silicon-photonic NoC                                                      | 89        |

|   | 5.1      | Introd   | luction                                                                   | 89        |

|   | 5.2      | Target   | t System                                                                  | 91        |

|   | 5.3      | Laser    | Sources                                                                   | 93        |

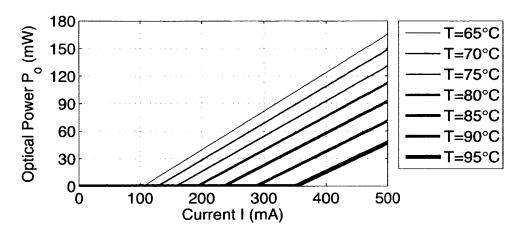

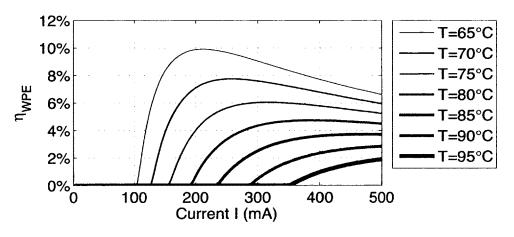

|   |          | 5.3.1    | Modeling                                                                  | 94        |

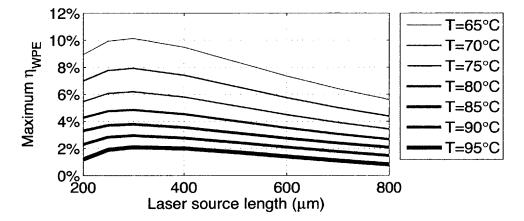

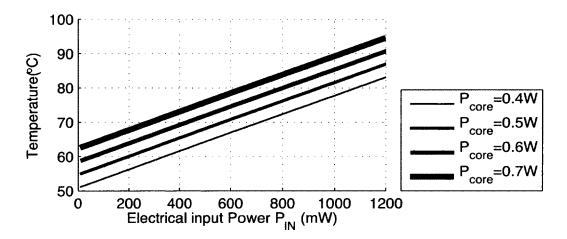

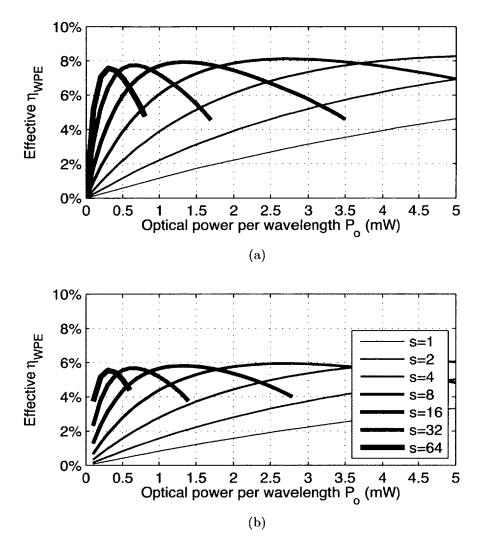

|   |          | 5.3.2    | Optical Power, WPE and Temperature Tradeoffs                              | 96        |

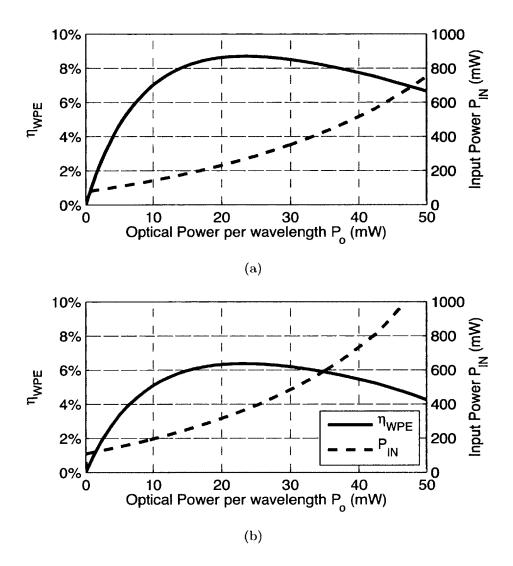

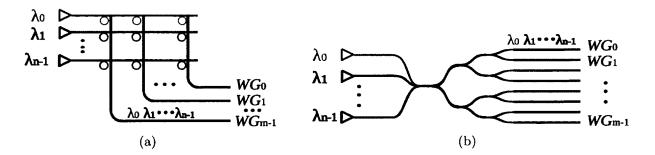

|   |          | 5.3.3    | Broadband vs Single-band Laser Sources                                    | 101       |

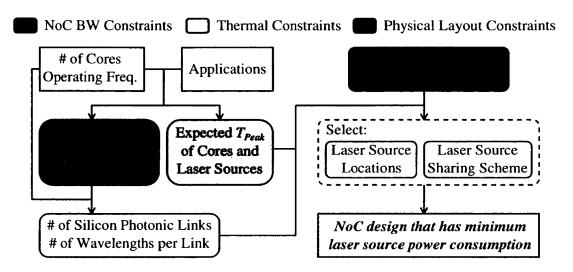

|   |          | 5.3.4    | Methodology to Determine Optimal Sharing and Placement .                  | 102       |

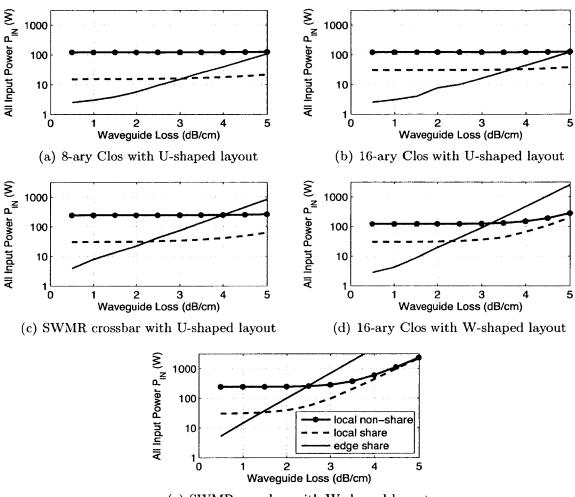

|   | 5.4      | Case S   | Studies                                                                   | 104       |

|   | 5.5      | Summ     | ary                                                                       | 109       |

| 6 |          | •        | f Computing Resources through Large Bandwidth Pro<br>Silicon-photonic NoC | )-<br>111 |

|   | 6.1      | •        | luction                                                                   | 111       |

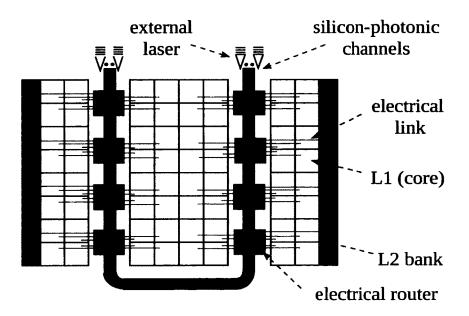

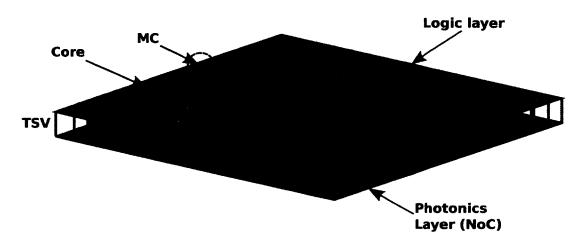

|   | 6.2      |          | t System                                                                  | 115       |

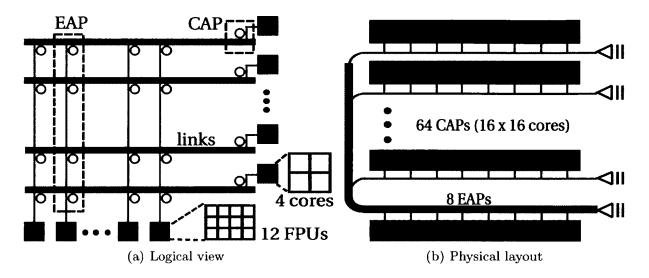

|   | 0.2      | 6.2.1    | Logic Layer                                                               | 115       |

|   |          |          |                                                                           |           |

|   | <u> </u> | 6.2.2    | Photonic Layer                                                            | 118       |

|   | 6.3      |          | UCloud-based Manycore System                                              | 119       |

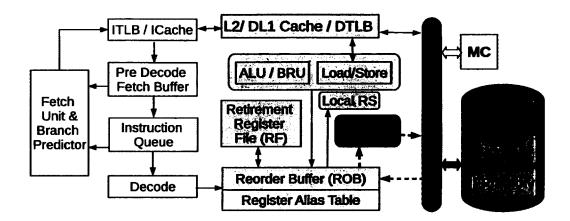

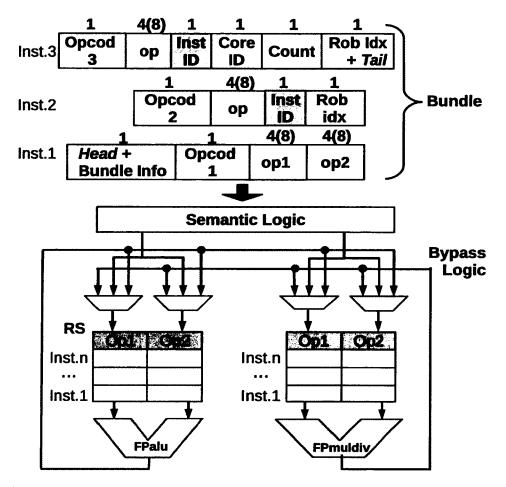

|   |          | 6.3.1    | Processor Core Design                                                     | 119       |

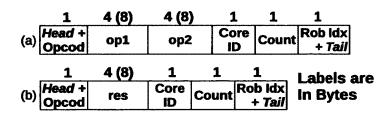

|                |               | 6.3.2   | Core-to-EUCloud NoC Architecture                                                               | 122 |

|----------------|---------------|---------|------------------------------------------------------------------------------------------------|-----|

|                |               | 6.3.3   | Execution in EUCloud                                                                           | 126 |

|                |               | 6.3.4   | Execution in EUCloud using Instruction Bundling                                                | 128 |

|                |               | 6.3.5   | Workload Allocation                                                                            | 132 |

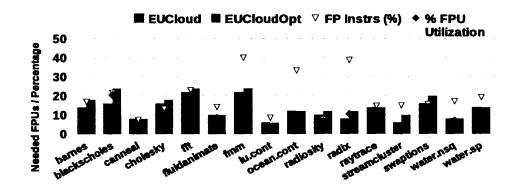

|                | 6.4           | Evalua  | tion $\ldots$ | 133 |

|                |               | 6.4.1   | Simulation Methodology                                                                         | 133 |

|                |               | 6.4.2   | EUCloud and NoC Design                                                                         | 134 |

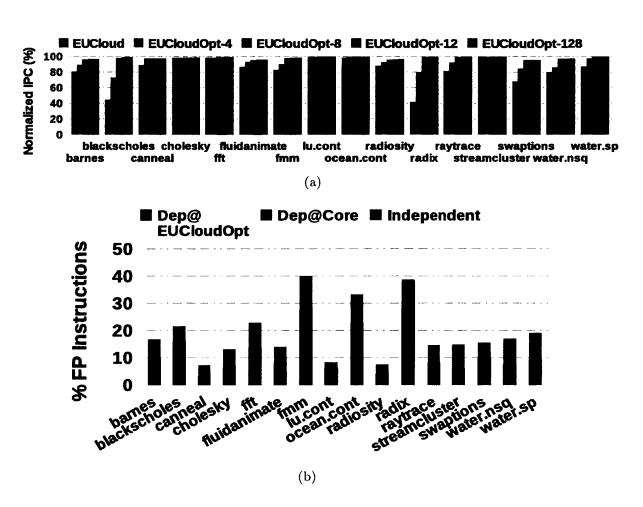

|                |               | 6.4.3   | Single-Application Performance                                                                 | 137 |

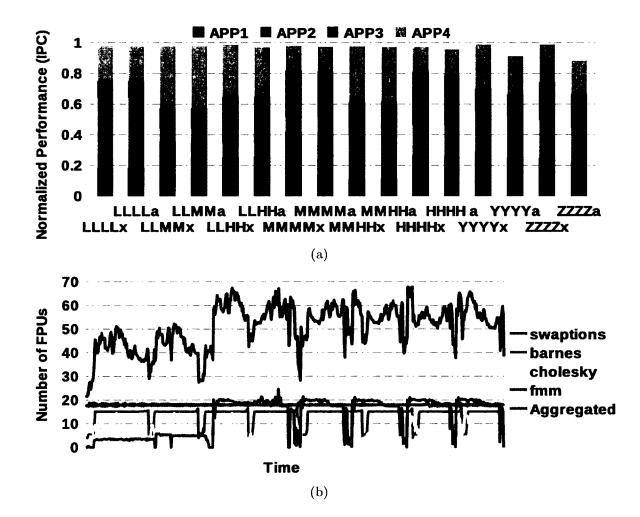

|                |               | 6.4.4   | Multi-programmed Workload Performance                                                          | 139 |

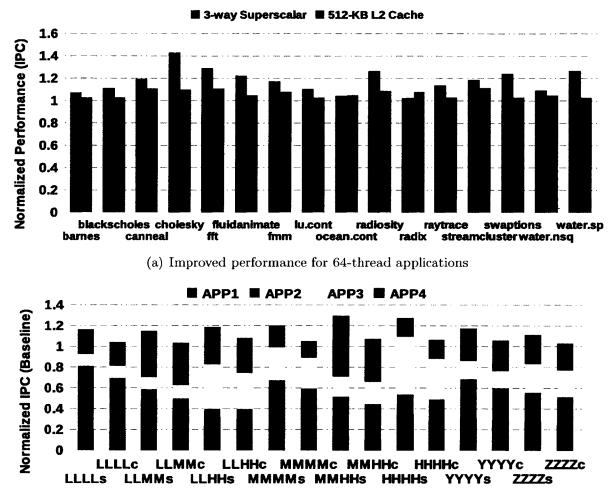

|                |               | 6.4.5   | EUCloud-based Manycore Benefits                                                                | 141 |

|                |               | 6.4.6   | Clustered vs. Global EUCloud                                                                   | 143 |

|                | 6.5           | Summ    | ary                                                                                            | 144 |

| 7              | Cor           | clusior | n and Future Work                                                                              | 146 |

|                | 7.1           | Conclu  | usion                                                                                          | 146 |

|                | 7.2           | Future  | Work                                                                                           | 149 |

|                |               | 7.2.1   | Laser Power Management through Core Reconfigurations                                           | 149 |

|                |               | 7.2.2   | Runtime Selection and Sharing of On-chip Laser Sources                                         | 149 |

|                |               | 7.2.3   | Performance Improvement through Silicon-photonic NoCs                                          | 150 |

| R              | e <b>fere</b> | nces    |                                                                                                | 151 |

| $\mathbf{C}_1$ | urric         | ulum V  | Vitae                                                                                          | 161 |

## List of Tables

| 2.1 | Micro-architectural parameters of the 64-core system                        | 17  |

|-----|-----------------------------------------------------------------------------|-----|

| 2.2 | Timing analysis of the notification tree architecture                       | 20  |

| 2.3 | Network architecture details                                                | 30  |

| 3.1 | Micro-architectural parameters of the 64-core system $\ldots \ldots \ldots$ | 43  |

| 3.2 | Energy and Power Projections for Photonic Devices                           | 46  |

| 3.3 | Optical Loss per Component                                                  | 46  |

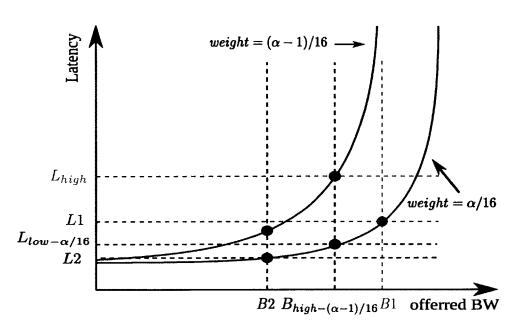

| 3.4 | $L_{low}$ for all bandwidth weight at various $L_{high}$                    | 56  |

| 4.1 | Micro-architectural parameters of the 64-core system                        | 72  |

| 5.1 | Architectural-level parameters for 5 NoCs under consideration $\ldots$ .    | 105 |

| 6.1 | Architectural parameters of the 256-core system                             | 117 |

| 6.2 | Multi-programmed workloads composed of four 64-thread applications          |     |

|     | that are classified depending on demand of FPUs                             | 139 |

## List of Figures

| $1 \cdot 1$ | Trends in transistor count, performance, core count and power over        |    |

|-------------|---------------------------------------------------------------------------|----|

|             | the past decades                                                          | 2  |

| $1 \cdot 2$ | Power breakdown of manycore network                                       | 6  |

| $2 \cdot 1$ | Physical layout of our 64-core system with electrical NoC                 | 18 |

| $2 \cdot 2$ | Example of Notification trees                                             | 19 |

| $2 \cdot 3$ | Example of broadcast packets                                              | 20 |

| $2 \cdot 4$ | The router architecture for EVC                                           | 23 |

| $2 \cdot 5$ | The C-EVC network: physical cmesh layout with EVC                         | 24 |

| $2 \cdot 6$ | The router architecture supporting EVC-T                                  | 25 |

| $2 \cdot 7$ | The C-EVC-T network: the physical cmesh layout with EVC-T $\ .$           | 26 |

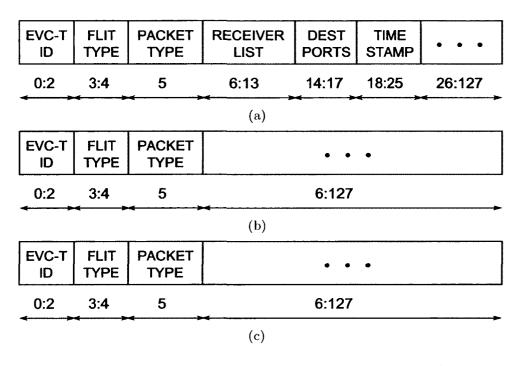

| $2 \cdot 8$ | Flit organization of an EVC-T packet                                      | 27 |

| $2 \cdot 9$ | Network latency and power vs. offered bandwidth                           | 34 |

| 2.10        | Comparison of C-VC and C-EVC-T networks                                   | 37 |

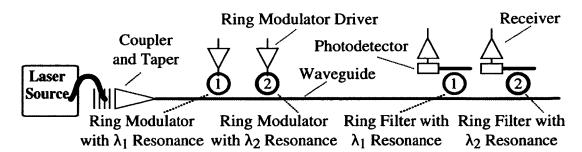

| $3 \cdot 1$ | Photonic Link Components                                                  | 45 |

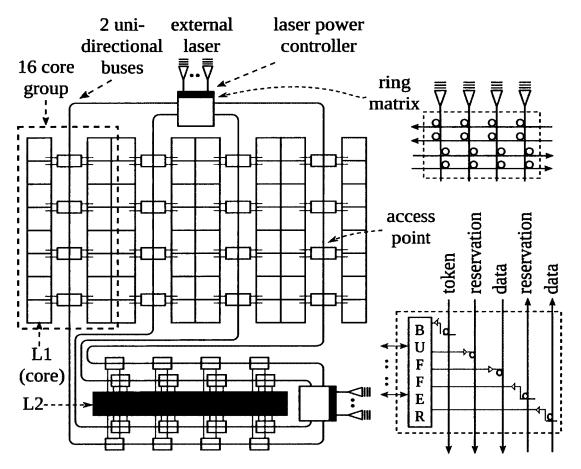

| $3 \cdot 2$ | Physical layout of the silicon-photonic multi-bus NoC architecture        | 48 |

| 3.3         | Timing diagram for token stream arbitration                               | 50 |

| $3 \cdot 4$ | Physical layout of the silicon-photonic Clos and butterfly NoC archi-     |    |

|             | tecture                                                                   | 51 |

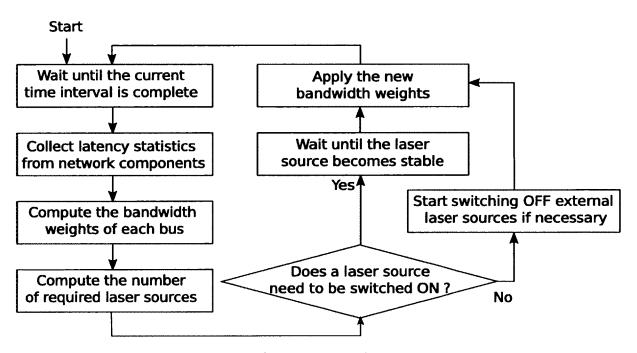

| 3.5         | Flow chart for runtime laser power management using weighted TDM          | 55 |

| 3.6         | Methodology to determine threshold $L_{low}$ for a bandwidth weight $\ .$ | 56 |

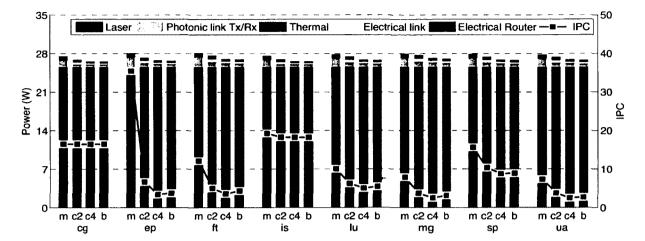

| 3.7         | Power and IPC for various NoCs with the same laser power budget .         | 60 |

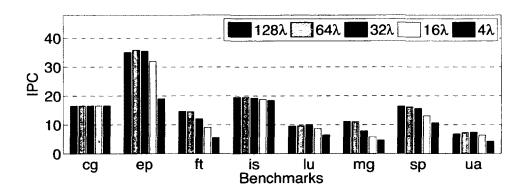

| $3 \cdot 8$  | IPC for various baseline bandwidth                                                                    | 61  |

|--------------|-------------------------------------------------------------------------------------------------------|-----|

| 3.9          | IPC and bandwidth weight for various reconfiguration threshold $L_{high}$                             | 62  |

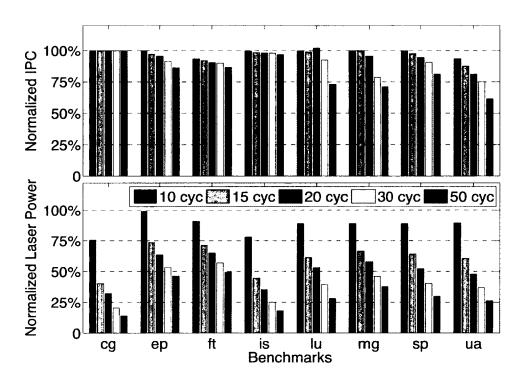

| $3 \cdot 10$ | $\operatorname{IPC}$ and bandwidth weight for various reconfiguration time interval $% \mathcal{A}$ . | 63  |

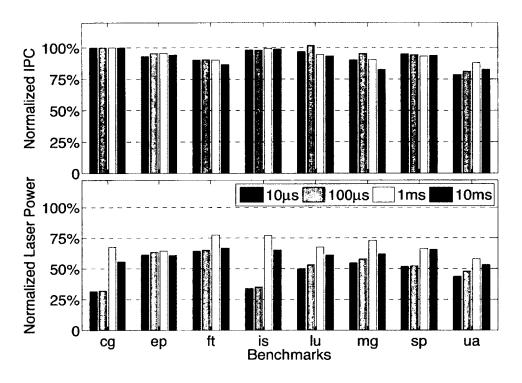

| 3.11         | IPC, network traffic and bandwidth weight tracing for selected bench-                                 |     |

|              | marks                                                                                                 | 65  |

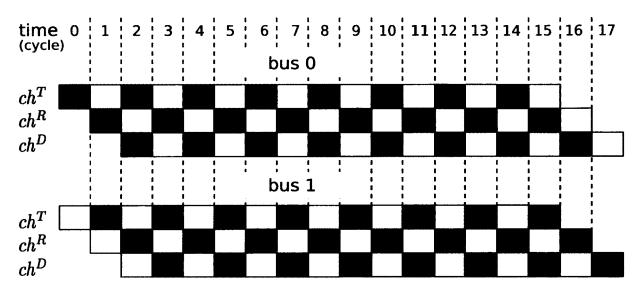

| $4 \cdot 1$  | Logical topology of a silicon-photonic crossbar NoC $\ldots$                                          | 73  |

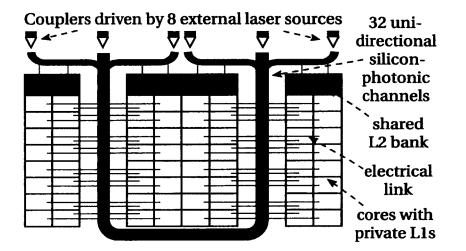

| $4 \cdot 2$  | Physical layout of the silicon-photonic crossbar NoC                                                  | 74  |

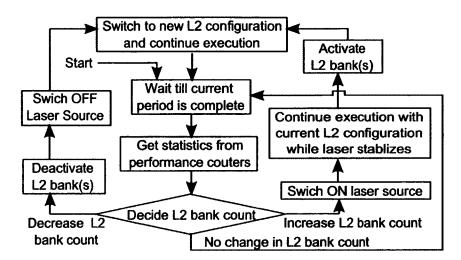

| $4 \cdot 3$  | Flowchart for runtime reconfiguration                                                                 | 76  |

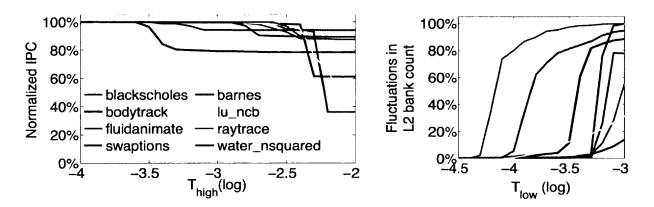

| $4 \cdot 4$  | The choice of thresholds $T_{high}$ and $T_{low}$                                                     | 78  |

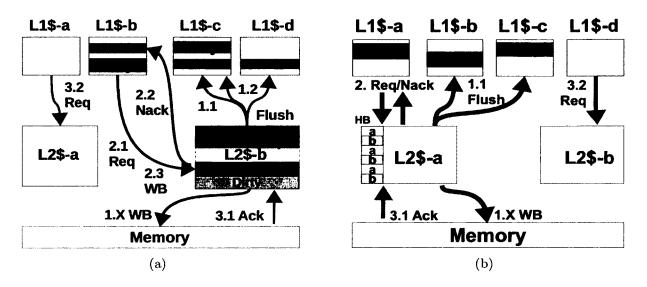

| 4.5          | L2 cache bank reconfiguration process                                                                 | 80  |

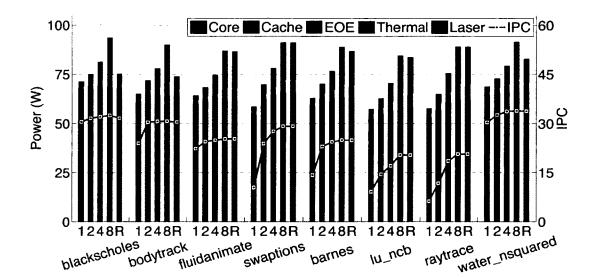

| $4 \cdot 6$  | IPC, replacement rate and 12 bank count tracing for selected benchmarks                               | 83  |

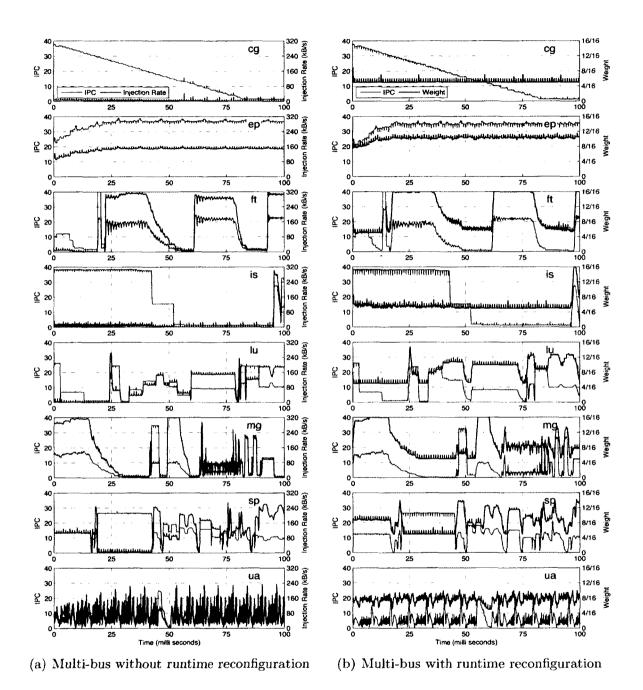

| 4.7          | Impact of runtime reconfiguration on system performance and power                                     | 84  |

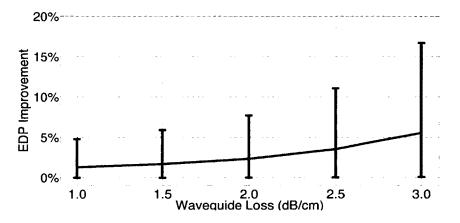

| $4 \cdot 8$  | EDP improvement across vs. waveguide loss                                                             | 85  |

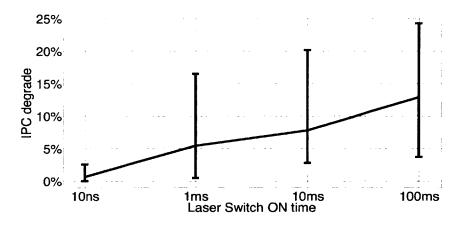

| $4 \cdot 9$  | IPC degradation vs. laser switch ON time                                                              | 86  |

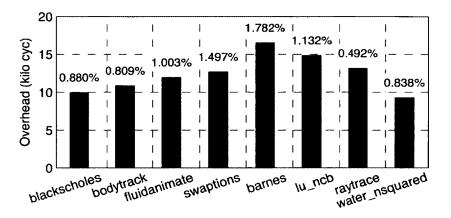

| 4.10         | Reconfiguration overhead for various benchmarks                                                       | 87  |

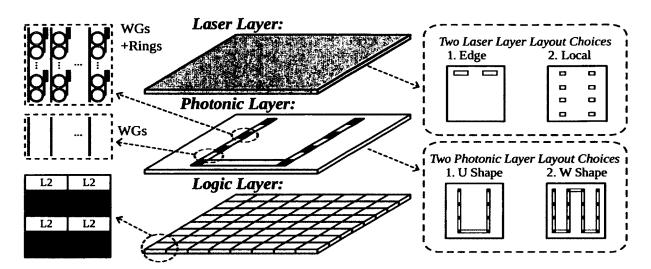

| $5 \cdot 1$  | Overview of the 3D flip-chip many<br>core system and layouts for each layer $% \mathcal{A}$           | 91  |

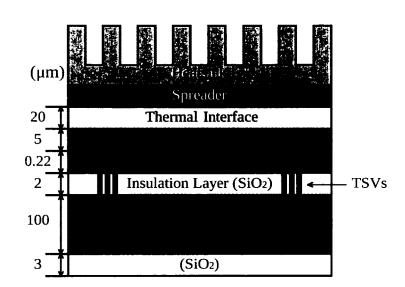

| $5 \cdot 2$  | Cross-sectional view of our target 3D manycore system                                                 | 92  |

| 5.3          | P-I characteristics of a laser source at various temperatures                                         | 96  |

| $5 \cdot 4$  | Wall-plug efficiency vs Input current at various temperatures                                         | 97  |

| 5.5          | Wall-plug efficiency vs Laser Source Lengths at various temperature .                                 | 97  |

| $5 \cdot 6$  | Laser source temperature vs. electrical input power                                                   | 98  |

| 5.7          | WPE vs optical output power for various sharing granularity                                           | 99  |

| 5.8          | The laser source sharing methods                                                                      | 101 |

| 5.9          | Effective WPE vs. sharing granularity of laser sources                                                | 103 |

| 5.10         | Flowchart for deciding the sharing and placement of on-chip laser sources                             | 104 |

| 5.11         | Total laser power vs. waveguide loss for various sharing and placement                                | 106 |

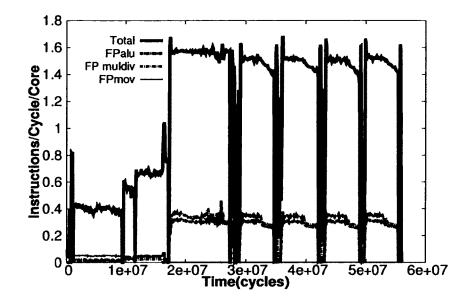

| $6 \cdot 1$  | Average per core utilization of FPUs when running FMM application on          |     |  |

|--------------|-------------------------------------------------------------------------------|-----|--|

|              | a 64-core system                                                              | 112 |  |

| 6.2          | 3D stacked manycore system                                                    | 116 |  |

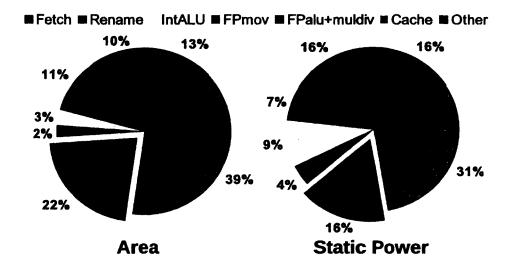

| <b>6</b> ∙3  | Breakdown of area and static power of each core                               | 118 |  |

| 6.4          | Abstract view of the main components of a processor core                      | 119 |  |

| 6.5          | Packets required to access EUCloud                                            | 121 |  |

| 6.6          | The silicon-photonic between cores and EUCloud $\ldots \ldots \ldots \ldots$  | 123 |  |

| 6.7          | NoC power for EUCloud                                                         | 125 |  |

| $6 \cdot 8$  | The execution stage using the pipelined 3-cycle ${\tt FPalu}$ unit at EUCloud | 127 |  |

| $6 \cdot 9$  | Extensions to support bundles in EUCloudOpt                                   | 130 |  |

| 6.10         | The workload allocation among EUs                                             | 131 |  |

| 6·11         | Required number of FPUs for for each 64-thread application $\ldots$ .         | 135 |  |

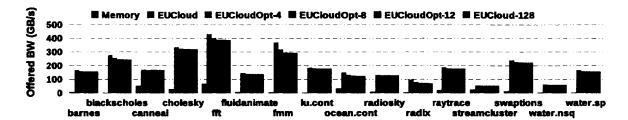

| <b>6</b> ·12 | Offered bandwidth for each 64-thread application                              | 136 |  |

| 6.13         | Performance comparison between EUCloud and EUCloudOpt $\ldots$                | 138 |  |

| 6.14         | Performance for EUCloudOpt-based manycore system                              | 140 |  |

| 6.15         | Performance for EUCloudOpt-based improved manycore system                     | 142 |  |

| 6.16         | Performance comparison Cluster vs. Global EUCloud under aggre-                |     |  |

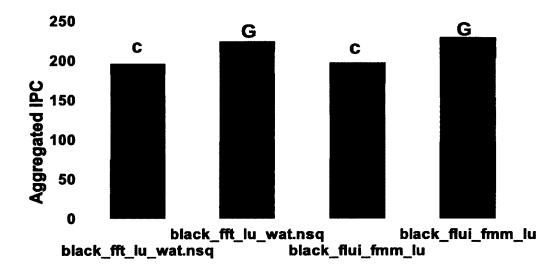

|              | gated IPC metric                                                              | 143 |  |

## List of Abbreviations

| AGU                       | <br>Address Generation Unit                    |

|---------------------------|------------------------------------------------|

| ALU                       | <br>Arithmetic Logic Unit                      |

| AMD                       | <br>Advanced Micro Devices                     |

| AP                        | <br>Access Point                               |

| AVX                       | <br>Advanced Vector Extensions                 |

| BRU                       | <br>Branch Unit                                |

| BTB                       | <br>Branch Target Buffer                       |

| $\operatorname{CAP}$      | <br>Core Access Point                          |

| CMOS                      | <br>Complementary MetalOxideSemiconductor      |

| CPU                       | <br>Central Processing Unit                    |

| DCache                    | <br>Data Cache                                 |

| $\mathbf{DC}$             | <br>Data Center                                |

| DDE                       | <br>Data-traffic Dependent Energy              |

| DWDM                      | <br>Dense Wavelength-Division Multiplexing     |

| EAP                       | <br>EUCloud Access Point                       |

| EDP                       | <br>Energy Delay Product                       |

| EEVDF                     | <br>Earliest Eligible Virtual Deadline First   |

| EUCloud                   | <br>Execution Unit Cloud                       |

| EUCloudOpt                | <br>Optimized Execution Unit Cloud             |

| $\mathbf{EU}$             | <br>Execution Unit                             |

| $\mathbf{EVC}$            | <br>Express Virtual Channels                   |

| EVC-T                     | <br>Express Virtual Channels with Taps         |

| FP                        | <br>Floating Point                             |

| FPALU                     | <br>Floating Point Arithmetic Logic Unit       |

| FPGA                      | <br>Field-Programmable Gate Array              |

| FPmov                     | <br>Floating Point Move                        |

| $\operatorname{FPmuldiv}$ | <br>Floating Point Multiplication and Division |

| FPMult                    | <br>Floating Point Multiplication              |

| FPU                       | <br>Floating Point Unit                        |

| GaAs                      | <br>Gallium Arsenide                           |

| GOPS                      | <br>Giga Operations per Second                 |

| HB                        | <br>Home Bank                                  |

| HPC                       | <br>High Performance Computer                  |

|                           |                                                |

| ICache         |                                       | Instruction Cache                                                 |

|----------------|---------------------------------------|-------------------------------------------------------------------|

| ID             |                                       | Identification                                                    |

| IEEE           |                                       | Institute of Electrical and Electronics Engineers                 |

| ILP            |                                       | Instruction-Level Parallelism                                     |

| InGaAs         |                                       | Indium Gallium Arsenide                                           |

| IntALU         |                                       | Integer Arithmetic Logic Unit                                     |

| IntMult        |                                       | Integer Multiplication                                            |

| IPC            |                                       | Instruction per Cycle                                             |

| ITRS           |                                       | International Technology Roadmap for Semiconductors               |

| LSTP           |                                       | Low Static Power                                                  |

| MECS           |                                       | Multidrop Express Channels                                        |

| MC             |                                       | Memory Controller                                                 |

| MIPS           |                                       | Million Instructions per Second                                   |

| MPSoC          |                                       | Multiprocessor System-on-Chip                                     |

| MWSR           |                                       | Multi-Writer Single-Reader                                        |

| NACK           |                                       | Negative Acknowledgement                                          |

| NACK           |                                       | National Aeronautics and Space Administration                     |

| NoC            |                                       | National Aeronautics and Space Administration<br>Networks-on-Chip |

| OoO            | •••••                                 | Out-of-Order                                                      |

| PIDRAM         |                                       |                                                                   |

|                |                                       | Photonically Interconnected DRAM                                  |

| PTM            | · · · · · · · · · · · · · · · · · · · | Predictive Technology Model                                       |

| RC             |                                       | Reconfiguration Controller                                        |

| RS             | • • • • • • • • • • • • • • •         | Reservation Station                                               |

| SCC            | • • • • • • • • • • • • • • •         | Single Chip Cloud Computer                                        |

| SIMD           |                                       | Single Instruction Multiple Data                                  |

| SiN            | • • • • • • • • • • • • • •           | Silicon Nitride                                                   |

| $SiO_2$        |                                       | Silicon Dioxide                                                   |

| SOI            |                                       | Silicon on Insulator                                              |

| SRAM           |                                       | Static Random-Access Memory                                       |

| SSE            |                                       | Streaming SIMD Extensions                                         |

| SWMR           | • • • • • • • • • • • • • • •         | Single-Write Multiple-Read                                        |

| $\mathrm{TDM}$ | • • • • • • • • • • • • • • •         | Time-Division Multiplexing                                        |

| $\mathrm{TLP}$ | • • • • • • • • • • • • • • •         | Thread-Level Parallelism                                          |

| $\mathrm{TSV}$ |                                       | Through Silicon Via                                               |

| $\mathrm{TT}$  |                                       | Thermal Tuning Circuits                                           |

| $\mathbf{VC}$  |                                       | Virtual Channel                                                   |

| VLSI           |                                       | Very-Large-Scale-Integration                                      |

| WDM            |                                       | Wavelength-Division Multiplexing                                  |

| WPE            |                                       | Wall-Plug Efficiency                                              |

|                |                                       |                                                                   |

### Chapter 1

### **Background and Introduction**

### 1.1 Trends in VLSI Computing System

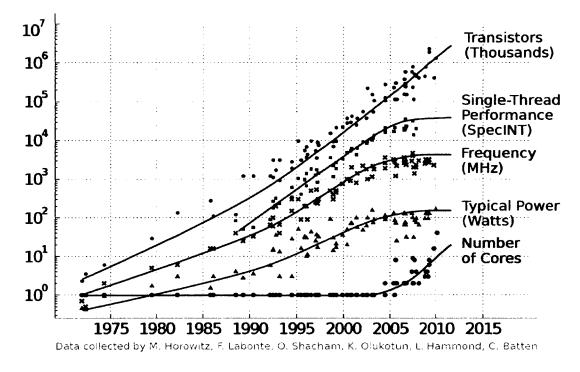

The general-purpose compute capacity of the world grew at an annual rate of 58% from 1986 to 2007 (Hilbert and Lpez, 2011). The very large scale integration (VLSI) community was able to use technology scaling to sustain this increase in compute capacity. Figure 1.1 shows the trends in transistors, performance, and power for general-purpose processors over the past three decades. As predicted by Moore's law (Moore, 1965), the number of transistors per unit area doubled approximately every two years. As the transistor number increased, processor performance was improved by designing more complicated core architecture and using higher core frequency. The MIPS R2000 had 110K transistors, ran at 16.7 MHz, had no on-chip caches, and used a very simple five-stage pipeline. It had a total compute capacity of 12 MIPS in 1985. Intel Pentium 4 processor released in 2000, had 42M transistors, ran at 2.0+ GHz, included large on-chip caches, and used a 20-stage pipeline with superscalar issue and a 126-entry reorder buffer for deep out-of-order execution. The compute capacity of the Pentium 4 Extreme Edition was 9,726 MIPS at 3.2 GHz in 2005.

Around 2005, the computing community hit the proverbial "power wall". Hence, to sustain the historic performance improvement implied by Moores law, processors were

Figure 1.1: Trends in transistor count, performance, core count and power over the past decades

designed to have multiple cores on a single die. Today's systems have hundreds of cores on a single die. The TILE64 processor released in 2008 has 64 title processors that are connected through 2D mesh network. The compute capacity of TILE64 processor was up to 384 aggregate GOPS at 750 MHz. The Intel Single-chip Cloud Computer (SCC) (Howard et al., 2010), released in 2009, enabled Tera-scale computing research. It integrated 48 Pentinum class IA-32 cores that were connected through a 2D mesh network. The core count on the processor is expected to increase into the thousands in the near future.

### 1.2 Electrical NoC

These processors with large number of cores on a chip require the design of scalable energy-efficient network-on-chip (NoC) for on-chip communication. Most contemporary multicore processors use electrical link technology for communication among the cores. The performance of these electrical NoC affects the latency of each individual cache/memory access and in turn affect the performance of the entire manycore system. The bus topology was widely used in multicore processors with less than ten cores. However, to provide the bandwidth required by a manycore system with tens to hundreds of cores, researchers have proposed various NoC topologies, ranging from low-radix high-diameter mesh network to high-radix low-diameter crossbar network (Dally and Towles, 2003). Several commercial systems such as Tilera (Bell et al., 2008) and Intel Single-Chip Cloud (SCC) (Howard et al., 2010) use low-radix high-diameter mesh network. This mesh network is easy to design in hardware using repeater-inserted electrical links. Several high-radix and low-diameter network topologies, such as flattened butterfly, clos, and MECS (Kim et al., 2007; Joshi et al., 2009; Grot et al., 2009) have been proposed for lower network latency distribution. These network topologies provide low network latency distributions and high network throughput by connecting distant routers with physical express channels. However, the energy overhead of physical express channels makes it difficult to justify their use for current and future power-limited systems. To improve the performance of low-radix and high-diameter network topologies, express virtual channels (EVC) and the corresponding flow control technique have been proposed in (Kumar et al., 2008). This technique enables the intermediate routers to forward the received packets immediately without buffering, arbitration, and crossbar switching. However, EVC is not efficient for transmitting broadcast packets due to the multiple transmissions of one broadcast packet on the same physical channel. To support effective transmission of broadcast packets, we extend the traditional EVC technique to express virtual channel with taps (EVC-T) that has multiple taps along the EVC. This approach transmits both broadcast packets and data packets with reduced traffic overhead and

network latencies.

In Addition, these packet switch-based NoC cannot maintain the packet order due to the variations in transmission distance and contentions in packet routing. However, maintaining the order of broadcast packets is critical for cache coherency. A number of techniques have been proposed for resolving the packet ordering issue in the NoC. Ordered broadcast trees and ring topologies address the cache coherence problem on packet switch-based NoCs by creating ordering points (Charlesworth, 2002; Marty and Hill, 2006). Although the ordering points method in these techniques is convenient and straightforward, the technique increases packet latency. A similar approach has been proposed in (Strauss et al., 2007), where a ring cache coherence protocol is used for ordering. In this case, in addition to the snoop request broadcast, the requester also initiates a response message that collects responses from all nodes as it travels around the ring. A global ordering of networks has been proposed using isotach-like networks in (Reynolds et al., 1997; Bilir et al., 1999; Williams et al., 2000). To maintain the orders of broadcast packets, some approaches use snoop ordering (Agarwal et al., 2009). This method avoids using the ordering points. However, the received broadcast packets have to wait for other packets with lower snoop orders, which reduces system performance. We propose a broadcasting technique with notification trees as the supporting networks for cache coherence. Our broadcasting technique allows caches to process received broadcast packets with much shorter waiting time and limited hardware overhead.

### 1.3 Silicon-photonic NoC

#### 1.3.1 Laser Power Management

In future manycore systems that have hundreds to thousands of cores integrated on a single chip, the electrical links may not be able to provide the required bandwidth within reasonable power budgets. Silicon-photonic link technology has been extensively explored as a potential replacement to the electrical link technology in the design of NoC for manycore systems. Researchers have explored silicon-photonic implementations of the entire spectrum of network topologies. The large number of global buses needed for the high-radix low-diameter crossbar that provide non-blocking connectivity can be efficiently implemented using silicon-photonics technology (Kirman et al., 2006; Psota et al., 2010; Vantrease et al., 2008). The silicon-photonic implementation of low-radix high-diameter networks like mesh and torus lying at the other end of the network spectrum have also been investigated (A. Shacham, K. Bergman and L. P. Carloni, 2007; Kirman and Martínez, 2010; Cianchetti et al., 2009; Petracca et al., 2008). Silicon-photonic designs of intermediate network topologies like Clos and fat-tree that offer the same network guarantees like the global crossbar with potentially lower resource requirements have also been explored (Gu et al., 2009; Joshi et al., 2009; Pan et al., 2009).

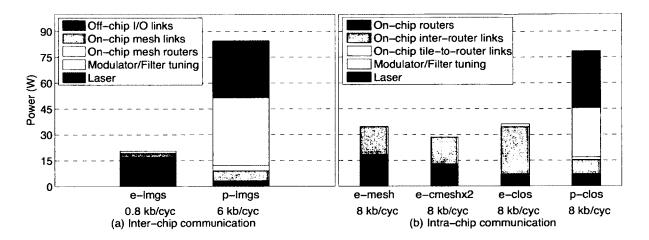

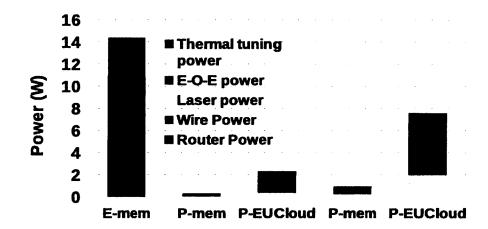

A general consensus among the various efforts so far is that silicon-photonic networks provide a bandwidth density and data-dependent energy advantage for NoC communication. However, the fixed amount of power consumed in the laser sources that drive these networks negates these advantages. Figure 1.2 shows the power breakdown in the electrical and photonic local meshes global switches (lmgs) interchip network (Batten et al., 2008), and electrical mesh, electrical concentrated mesh (cmesh), electrical Clos and photonic Clos intra-chip networks for the listed target

Figure 1.2: Power breakdown of manycore network – Power breakdown in the electrical and photonic local meshes global switches (lmgs) inter-chip network (Batten et al., 2008), and electrical mesh, electrical concentrated mesh (cmesh), electrical Clos and photonic Clos intra-chip networks for the listed target bandwidths. Laser power and modulator/filter tuning power more than offsets any power savings in the data-dependent power of the silicon-photonic link. Uniform random traffic pattern was used for evaluating both networks. For modulator/filter tuning, we assumed a tuning cost of 10  $\mu$ W per K per ring and a tuning range of 20 K. For the laser source power, we assumed the laser source has an efficiency of 30% (Batten et al., 2008; Joshi et al., 2009).

bandwidths. As shown in Figure 1.2, a non-trivial amount of power is required in the laser source that is used in driving the silicon-photonic networks and in tuning of modulators and filters against thermal variations. In fact, the laser power and thermal tuning power can more than offset the bandwidth density and data-dependent energy advantages of the silicon-photonic links. To use silicon-photonic link technology in future manycore system, we need to reduce these two sources of power consumption. To enable the use of silicon-photonic NoC in future manycore systems, we need to develop techniques to proactively manage laser power.

At the device level, standard design-time solutions to reduce optical loss in siliconphotonic devices and in turn reduce the laser power range from exploring different materials to process flows to device geometries. At the circuit level, we can explore the design of receivers that can operate with low-sensitivity photodetectors or use photonic devices that have lower losses but are more susceptible to noise (Bauters et al., 2011; Bauters et al., 2013), and use error detection/correction techniques to tackle any errors. At the architecture level, a nanophotonic crossbar architecture that uses optical channel sharing to manage static power dissipation is proposed in (Pan et al., 2010). Here a token-stream mechanism is used for channel arbitration and credit distribution, to enable efficient global sharing of crossbar channels. Similarly, a reconfigurable photonic network for board-to-board communication is proposed in (Kodi and Louri, 2011) for improving performance and reducing power. Here, depending on the network traffic, idle channels are reallocated to busy channels to improve performance, and bit rate and supply voltages of individual channels are regulated to manage power. In (Li et al., 2012b), the authors propose to divide the photonic NoC into subnets and also share photonic channels for sending arbitration and data packets to reduce laser power. In (Zhou and Kodi, 2013), the authors propose a prediction mechanism to dynamically scale the NoC bandwidth depending on the demands of the overlying application and in turn reduce optical power consumption.

For a multi-bus silicon-photonic NoC, we propose to use time-division multiplex to control the photonic bandwidth output from the laser source across all the channels based on weights that change at runtime to maximize the manycore system performance. We switch ON/OFF the laser source (i.e. reduce the net bandwidth of the network) to further reduce laser power. The ultimate goal is to maximize the overall execution efficiency of the manycore system. The decisions on the magnitude of change of the multiplexing weights and network bandwidth (through switching ON/OFF of laser sources) are made based on the average network packet latency for an application over fixed sampling intervals. Our technique ensures that the application runs at peak performance while consuming minimum amount of laser power. We have also proposed a multi-bus NoC architecture that is well suited to the proposed weighted time-division multiplexing technique and have presented a head-to-head comparison of this multi-bus NoC architecture with conventional Clos and butterfly NoC architecture. A time-division multiplexed arbitration technique for silicon-photonic mesh NoC is proposed in (Hendry et al., 2011). In contrast to our runtime approach, here the time division-multiplexed photonic paths between the various pairs of network access points are established statically during design time and do not change at runtime. The key idea is to provide complete network connectivity, with each pair of access points getting fair access to large network bandwidth.

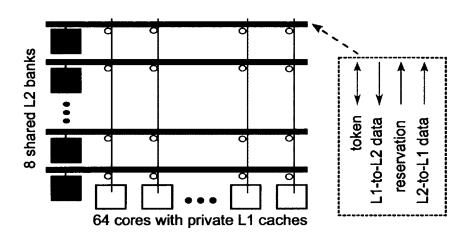

We also propose to manage the laser power consumed in the silicon-photonic NoC between the private L1 cache and distributed shared L2 cache using cache reconfiguration. In our approach, we determine the minimum number of L2 cache banks that are required to sustain the application performance. The extra L2 cache banks are deactivated and the silicon-photonic links associated with those L2 cache banks are also switched OFF to save laser power. The idea of reconfiguring the cache architecture to reduce cache energy and/or improve performance has been explored in the past (Sim et al., 2012; Qureshi et al., 2007; Wu et al., 2011). However, it has never been used to manage the power consumed in a silicon-photonic NoC. The main goal here is to minimize the EDP of the overall manycore system by leveraging the spatial and temporal variations in the behavior of the applications.

#### 1.3.2 On-chip Laser Source

A widespread adoption of silicon-photonic link technology in designing the NoC of manycore systems is not yet possible as packaging a silicon-photonic manycore system where several off-chip laser sources drive the photonic NoC through optical fibers is extremely challenging. Hence, on-chip laser sources are being considered as a potential alternative to these off-chip laser sources for driving the silicon-photonic NoC (Kurian et al., 2012; Heck and Bowers, 2014). These on-chip laser sources can be on the layer adjacent to the layer containing the photonic devices, making it easier to couple the laser source output to the photonic NoC. In addition to packaging challenges, the fixed power consumed in the laser sources and the power consumed in thermal management of the photonic links can be non-trivial and can negate the bandwidth advantages of silicon-photonic links. These on-chip laser sources can be switched ON/OFF relatively quickly compared to off-chip laser sources making them compatible with the runtime laser power management techniques (Chen and Joshi, 2013; Li et al., 2012a; Zhou and Kodi, 2013) that have been proposed. Similarly, given that laser sources are on the layer next to the photonic device layer it would be easier to match the temperatures of the laser source and the photonic devices, which would in turn make the thermal management techniques (Zhang et al., 2014; Nitta et al., 2011; Zheng et al., 2012; Li et al., 2012b) more effective.

Several automated tool flows have been developed to enable rapid exploration of the silicon-photonic link design space as well as the silicon-photonic NoC design space. In (Ding et al., 2009), the authors propose a linear programming technique to design the physical layout of the photonic devices on a separate photonic layer with the goal of minimizing the power consumed by an off-chip laser source. Similarly, in (Condrat et al., 2013), the authors propose a methodology to route the photonic waveguide such that the number of waveguide crossings is minimized. For a comprehensive evaluation of the photonic network design space, the authors in (Chan et al., 2011) propose a methodology and a tool that jointly explores the link-level and system-level designs of the network topologies. In (Hendry et al., 2011), the authors propose a toolflow for placement and routing of photonic devices to hierarchically design large

complex photonic networks. In (Boos et al., 2013), the authors have proposed a tool for placement and routing of optical NoC topologies with the goal of enabling a realistic analysis of the optical NoC design space. We explore the design space for sharing and placement of on-chip laser sources. Our analysis jointly considers NoC bandwidth constraints, thermal constraints and physical layout constraints to determine the optimal sharing as well as the placement of the on-chip laser sources with the goal of minimizing the laser power consumption. The approach that we have adopted can be easily integrated with the design automation tools described above to generate an optimal end-to-end design of the NoC.

#### 1.3.3 The Use of Large Bandwidth

The idea of sharing computational resources such as floating point units has already been demonstrated as an efficient strategy to save power and chip area. Processor architectures that share floating point units have already been introduced by several commercial vendors including IBM (Meltzer, 1999), Texas Instrument (Kahle and Moore, 2000), Sun/Oracle (Leon et al., 2006) and AMD (McIntyre et al., 2012). These processor architecture designs are however only suitable for small core counts and do not readily scale to large core counts. Recently, (Kakoee et al., 2013) proposed a shared FPU for low-power embedded MPSoCs. They rely on a dedicated interconnection network to convey all traffic to access a shared set of FPUs, along with a FPU allocator that assigns processor's requests to available FPUs. This design can only support a small processor count as the overhead of a dedicated network scales non-linearly with core count. FPU Sharing has also been proposed in the context of FPGAs (Castells-Rufas et al., 2011) leading to significant area savings with minimal performance degradation for a modest scale of sharing.

Contemporary solutions cannot adapt well to hundreds of processor cores in future

manycore systems targeting multi-programmed workloads and/or server consolidation scenarios. The localized sharing of FPUs among a reduced fraction of processor cores can lead to significant performance losses when applications belonging to a multiprogrammed workload need more FPUs than those available in a manycore partition, or over-provisioned partitions for applications that need less number of FPUs than the number of FPUs that are available in the partition. To maximize the savings in area and power, we propose a novel EUCloud-based manycore that implements efficient global sharing of computing resources without degrading application/workload performance, by leveraging low-latency and high-bandwidth density of silicon-photonic technology.

### 1.4 Contribution and Organization

In Chapter 2, we present the use of a contention-free notification tree per core as a supporting network for broadcasting to maintain the sequential consistency for snoop-based cache coherence. These notification trees ensure each core knows when to expect a broadcast packet and the exact timestamp when a broadcast packet was generated. This information guarantees that on average a core has to wait for less than a cycle before it can make the decision about processing a broadcast packet and all the broadcast packets are processed in the correct order. We also present the use of EVC-T flow control mechanism to transmit both broadcast and data packets in a snoopbased cache coherency protocol to achieve low network latency and save energy. For broadcast packets while forwarding them to downstream routers to receive and store broadcast packets while forwarding them to downstream routers simultaneously. For NAS parallel benchmarks (Bailey et al., 1994), EVC-T reduces the average packet latency (data and broadcast) by 24% and improves the system energy efficiency, reducing the energy delay product (EDP) by 13% on average. In Chapter 3, we present a silicon-photonic multi-bus NoC architecture between private L1 caches and distributed L2 cache banks that uses weighted time-division multiplexing (W-TDM) to distribute the laser power across multiple buses based on the runtime variations in the bandwidth requirements within and across applications to maximize energy efficiency. The multi-bus NoC architecture also harnesses the opportunities to switch OFF laser sources at runtime, during low bandwidth requirements, to reduce laser power consumption. Using detailed system-level simulations, we evaluate the multi-bus NoC architecture and runtime laser power management technique on a 64-core system running NAS parallel benchmark suite. The silicon-photonic multi-bus NoC architecture provides more than  $2\times$  better performance than siliconphotonic Clos and butterfly NoC architectures, while consuming the same laser power. Using runtime laser power management technique, the average laser power is reduced by more than 49% with minimal impact on the system performance.

In Chapter 4, we present a runtime management technique to reduce the laser power dissipation at by dynamically activating/deactivating L2 cache banks and switching ON/OFF the corresponding silicon-photonic links in the NoC. Since the total laser power dissipation depends on the number of on-chip silicon-photonic links, this method effectively throttles the total on-chip NoC bandwidth at runtime according to the memory access features of the applications running on the manycore system. Full-system simulation utilizing PARSEC and SPLASH parallel benchmarks (Bienia et al., 2008; Woo et al., 1995) reveal that our proposed technique achieves 23.8% savings in laser power and 5.52% lower energy-delay product (EDP) for the whole system at the cost of 0.65% loss in IPC on average.

In Chapter 5, we propose the sharing and placement methodology of on-chip laser sources that simplify packaging and lower photonic losses in the links, compared to off-chip laser sources. The electrical input power of these laser sources is dependent on the laser source temperature and the optical output power. The laser source temperature depends on the power consumed by the laser as well as the cores in the laser's neighborhood, while the optical output power of the laser source depends on the network bandwidth requirements and physical layout of the network. We first explore the power, efficiency and temperature tradeoffs associated with on-chip laser source. After that, using a 3D manycore system, we explore the design space for sharing and placement of the laser source by jointly considering the network bandwidth requirements, thermal constraints and physical layout constraints to determine the optimal sharing and placement of the laser sources, which minimizes the laser power. As part of this exploration we consider three different topologies – 8-ary 3-stage Clos, 16-ary 3-stage Clos and 16 x 16 crossbar, two different physical layouts – U-shaped and W-shaped and three different sharing/placement strategies – locally-placed laser sources with no sharing, locally-placed laser sources with sharing and laser sources placed along the edge with sharing. Our analysis shows that depending on the network topology, physical layout and waveguide losses, the sharing granularity and placement decisions of the laser source changes.

Finally, in Chapter 6, we present a manycore architecture that uses silicon-photonic links that features high bandwidth density and low latency communication, to achieve efficient global sharing of computing resources located in a globally-shared Execution Unit Cloud (EUCloud). Manycore systems exploit massive thread-level parallelism sacrificing instruction-level parallelism. This translates into lower utilization of the core's execution units (EUs) that creates opportunities for sharing of EUs (rather than using the complete set of EUs per core), which in turn can reduce area and static power. EU sharing is implemented in today's systems, but these mechanisms are not devised to adapt well to manycore systems running multi-programmed workloads or server consolidation scenarios. We consider a 256-core processor manufactured at 16 nm, an EUCloud composed of Floating Point Units (FPUs), and we use multi-programmed workloads with a representative set of benchmarks to evaluate the EUCloud architecture. Our analysis shows that FPUs have a maximum of 20% utilization rate for the most FPU-intensive workload but occupy around 22% of the entire core area and consume 16% of static power. In our proposed manycore system with EUCloud, to sustain application performance we need just 96 FPUs instead of the 256 FPUs in the nominal case, which results in 13.75% and 10% reductions in the total manycore area and power respectively. We harness the unused area and power budgets of each core to boost performance by using larger caches achieving 8.13% performance improvement for the nominal power budget. Alternately, we can increase the core complexity, thus leading to 29.4% higher performance for an 8% increase in power budget.

### Chapter 2

# Broadcast through Express Virtual Channel with Taps in Electrical NoC

### 2.1 Introduction

The general trend for NoC architectures is towards designing low-radix high-diameter network topologies (e.g., mesh) that have short router-to-router channels (Bell et al., 2008; Howard et al., 2010). These topologies are easier to design from the hardware perspective. However, mapping an application to these topologies is difficult due to the large variance in packet latencies. High-radix low-diameter topologies such as crossbar are more amenable to application mapping due to low network diameters, but are difficult to design from the hardware perspective because of the long wires.

Another issue with NoC-based manycore systems is maintaining cache coherency across multiple caches. Previously, snoop-based and directory-based cache coherency protocols have been investigated for manycore systems (Culler et al., 1998). Snoopbased cache architecture uses a broadcasting mechanism for cache coherency, and is commonly used for bus-based topology in systems with a small number of cores

<sup>&</sup>lt;sup>1</sup>This chapter was previously published. © 2011 IEEE. Reprinted with permission from Chao Chen, Jie Meng, Ayse K. Coskun and Ajay Joshi, "Express Virtual Channels with Taps (EVC-T): A Flow Control Technique for Network-on-Chip (NoC) in Manycore Systems," 2011 IEEE 19th Annual Symposium on High Performance Interconnects (HOTI), August 2011 (Chen et al., 2011)

(e.g., fewer than 10 cores). This protocol, however, does not scale well for NoC-based manycore systems due to the packet latency distribution.

To harness the true potential of manycore systems we need to develop low-cost, highperformance and energy-efficient NoC architectures. This chapter makes two contributions towards achieving this goal. First, we propose a new broadcasting mechanism for snoop-based cache coherency protocol for manycore systems. Each core uses a dedicated notification tree to rapidly inform all other cores of an incoming broadcast message. In this way, other cores can make early decisions to wait for the packet or to proceed with execution in presence of simultaneously transmitted packets over the shared network. The proposed broadcast mechanism has higher performance in comparison to conventional snoop-based broadcast mechanisms for low network traffic. For high network traffic, the performance of the proposed approach is similar to the conventional approaches.

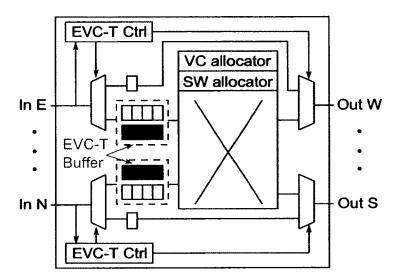

We also propose a novel network flow-control mechanism: Express Virtual Channels with Taps (EVC-T) (Chen et al., 2011). Our flow-control mechanism, when mapped to a physical concentrated mesh (cmesh) network, results in a logical topology with high radix and low diameter. As a result, this NoC is easy to design from the hardware perspective and easy to program. The logical topology is similar to multidrop express channel (MECS) (Grot et al., 2009). However, unlike MECS, the proposed logical topology supports both data and broadcast packets, and does not use physically separated express channels.

Our novel contributions in the area of broadcast in electrical NoC are as follows:

• To maintain the sequential consistency for snoop-based cache coherence, we propose using a contention-free notification tree per core as a supporting network for broadcasting. These notification trees ensure each core knows when to expect a broadcast packet and the exact timestamp when a broadcast packet was generated. This information guarantees that on average a core has to wait for less than a cycle before it can make the decision about processing a broadcast packet and all the broadcast packets are processed in the correct order.

• To achieve low network latency and save energy, we propose EVC-T flow control mechanism to transmit both broadcast and data packets in a snoop-based cache coherency protocol. For broadcasting, our EVC-T technique allows intermediate routers to receive and store broadcast packets while forwarding them to downstream routers simultaneously. For NAS parallel benchmarks (Bailey et al., 1994), EVC-T reduces the average packet latency (data and broadcast) by 24% and improves the system energy efficiency, reducing the energy delay product (EDP) by 13% on average.

In this chapter, Section 2.2 provides the details of our target system. Section 2.3 explains the use of notification trees as supporting networks for cache coherence. Section 2.4 describes the EVC-T flow control technique. Section 2.5 evaluates our techniques using synthetic traffic and the NAS parallel benchmarks. Section 2.6 summarizes our analysis.

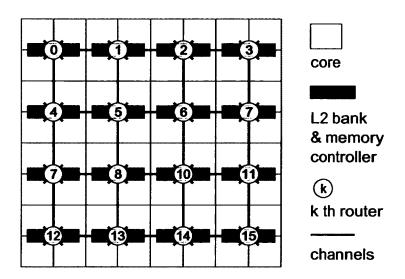

### 2.2 Target System

We choose a 64-core processor as our target system that is manufactured using 22 nm technology process as a representative node for future manycore chips (Kuhn et al., 2010). Each core on the processor supports 2-way issue out-of-order execution, and has two integer ALUs, one integer multiplication unit, one floating-point ALU, and one floating-point multiplication unit. The core architecture is configured based on the cores used in Intel's 48-core SCC (Howard et al., 2010). The micro-architectural

parameters are listed in Table 2.1. The cores operate at 1 GHz frequency and have a supply voltage of 0.9 V, while the on-chip network operates at 2 GHz.

Each core has 16 KB private L1 instruction cache and 16 KB private L1 data cache. We use a shared memory programming model and explore a distributed L2 cache architecture. The manycore system uses the snoop-based MESI protocol for maintaining the cache coherence.

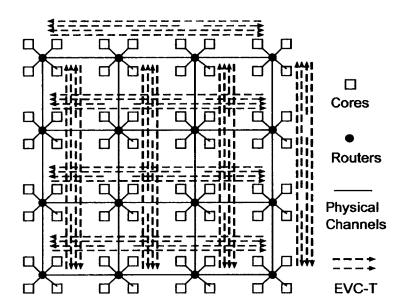

Figure 2.1 shows the physical layout of our 64-core target system. There are 64 cores, 16 L2 cache banks (1 MB each), 16 memory controllers that are uniformly distributed across the chip. Four cores and one L2 bank share one router and communicate with other cores and L2 banks through the on-chip network. Each memory controller is associated with one L2 bank and there is a dedicated channel between them, which is not shown in Figure 2.1. Each router has four-cycle zero-load latency for the four pipelined routing stages: route computation, virtual channel allocation, switch allocation, and switch traversal (Krishna et al., 2009). After energy optimization by repeater insertion, each 5 mm channel between two neighboring routers has singlecycle latency.

| Micro-architecture Configuration |                                               |  |

|----------------------------------|-----------------------------------------------|--|

| Core Frequency                   | 22nm, 1.0 GHz @ 0.9 V                         |  |

| Branch Predictor                 | Tournament predictor                          |  |

| Issue                            | 2-way Out-of-order                            |  |

| Reorder Buffer                   | 128 entries                                   |  |

| Functional Units                 | 2 IntALUs, 1 IntMult, 1 FPALU, 1 FPMult       |  |

| Physical Regs                    | 128 Int, 128 FP                               |  |

| Instruction Queue                | 64 entries                                    |  |

| Private L1 I/D-Cache             | 16 KB each @ 2 ns                             |  |

| Distributed L2 Cache             | 4-way, 64B/block, 16 x 1 MB @ 6 ns            |  |

| Cache Coherence                  | Snoop based MESI (Papamarcos and Patel, 1984) |  |

| NoC                              | mesh @ 2.0 GHz                                |  |

| Memory                           | 16 MCs @ 100 ns                               |  |

Table 2.1: Micro-architectural parameters of the 64-core system

Figure 2.1: Physical layout of our 64-core system with electrical NoC. – 16 L2 cache banks (1 MB each) are uniformly distributed across the chip. Each L2 bank has one memory controller physically located next to it. Each router uses a concentration of 4 cores and one L2 cache bank. It has 13 input and 13 output ports (4 for inter-router interconnect, 8 for L1 I-cache and D-caches of 4 cores, and 1 for 1 L2 cache bank).

### 2.3 Notification Trees for Broadcasting Order

For network topologies such as cmesh, clos or crossbar, where the network enables parallel accesses, multiple sources can insert packets into the network at the same time. The latency of each packet varies based on the traffic workload as well as the physical location of its source L1 cache. Therefore, a destination L1 cache can potentially receive broadcast packets in a different order than the original order in which the broadcast packets were generated. Hence, a destination L1 cache needs to wait for all broadcast packets that are on the fly before processing the received broadcast packet. The worst-case waiting time can be determined using empirical methods. However, depending on the size of the manycore system, the waiting period could be considerably long, which has a negative impact on the system performance. In our 64-core target system with a cmesh network, the cores at the corners have

| )  | 1   | 2  | 3  | 4   | 5   | 6  | 7  |

|----|-----|----|----|-----|-----|----|----|

| 8  | 9   | 10 | 11 | 12  | 13  | 14 | 15 |

| 16 | .17 | 18 | 19 | 20, | 21  | 22 | 23 |

| 24 | 25  | 26 | 27 | 28  | 29  | 30 | 31 |

| 32 | /33 | 34 | 35 | 36  | 37  | 38 | 39 |

| 40 | 41  | 42 | 43 | 44  | 45  | 46 | 47 |

| 48 | 49  | 50 | 51 | 52  | /53 | 54 | 55 |

| 56 | 57  | 58 | 59 | 60  | 61  | 62 | 63 |

|    |     |    | (a | )   |     |    |    |

**Figure 2.2: Example of Notification trees** – (a) Notification tree from core 0. (b) Notification tree from core 18.

to wait for more than 34 cycles assuming the shared cmesh network has zero-load latency. As the network traffic becomes high, the waiting time increases because of network contention. When an L1 cache knows in advance how many cycles to wait for the broadcast packets that are already on-the-fly, we can avoid the wasted cycles at the cache.

We propose using notification trees along with the existing shared network to maintain the sequential consistency of broadcast packets that are transmitted on unordered interconnects. Each L1 cache in a core has a dedicated notification tree, connecting it to all other L1 caches. Figure 2.2 shows the notification trees from the L1 caches in core 0 and core 18. Each notification tree is pipelined and each pipeline segment uses energy-optimized repeater-inserted single-bit wire.

The notification tree for an L1 cache sends a notification pulse to all other destination L1 caches whenever it has a read/write cache miss, and a new broadcast packet requesting the missing cache line is generated. The actual broadcast packets

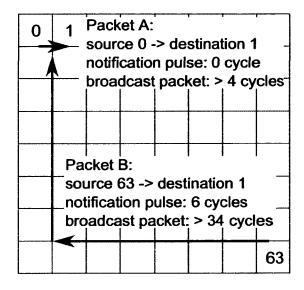

**Figure 2.3: Example of broadcast packets** – Here, broadcast packets are sent from core 0 and core 63 to ALL receivers across the chip. For clarity, only one receiver is shown.

are transmitted over the shared network. As the notification trees are contention free, the notification pulses reach destination L1 caches within fixed latencies. Thus, each destination L1 cache can determine the exact waiting time before other received broadcast packet get processed. The waiting time of any broadcast packet is calculated by subtracting the broadcast packet transmission time from the notification transmission time for the farthest network source. The maximum waiting time in a destination L1 cache depends on its physical location relative to other L1 caches.

**Table 2.2: Timing analysis of the notification tree architecture** – Notification arrival time corresponds to the latency of a notification pulse through the dedicated notification tree. Packet arrival time corresponds to the zero-load latency of a broadcast packet traveling through the shared cmesh network.

| Packet<br>ID | Source<br>Core                         | Send<br>Time |                                       | Notification<br>Arrival<br>Time         | Packet<br>Arrival<br>Time                 |

|--------------|----------------------------------------|--------------|---------------------------------------|-----------------------------------------|-------------------------------------------|

| A<br>B       | $\begin{bmatrix} 0\\ 63 \end{bmatrix}$ | Т<br>Т-1     | $\begin{vmatrix} 1\\ 1 \end{vmatrix}$ | $\begin{array}{c} T \\ T+5 \end{array}$ | $\begin{array}{c} T+4\\ T+33 \end{array}$ |

Figure 2.3 shows an example for two broadcast packets: packet A and packet B from the L1 caches in core 0 and core 63, respectively. Packet A reaches the L1 cache of core 1 after traveling through one router, resulting in a zero-load latency of 4 cycles. Packet B reaches the L1 cache in core 1 after traveling through 7 routers and 6 channels, resulting in a zero-load latency of 34 cycles. On the other hand, the notification pulses for both packets reach their destinations much faster. The notification pulse for packet A reaches the L1 cache in core 1 right after packet A is generated and the notification pulse for packet B reaches the L1 cache in core 1 in 6 cycles after traveling through 6 wire segments on the notification tree.

In our analysis, packet A is generated at time 'T', while packet B is generated at time 'T-1'. The notification pulses for packet A and B reach the L1 cache in core 1 at time 'T' and 'T+5', respectively. To maintain cache coherency, packet B has to be processed before packet A. After the L1 cache for core 1 receives the broadcast packet A at 'T+4', it monitors the notification trees for the remaining L1 caches for an additional cycle. The 1-cycle waiting time is calculated based on the fact that the core 63 is farthest away from core 1, and it takes 6 cycles for a notification pulse to be transmitted from the L1 cache in core 63 to the L1 cache in core 1. As the L1 cache in core 1 receives the notification for packet B at 'T+5', it can formulate the correct order for processing the packets. On average, the L1 cache in a core has to monitor the notification trees for less than a cycle before it can decide on the broadcast packet processing order. The exact time when a broadcast packet is processed depends on the network latency of the broadcast packet. Table 2.2 shows the timing analysis of these two broadcast packets at their sources (core 0 and core 63) and at the destination (core 1) as an example.

The overall hardware overhead for the proposed broadcast technique includes 64 notification trees, buffers in each core to store incoming notifications, and combinational logic in each core to decide on the processing order. The area overhead of 64 notification trees is 31% with respect to the wiring area of the existing shared network and the power overhead is 0.27 W. The area and power overheads for buffers and combinational logic are negligible. The total hardware overhead can be reduced by  $4\times$ using a shared architecture, where a group of 4 cores shares a notification tree.

# 2.4 EVC-T Flow Control Mechanism

In this section, we propose a novel flow control mechanism that, when used with a low-radix high-diameter physical network, provides a high-radix low-diameter logical topology. This reduces the network latency for broadcast and data packets, and there-fore improves the manycore system performance. We introduce the traditional EVC flow control mechanism as the background at first, and then describe our proposed EVC-T flow control mechanism and its application in our target system.

## 2.4.1 Express Virtual Channels (EVC)

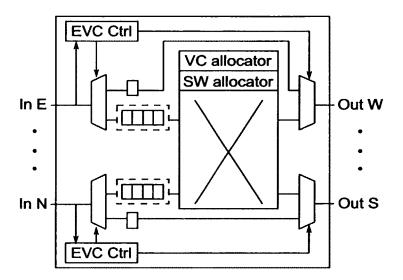

The EVC flow control mechanism proposed in (Kumar et al., 2008) enables packets to entirely bypass routers. Figure 2.4 shows the router architecture supporting EVCs. Each router receives four types of packets – a packet generated by a core connected to that router, a packet that will bypass the router, a packet that will change direction (X  $\rightarrow$  Y) in the router, and a packet that has one of the attached core as its destination. The EVC controllers at the input ports differentiate between the packets that will be buffered by the router (change direction, get ejected to, or are injected from an attached core) and those that will bypass the router. The packets that bypass the router get priority to access the downstream inter-router physical channel among all packets.

**Figure 2.4:** The router architecture for EVC (Kumar et al., 2008). A packet received at an intermediate router of an EVC is immediately forwarded to the subsequent physical channel of the same EVC. A packet received at a destination router of an EVC is buffered and switched to channels in another direction.

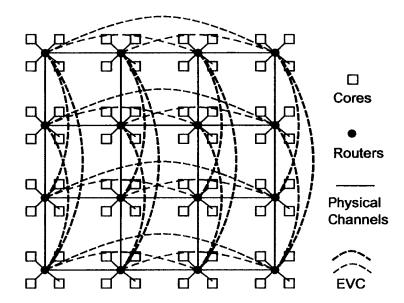

At low network traffic, when using EVCs, a data packet effectively passes through a series of inter-router channels as it bypasses all intermediate routers. As a result, it has lower latency compared to the equivalent networks with no EVCs. On the other hand, at high network traffic, the latency and saturation throughput are comparable to equivalent networks with no EVCs. Figure 2.5 shows an example network, where the network has the same physical layout as cmesh topology; i.e, it connects the neighboring routers with short physical channels. By connecting distant routers with EVCs, this network approaches the low zero-load latency of physical flattened butterfly topology while maintaining the low energy cost benefits of the traditional cmesh topology.