| ColdFire                                                                      |                                            |

|-------------------------------------------------------------------------------|--------------------------------------------|

|                                                                               |                                            |

| Babak Kia<br>Adjunet Professor                                                | California<br>California                   |

| Boston University<br>College of Engineering<br>Email: bkia <i>-at-</i> bu.edu | ENG SC757 - Advanced Microprocessor Design |

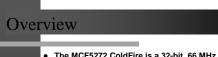

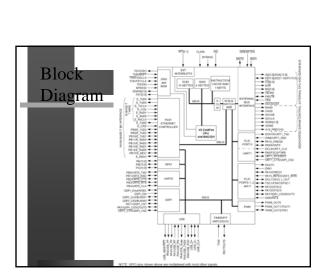

- The MCF5272 ColdFire is a 32-bit, 66 MHz processor based on the Version 2 ColdFire Core

- 4K Internal SRAM • 16K Internal ROM

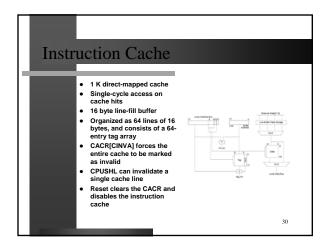

- 1K Instruction Cache

- Fully static operation with stop and sleep mode

- Individual module clock enables

- Very rapid response times to Interrupts from low power and sleep modes

- Software-controlled disable of external clock input for virtually zero power consumption

2

3

- Operating voltage of 3.3 v

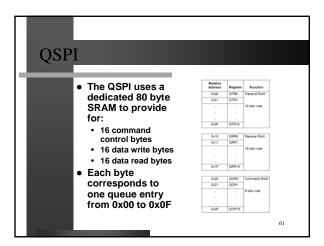

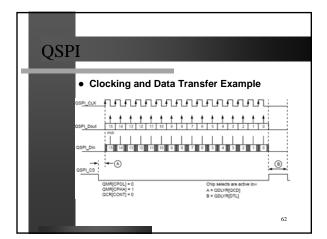

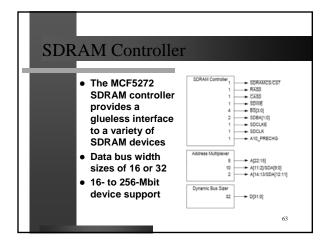

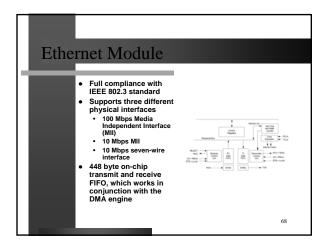

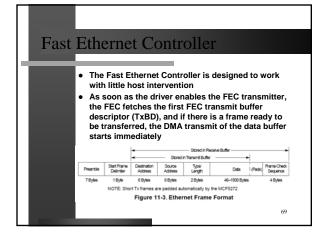

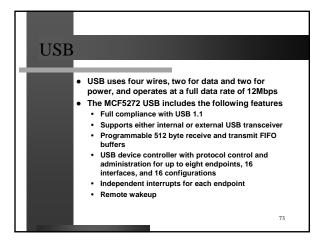

#### Peripherals IEEE 802.3 compliant 10/100 Fast Ethernet Controller (FEC), with dedicated DMA . USB 1.1 device controller and transceiver 4 TDM ports PLIC module – Intended for ISDN designs • QSPI – 16 stacked transfers • SDRAM controller 3 PWM outputs

- •

- 2 UARTs baud rates up to 5 Mbps 1-channel DMA •

- •

- 8 chip selects

- 16-bit general purpose I/Os •

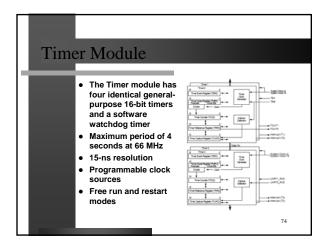

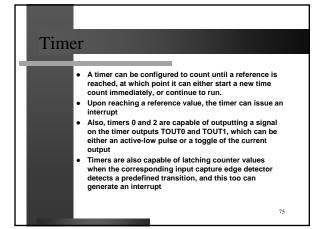

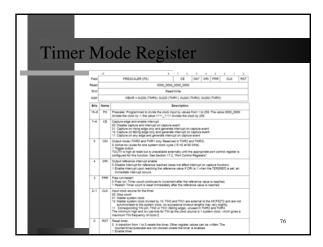

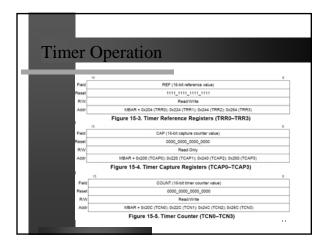

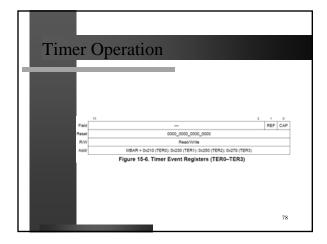

- 4 16-bit timers and SW watchdog timer

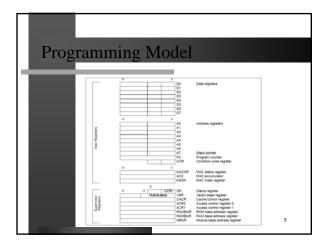

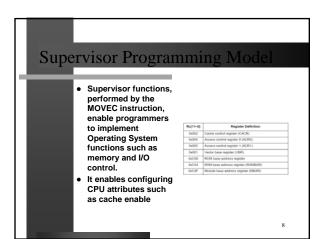

# Programming Model

- 16 general purpose 32-bit registers, A0-A7 and D0-D7

- 32-bit Program Counter

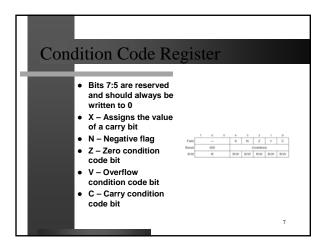

- 8-bit Condition Code Register

- Data registers can be accessed as 8, 16, or 32 bit values and can be used as index registers

- A0-A6 can be used as software stack pointers, index registers, or base address registers

6

• A7 is the system Stack Pointer

| Excep | tion           | Proc                | essing                               |                                   |  |

|-------|----------------|---------------------|--------------------------------------|-----------------------------------|--|

| _     |                |                     |                                      |                                   |  |

|       | Vector Numbers | Vector Offset (Hex) | Stacked Program Counter <sup>1</sup> | Assignment                        |  |

|       | 0              | 000                 | -                                    | Initial stack pointer             |  |

|       | 1              | 004                 | -                                    | Initial program counter           |  |

|       | 2              | 008                 | Fault                                | Access error                      |  |

|       | 3              | 00C                 | Fault                                | Address error                     |  |

|       | 4              | 010                 | Fault                                | llegal instruction                |  |

|       | 6              | 014                 | Fault                                | Divide by zero                    |  |

|       | 6-7            | 018-01C             | -                                    | Reserved                          |  |

|       | 8              | 020                 | Fault                                | Privilege violation               |  |

|       | 9              | 024                 | Next                                 | Trace                             |  |

|       | 10             | 028                 | Fault                                | Unimplemented line-a opcode       |  |

|       | 11             | 02C                 | Fault                                | Unimplemented line-flopcode       |  |

|       | 12             | 050                 | Next                                 | Debug interrupt                   |  |

|       | 13             | 034                 | -                                    | Reserved                          |  |

|       | 14             | 038                 | Fault                                | Format error                      |  |

|       | 15             | 03C                 | Next                                 | Uninitialized interrupt           |  |

|       | 16-23          | 040-05C             | -                                    | Reserved                          |  |

|       | 24             | 060                 | Next                                 | Spurious Interrupt                |  |

|       | 25-31          | 064-07C             | Net                                  | Level 1-7 autovectored interrupts |  |

|       | 32-47          | 080-08C             | Next                                 | Trap #0-15 instructions           |  |

|       |                | 000-0F0             | -                                    | Reserved                          |  |

|       | 48-60          |                     |                                      |                                   |  |

|       | 48-60          | 050-04-0            | Fault                                | Unsupported instruction           |  |

- during the first instruction of all exception handlers

- This enables the programmer to disable interrupts by raising the interrupt mask level in the status register

- There are many sources for exception, however the following usually indicate a fatal error:

| rrupt Priority                                 |                                                      |

|------------------------------------------------|------------------------------------------------------|

| inupermoney                                    |                                                      |

|                                                | -                                                    |

| Mnemonic or Portion Thereof                    | Description                                          |

| INT1, INT2, INT3, INT4, INT5, INT6             | External interrupt signals 1–6.                      |

| TMR0, TMR1, TMR2, TMR3                         | Timers 3–0 from timer module                         |

| US80, US81, US82, US83, US84, US85, US86, US87 | US8 endpoint 0-7                                     |

| UART1, UART2                                   | UART1, UART2 modules                                 |

| PLIP                                           | PLIC 2-KHz periodic interrupt, 28+D data             |

| PLIA                                           | PLIC asynchronous and maintenance channels interrupt |

| DMA                                            | DMA controller interrupt                             |

| Mnemonic or Portion Thereof                    | Description                                          |

| ETx                                            | Ethernet module transmit data interrupt              |

| ERx                                            | Ethernet module receive data interrupt               |

| ENTC                                           | Ethernet module non-time-critical interrupt          |

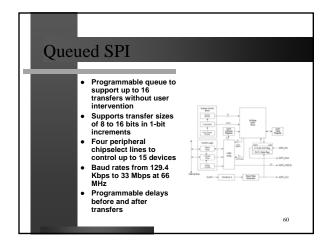

| QSPI                                           | Queued serial peripheral interface                   |

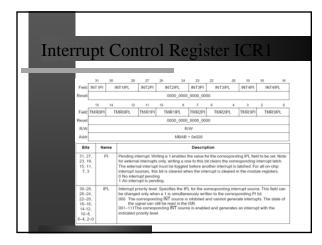

| IPL2, IPL1, IPL0                               | Interrupt priority level bits 2–0                    |

| PI                                             | Pending interrupt                                    |

| PDN                                            | Power down enable                                    |

| WK                                             | Wakeup enable                                        |

| SWTO                                           | Software watchdog timer time out                     |

| Tret |               | la ata.  | T-1-1    |                            |

|------|---------------|----------|----------|----------------------------|

| Inte | errupt V      | ecto     | r I adie | 2                          |

|      |               |          |          |                            |

|      |               |          |          |                            |

|      |               |          |          |                            |

|      |               |          |          |                            |

|      | Vector Number | Bits 4-0 | Source   | Function                   |

|      | 64            | 00000    | Reserved | User Spurious Interrupt    |

|      | 65            | 00001    | INT1     | External Interrupt Input 1 |

|      | 66            | 00010    | INT2     | External Interrupt Input 2 |

|      | 67            | 00011    | INT3     | External Interrupt Input 3 |

|      | 68            | 00100    | INT4     | External Interrupt Input 4 |

|      | 69            | 00101    | TMR0     | Timer 0                    |

|      | 70            | 00110    | TMR1     | Timer 1                    |

|      | 71            | 00111    | TMR2     | Timer 2                    |

|      | 72            | 01000    | TMR3     | Timer 3                    |

|      | 73            | 01001    | UART1    | UART 1                     |

|      | 74            | 01010    | UART2    | UART 2                     |

|      | 75            | 01011    | PLIP     | PLIC 2KHz Periodic         |

|      |               |          |          |                            |

|      |               |          |          |                            |

|      |               |          |          |                            |

| Interru | nt Va         | ator     | Tabl     |                                   |

|---------|---------------|----------|----------|-----------------------------------|

| menu    | pi ve         | CLOI     | Iad      | le                                |

|         |               |          |          |                                   |

|         |               |          | _        |                                   |

|         |               |          |          |                                   |

|         | Vector Number | Bits 4-0 | Source   | Function                          |

|         | 76            | 01100    | PLIA     | PLIC Asynchronous                 |

|         | 77            | 01101    | USBO     | USB Endpoint 0                    |

|         | 78            | 01110    | US81     | USB Endpoint 1                    |

|         | 79            | 01111    | U\$82    | USB Endpoint 2                    |

|         | 80            | 10000    | U083     | USB Entpoint 3                    |

|         | 81            | 10001    | USB4     | USB Endpoint 4                    |

|         | 82            | 100/10   | US85     | USB Endpoint 5                    |

|         | 83            | 10011    | U\$86    | USB Endpoint 6                    |

|         | 84            | 10100    | US87     | USB Endpoint 7                    |

|         | 85            | 10101    | D64A     | DMA Controller                    |

|         | 86            | 10110    | ERx      | Ethernet Receiver                 |

|         | 87            | 10111    | ETx      | Ethernet Transmitter              |

|         | 88            | 11000    | ENTC     | Ethernet Module Non-time-critical |

|         | 89            | 11001    | QSP1     | Queued Serial Perpheral Interface |

|         | 90            | 11010    | INT5     | External Interrupt Input 5        |

|         | 91            | 11011    | INT6     | External Interrupt Input 6        |

|         | 92            | 11100    | \$1070   | Software Watchdog Timer Timeout   |

|         | 93            | 11101    | Reserved | Reserved                          |

|         | 94            | 11110    | Reserved | Reserved                          |

|         | 95            | 11111    | Reserved | Reserved                          |

#### Power Management

- In sleep mode the processor allows any interrupt condition to wake up the processor

Because it is a static design, sleep mode simply disables the clock to the processor's modules. When an interrupt occurs, execution is simply resumed from the point where the processor was placed into sleep mode

Stop mode is a scheward by cetting a bit in the

- Stop mode is achieved by setting a bit in the control register, which disables both the core and the peripherals. •

- In stop mode, the processor consumes very little power and is brought out of the stop mode through an external interrupt event. ٠

24

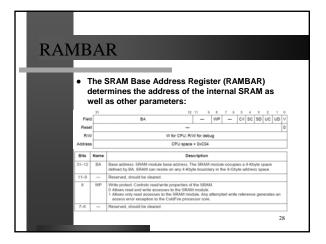

| Loca | l Memo                                                                                                                                                                                                                                                                      | ory    | - 5   | SRAM                       |                              |  |  |  |  |  |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|----------------------------|------------------------------|--|--|--|--|--|--|--|

|      | <ul> <li>The MCF5272 provides a local memory with the following parameters</li> <li>4K SRAM organized as 1K x 32 bits</li> <li>Sing-cycle access</li> <li>Programmable base address</li> <li>Ideal for use as system stack, or for storing critical code or data</li> </ul> |        |       |                            |                              |  |  |  |  |  |  |  |

|      | Address (using MOVEC)                                                                                                                                                                                                                                                       | Name   | Width | Description                | Reset Value                  |  |  |  |  |  |  |  |

|      | 0x002                                                                                                                                                                                                                                                                       | CACR   | 32    | Cache control register     | 0x0000                       |  |  |  |  |  |  |  |

|      | 0x004                                                                                                                                                                                                                                                                       | ACR0   | 32    | Access control register 0  | 0x0000                       |  |  |  |  |  |  |  |

|      | 0x005                                                                                                                                                                                                                                                                       | ACR1   | 32    | Access control register 1  | 0x0000                       |  |  |  |  |  |  |  |

|      | 0×C00                                                                                                                                                                                                                                                                       | ROMBAR | 32    | ROM base address register  | Uninitialized (except V = 0) |  |  |  |  |  |  |  |

|      | 0xC04                                                                                                                                                                                                                                                                       | RAMBAR | 32    | SRAM base address register | Uninitialized (except ∨ = 0) |  |  |  |  |  |  |  |

|      |                                                                                                                                                                                                                                                                             |        |       |                            | 25                           |  |  |  |  |  |  |  |

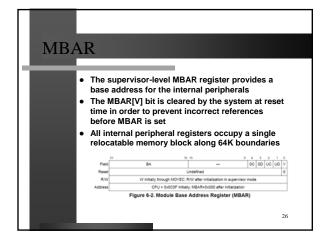

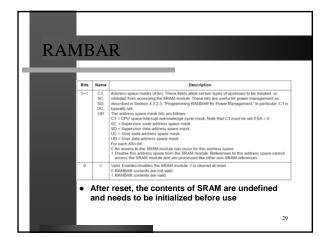

| Bits  | Field | Description                                                                        |

|-------|-------|------------------------------------------------------------------------------------|

| 31-16 | BA    | Base address. Defines the base address for a 64-Kbyte address range.               |

| 15-5  | -     | Reserved, should be cleared.                                                       |

| 4     | SC    | Setting masks supervisor code space in MBAR address range                          |

| 3     | SD    | Setting masks supervisor data space in MBAR address range                          |

| 2     | UC    | Setting masks user code space in MBAR address range                                |

| 1     | UD    | Setting masks user data space in MBAR address range                                |

| 0     | V     | Valid. Determines whether MBAR settings are valid.<br>0 MBAR contents are invalid. |

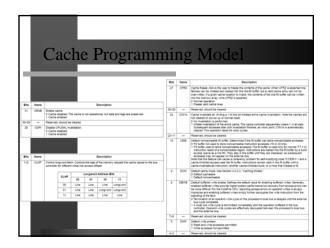

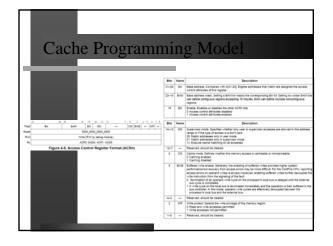

| Cache | • P    | rno                         | ra         | m      | m     | nin       | σ             | $\cdot \mathbf{M}$ | od       | el       |                           |           |  |        |               |    |                        |  |  |   |        |

|-------|--------|-----------------------------|------------|--------|-------|-----------|---------------|--------------------|----------|----------|---------------------------|-----------|--|--------|---------------|----|------------------------|--|--|---|--------|

| Juein | -      | 108                         | 100        |        |       |           | $\mathcal{D}$ | 1111               |          |          |                           |           |  |        |               |    |                        |  |  |   |        |

|       |        |                             |            |        |       |           |               |                    |          |          |                           |           |  |        |               |    |                        |  |  |   |        |

|       |        |                             |            |        |       |           |               |                    |          |          |                           |           |  |        |               |    |                        |  |  |   |        |

| A     | ddress | (using M                    | OVEC       | ) N    | ame   | Width     |               | Des                | criptio  | n        | Re                        | set Value |  |        |               |    |                        |  |  |   |        |

|       |        | 0x002                       |            |        |       | 0x002 C   |               |                    | 0x002 C  |          |                           | 0x002 C/  |  |        | 0x002 CACR 32 | 32 | Cache control register |  |  | 0 | 0x0000 |

|       |        | 0x004                       | A          | ACR0   | CR0   | ACR0      | ACR0          | ACR0               | 32       | Ā        | Access control register 0 |           |  | 0x0000 |               |    |                        |  |  |   |        |

|       |        | 0x005                       |            | A      | CR1   | 32        | A             | ccess con          | trol reg | gister 1 | 0x0000                    |           |  |        |               |    |                        |  |  |   |        |

|       |        |                             |            | -      |       |           | +             |                    |          |          | -                         |           |  |        |               |    |                        |  |  |   |        |

|       |        | 50 29                       | 28<br>CDPI | 27     | 26    |           | 24<br>NVA     | 23                 |          |          |                           | 16        |  |        |               |    |                        |  |  |   |        |

| Re    |        |                             | COPI       | wr rus |       |           |               | 0000_0000          |          |          |                           |           |  |        |               |    |                        |  |  |   |        |

| B     | w      | Write (R/W by debug module) |            |        |       |           |               |                    |          |          |                           |           |  |        |               |    |                        |  |  |   |        |

|       |        |                             |            |        | 10    |           |               | 7 6                |          |          | 2                         | 1 0       |  |        |               |    |                        |  |  |   |        |

| P     | eld    | -                           |            |        | CEIB  | DCM DE    | SWE           | -                  | DWP      | -        |                           | CLNF      |  |        |               |    |                        |  |  |   |        |

| Re    | set    |                             |            |        |       | 00000_00  | .000          | 0000_0000          |          |          |                           |           |  |        |               |    |                        |  |  |   |        |

| R     | w      |                             |            |        | V     | Wite (R/W | by d          | debug module       | )        |          |                           |           |  |        |               |    |                        |  |  |   |        |

|       | Rc     |                             |            |        |       |           | 0×0           | 02                 |          |          |                           |           |  |        |               |    |                        |  |  |   |        |

|       |        |                             | Figu       | re 4~  | 4. Ca | che Co    | ntro          | ol Registe         | r (CAC   | CR)      |                           |           |  |        |               |    |                        |  |  |   |        |

|       |        |                             |            |        |       |           |               |                    |          |          |                           |           |  |        |               |    |                        |  |  |   |        |

| SIM             |                                    |                                                                  |                             |                                                              |    |  |  |

|-----------------|------------------------------------|------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------|----|--|--|

|                 |                                    |                                                                  |                             |                                                              |    |  |  |

|                 |                                    |                                                                  |                             |                                                              |    |  |  |

|                 |                                    |                                                                  |                             |                                                              |    |  |  |

| MBAR<br>Offset  | [21:24]                            | [22:14]                                                          | [95:0]                      | [7:4]                                                        |    |  |  |

| 0×000           | Module                             | base address register (                                          | VEAR), after initialization | [p. 6-4]                                                     |    |  |  |

| 0x004           | System configuration is            | egister (SCR) [p. 6-5]                                           | System protection /         | egister (SPR) (p. 6-6)                                       |    |  |  |

| G×008           |                                    |                                                                  | agistar (P5/R) (p. 6-2)     |                                                              |    |  |  |

| 0+000           | Reser                              | Reserved Active low power register (ALPR) (p. 6                  |                             |                                                              |    |  |  |

| 0x010           |                                    | Device identification register (DIR) [p. 6-11]                   |                             |                                                              |    |  |  |

| 0x014-<br>0x01C |                                    | Reserved                                                         |                             |                                                              |    |  |  |

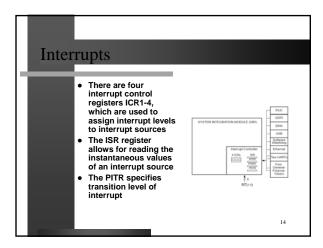

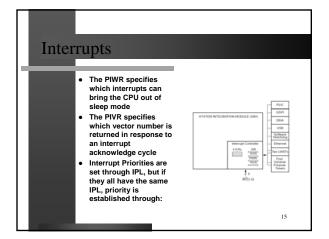

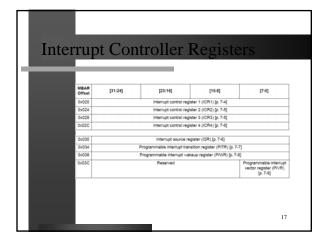

|                 |                                    | Interrupt Controller Registers                                   |                             |                                                              |    |  |  |

| 0×020           |                                    | Interrupt control register 1 (ICR1) (p. 7-4)                     |                             |                                                              |    |  |  |

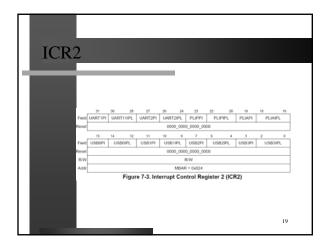

| 0+024           |                                    | interrupt control reg                                            | wwr.2 (ICR2) (p. 7-6)       |                                                              |    |  |  |

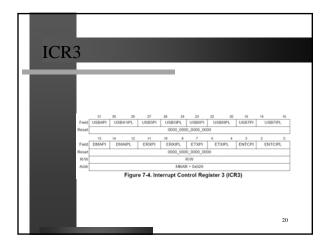

| 0×028           |                                    | interrupt control reg                                            | aler 3 (ICR3) [p. 7-6]      |                                                              |    |  |  |

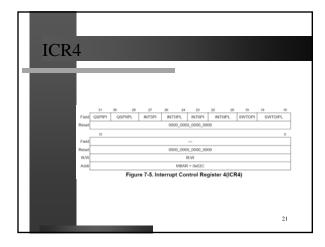

| 0x02C           |                                    | interrupt control reg                                            | ater 4 (ICR4) (p. 7-4)      |                                                              |    |  |  |

| 0+600           |                                    | Interrupt source re                                              | gater (ISR) (p. 7-6)        |                                                              |    |  |  |

| 0×004           |                                    |                                                                  | ation register (PITR) (p. 7 |                                                              |    |  |  |

| 0x008           | Pro                                |                                                                  | keup register (PWR) (p. 7   |                                                              |    |  |  |

| 0+030           |                                    | Reserved                                                         |                             | Programmable interrupt<br>vector register (PIVR)<br>[p. 7-8] |    |  |  |

|                 |                                    | Software Watchdog Registers                                      |                             |                                                              |    |  |  |

| 0x280           | Viatcholog reset referen<br>(p. 6- | Viatchdog reset reference register (VIRRR) Reserved<br>[3: 6-12] |                             |                                                              |    |  |  |

| 0.284           | Watchdog interrupt refer<br>(p. 6- |                                                                  | Res                         | erved                                                        |    |  |  |

| 0×288           | Watchdog counter regi              | ster (WCR) [p. 6-14]                                             | Res                         | erved                                                        | 34 |  |  |

|                 |                                    |                                                                  |                             | erved                                                        |    |  |  |

### System Integration Modul

- The System Integration Module provides overall control and arbitration of the bus and serves as the interface between the ColdFire core and the internal peripheral devices

- It provides the following features:

- Module base address register (MBAR) ٠

- Interrupt Controller

- Chip Select module and SDRAM controller interface •

- System protection (watchdog timer)

- Pin Assignment Register (PAR) • Power Management

- Bus Arbitration

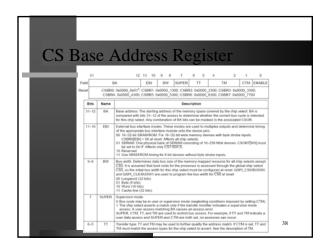

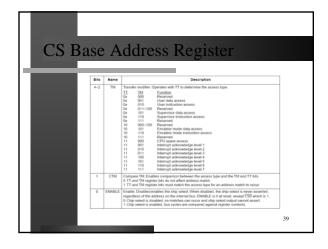

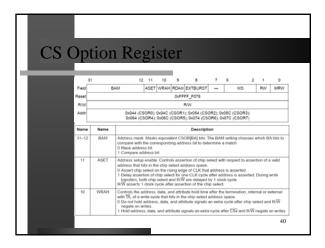

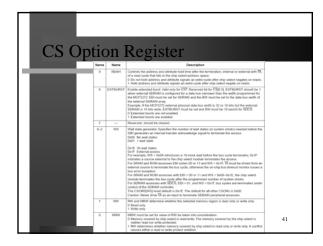

## Chip Select Module • The ColdFire provides · 8 dedicated chip selects Address masking for memories ranging from 4K to 2 GB • Programmable wait states and port sizes Programmable address setup and hold times SDRAM controller interface with CS7# Global chip select functionality CS0# used to access external boot ROM, in conjunction with BUSW[1:0]

36

35

| <b>a</b> 1 · a | 1 .     |       |                      |              |

|----------------|---------|-------|----------------------|--------------|

| Chip Se        | elect   | M     | odule                |              |

| Cinp be        | 1000    | TAT   | ouure                |              |

|                |         |       |                      |              |

|                | Offset  | Name  | Chip Select Register | Reset        |

|                | + 0x040 |       | CS base register 0   | 0x0000_0x011 |

|                | + 0x040 |       | CS option register 0 | 0xFFFF_F078  |

|                | + 0x048 |       | CS base register 1   | 0x0000_1300  |

|                | + 0x04C |       | CS option register 1 | 0xFFFF_F078  |

|                | + 0x050 | CSBR2 | CS base register 2   | 0x0000_2300  |

|                | + 0x054 | CSOR2 | CS option register 2 | 0xFFFF_F078  |

|                | + 0x058 | CSBR3 | CS base register 3   | 0x0000_3300  |

|                | + 0x05C | CSOR3 | CS option register 3 | 0xFFFF_F078  |

|                | + 0x060 | CSBR4 | CS base register 4   | 0x0000_4300  |

|                | + 0x064 | CSOR4 | CS option register 4 | 0xFFFF_F078  |

|                | + 0x068 | CSBR5 | CS base register 5   | 0x0000_5300  |

|                | + 0x06C | CSOR5 | CS option register 5 | 0xFFFF_F078  |

|                | + 0x070 | CSBR6 | CS base register 6   | 0x0000_6300  |

|                | + 0x074 | CSORE | CS option register 6 | 0xFFFF_F078  |

|                | + 0x078 | CSBR7 | CS base register 7   | 0x0000_7700  |

|                | + 0+070 | CSOR7 | CS option register 7 | 0xFFFF_F078  |

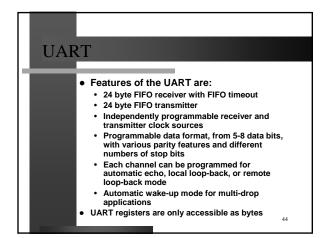

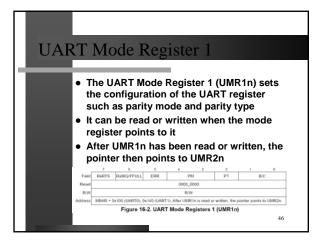

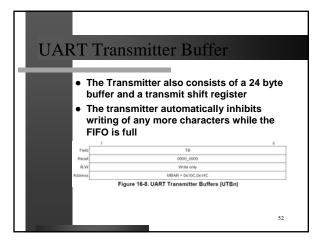

| UART | Pro     | D§      | gramn                                                                                          | ning    | Mo     | del   |    |

|------|---------|---------|------------------------------------------------------------------------------------------------|---------|--------|-------|----|

|      | MBAR C  | _       |                                                                                                |         |        | 1     |    |

|      | UARTS U |         | [21:24]                                                                                        | [23:14] | [16:4] | [7:4] |    |

|      | 0x11C   |         | (Read) Do not access. <sup>2</sup>                                                             |         | -      |       |    |

|      |         |         | UART divider lower<br>registers—(UDLn) (p.<br>10-14]                                           |         | -      |       |    |

|      | 0x120   | Ow 1610 | (Read) UART autobaut<br>register MSB(UABUH)<br>[p. 16-18]                                      |         |        |       |    |

|      |         |         | (Write) Do not access?                                                                         |         |        |       |    |

|      | 0x124   | Qx164   | (Read) UART autobaud<br>register LSB—(UABLn) (p.<br>16-18)                                     |         |        |       |    |

|      |         |         | (Write) Do not access <sup>2</sup>                                                             |         |        |       |    |

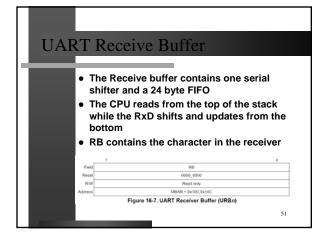

|      |         |         | UART Transmitter FIFO<br>registers(UTFn) (p. 16-5)                                             |         |        |       |    |

|      | 0x12C   | Dx16C   | UART Receiver FIFO<br>registers(URFit) (p.<br>16-5)                                            |         | -      |       |    |

|      | 0x130   | Ox170   | UART Fractional Precision<br>Divider Control negisters<br>(UFPDn) [p. 16-17]                   |         |        |       |    |

|      | 0x134   | Ox174   | (Read) UART input port<br>registers—(UIPn) (p.<br>16-18)                                       |         |        |       |    |

|      |         |         | (Write) Do not access. <sup>2</sup>                                                            |         |        |       |    |

|      | 0x138   | 0x178   | (Read) Do not access 2                                                                         |         |        |       |    |

|      |         |         | (Write) UART output port<br>bit set command<br>registers—(UOP1n <sup>3</sup> ) (p.<br>16-18)   |         |        |       |    |

|      | 0x13C   | Dx17C   | (Read) Do not access. <sup>2</sup>                                                             |         |        |       |    |

|      |         |         | (Write) UART output port<br>bit reset command<br>registers—(UOPDn <sup>3</sup> ) (p.<br>16-18) |         |        |       | 45 |

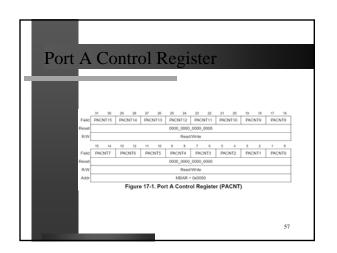

| PACN | T     |         |                                                                                                                                                 |    |

|------|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | Bits  | Name    | Description                                                                                                                                     |    |

|      | 31-30 | PACNT15 | Configure pin M3. If this pin is programmed to function as INTE, it is not available as a GPI0.<br>GPI0.<br>01 PM15<br>01 D04X11<br>1. Reserved |    |

|      | 29-28 | PACNT14 | Configure pin M2<br>00 PM-14<br>01 DREQ01<br>15 Reserved                                                                                        |    |

|      | 27-26 | PACNT13 | Configure pin L3<br>00 PAL3<br>01 DFSC3<br>1x Reserved                                                                                          |    |

|      | 25-24 | PACNT12 | Configure pin L2<br>00 PH (2<br>01 DFSC2<br>11: Reserved                                                                                        |    |

|      | 23-22 | PACNT11 | Configure pin L1<br>00 PA11<br>10 GPR-051<br>10 GSPL_C51<br>11 Reserved<br>11 Reserved                                                          |    |

|      | 21-20 | PACNT10 | Configure pin K5<br>00 PA10<br>01 DEEC0<br>1x Reserved                                                                                          |    |

|      | 19-18 | PACNT9  | Configure pin J3<br>00 FM/0<br>01 DONT0<br>1x Reserved                                                                                          | 58 |

|      |       |         |                                                                                                                                                 | _  |

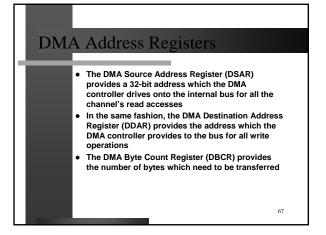

| DMA C            | ontr                                                    | olle                          | r                            |                      |                  |                       |                              |                         |

|------------------|---------------------------------------------------------|-------------------------------|------------------------------|----------------------|------------------|-----------------------|------------------------------|-------------------------|

| wh<br>ca<br>● Th | e 5272 p<br>lich sup<br>n be use<br>e DMA N<br>erations | ports m<br>ed for b<br>Mode R | nemory<br>lock-da<br>egister | -to-<br>ata r<br>cor | me<br>no<br>ntro | mory<br>ves<br>ols va | transfe<br>rious D<br>essing | ers that<br>MA<br>modes |

| 51<br>Field RESE | 30 29<br>T EN                                           |                               | _                            |                      |                  |                       | 20 19<br>RQM                 | 18 17 16                |

| Reset            |                                                         |                               | 0000_000                     | 0_0000               | _0000            | )                     |                              |                         |

| RW               |                                                         |                               |                              | R/W                  |                  |                       |                              |                         |

| 14               | 14 13                                                   | 12 10                         | • •                          | 7                    | 8                | 5 4                   |                              | 2,1 0                   |

| Field —          | DSTM                                                    | DSTT                          | DSTS                         | -                    | -                | SRCM                  | SRCT                         | SRCS                    |

| Reset 0          | 01                                                      | 1_00                          | 01                           | 0                    | 0                | 1                     | 1_01                         | 01                      |

| RW               |                                                         |                               |                              | R/W                  |                  |                       |                              |                         |

| Addr             |                                                         |                               | 1112110                      | t + 0x00             |                  |                       |                              |                         |

|                  |                                                         | Figure 10-                    | 1. DMA Mo                    | de Re                | gist             | er (DMF               | 0                            | 64                      |

| Etle a una a d | D.,              |       |       | ming Model                                      |    |

|----------------|------------------|-------|-------|-------------------------------------------------|----|

| Einemei        | . Pr             | ogra  | m     |                                                 |    |

|                |                  | - 0   |       | 0                                               |    |

|                |                  |       |       |                                                 |    |

|                | Offset           | Name  | Width | Description                                     |    |

|                | Cx840            | ECR   | 32    | Ethernet control register, (p. 11-12)           |    |

|                | 01844            | ER    | 32    | Interrupt event register, (p. 11-13)            |    |

|                | Cx848            | EMR   | 32    | Interrupt mask register, (p. 11-54)             |    |

|                | 0x840            | IVSR  | 32    | Interrupt vector status register, (p. 11-14)    |    |

|                | 0x850            | RDAR  | 32    | Receive descriptor active register, (p. 11-15)  |    |

|                | 0x854            | TDAR  | 32    | Transmit descriptor active register, (p. 11-16) |    |

|                | Cx880            | MMFR  | 32    | Mil management frame register, (p. 11-17)       |    |

|                | 0x884            | MSCR  | 32    | MII speed control register, (p. 11-18)          |    |

|                | DVBCC            | FROR  | 32    | FIFO receive bound register, [p. 11-20]         |    |

|                | 0x800            | FRSR  | 32    | FIFO receive start register. (p. 11-20)         |    |

|                | 0+800            | TFSR  | 32    | FIFO transmit start register, (p. 11-22)        |    |

|                | 0x8E4            | TPWR  | 32    | Transmit FIFO watermark, (p. 11-21)             |    |

|                | 0x944            | RCR   | 32    | Receive control register, [p. 11-23]            |    |

|                | 01948            | MFLR  | 32    | Maximum frame length register, (p. 11-24)       |    |

|                | 0x984            | TCR   | 32    | Transmit control register, (p. 11-25)           |    |

|                | 0×C00            | MALR  | 32    | Lower 32-bits of MAC address                    |    |

|                | 0xC04            | MAUR  | 32    | Upper 16-bits of MAC address                    |    |

|                | 0xC08            | HTUR  | 32    | Upper 32-bits of hash table, (p. 11-27)         |    |

|                | DVCDC            | HTLR  | 32    | Lower 32-bits of hash table, (p. 11-27)         |    |

|                | 0xC10            | ERDSR | 32    | Pointer to receive descriptor ring, (p. 11-28)  |    |

|                | 0xC14            | ETDSR | 32    | Pointer to transmit descriptor ring. (p. 11-29) |    |

|                | OxC18            | EMRER | 32    | Maximum receive buffer size, (p. 11-29)         |    |

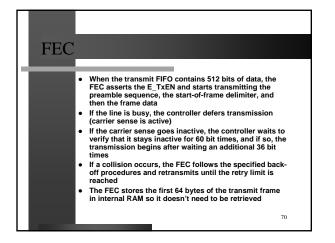

|                | 0xC40 -<br>0xC97 | 87/70 | 32    | FIFO RAM space                                  | 71 |

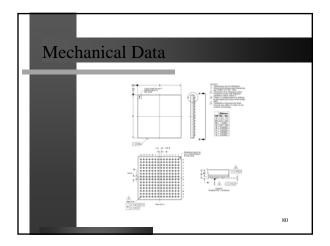

| Mecha | n   | ic                      | ิลโ              | D                | )at                   | a                  |                   |               |                 |                 |                       |                           |                       |                      |                      |  |

|-------|-----|-------------------------|------------------|------------------|-----------------------|--------------------|-------------------|---------------|-----------------|-----------------|-----------------------|---------------------------|-----------------------|----------------------|----------------------|--|

| meene | *11 | 10                      | ~                |                  | u                     |                    |                   |               |                 |                 |                       |                           |                       |                      |                      |  |

|       | _   |                         |                  |                  |                       |                    |                   |               |                 |                 |                       |                           |                       |                      |                      |  |

|       |     |                         | 2                | 3                |                       |                    | 4                 | 7             |                 |                 | 10                    | 11                        | 12                    | 13                   |                      |  |

|       |     | 88453                   | opened.          | 16               | 20                    | 1140<br>100        | 12                | 02V<br>05     | 12              | 102             | ****                  | +157<br>100-127<br>550-11 | 252                   | 222                  | 122                  |  |

|       |     | 100                     | mend             | 87800            | 짦                     | 420                | 4177<br>11        | 0207<br>04    | -127            | 1045            | 77                    | +12/<br>30+71             | 4.V<br>30+0           | 1048<br>1048<br>1040 | all'<br>IDAY<br>IDAN |  |

|       | c   | 4172                    | P971             | 10434            | 10%/<br>#970,4        | 421                | +10               | 0.172r<br>0.0 | 87              | (10)            | +14/<br>M=13/<br>M=12 | #11/<br>96=0              | 4)<br>1100            | 49<br>1047<br>1047   | 10                   |  |

|       | 0   | 143V<br>1580,500        | 140<br>100.75    | PERS .           | 1920<br>19204         | 100/               | +12               | 417           | +16             | +15             | -0                    | 214                       | +10<br>10×37<br>10×37 | IDOAE                | 10,000               |  |

|       |     | - ndi<br>una mo         | nali<br>Usa Yudu | saki<br>usa susa | rull'<br>Use re       | 142                | 1657              | -             |                 | +22             | 215                   | #15/<br>#110              | 112                   | 403                  | 180.4                |  |

|       | ,   | 108,0*                  | 108,0            | 72               | HEY5                  | 100                | 100               |               | 940             | -10             | ×90                   | 812F<br>#170              | 104'<br>18            | 105V<br>105          | 100<br>210           |  |

|       | 6   | 100,000                 | 100,000          | 1968<br>UR10,0.8 | ret                   | 100                | - 040             | 010           | - 040           | - 010           | V90                   | 611V<br>#C11              | 427)<br>411           | 429<br>512           | 129<br>20            |  |

|       |     | 1917<br>1912,010        | uRn              | ullin            | 1907<br>UM10_110      | -100               |                   | - 000         | 940             | 940             | ×90                   | 8107<br>#110              | 908a-1                | 10547<br>2010        | 1100<br>1100         |  |

|       |     | 18,04                   | 100              | 240¥<br>000070   | and with the          | -10                | - 10              |               | -               | 100             | -10                   | - 1                       | -16                   | -9                   | tond                 |  |

|       | ×   | unit_no                 | arcia            | outer            | 00/10<br>UR1(10       | na10/<br>oneuti    | Nex (1/2)<br>1911 | -100          | -00             | 200<br>8004     | 111                   | 63<br>#13                 | 14/<br>958            | 05<br>853            | 00/<br>#18           |  |

|       |     | 1411/<br>099_011        | 14/2<br>1912     | #119<br>19103    | PACT<br>PACT<br>OPSC1 | san cur<br>subri   | 110               | 4,7054        | #810/<br>6,7101 | 1114            | 1,00                  | -08                       | 107<br>FCD            | 10<br>PC1            | 12                   |  |

|       |     | 1,000<br>0001,001       | 200              | 637-5%           | 295<br>108,008        | 0181,130<br>81(14) | 10170             | 1,000         | 1995<br>6,7-62  | 1919<br>6,0001  | 0.000                 | 158                       | 451                   | 8.0455               | 0.404                |  |

|       |     | 00471                   | (m1              | 103              | 1004_000/1<br>#585,   | Park_0/0           | 1,100             | 6,0004        | 260<br>6_043    | 14 Qr<br>()     | 6,000                 | 63                        | SALUE<br>TRA          | 188                  | 12                   |  |

|       |     | AUT<br>00P-030<br>00R13 | 197              | 872              | 007_04                | FMM 0473<br>15671  | 1,05              | 4,440         | 1,749           | 1411/<br>6,0103 | HETS'<br>LUNC         | -02                       | राज                   | 8.0                  | 45                   |  |

|       |     |                         |                  | F                | igure 2               | 2-1. MC            | F5272 P           | hinout        | (196 )          | APE             | GA)                   |                           |                       |                      |                      |  |

| Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |                                                                |                                                       |                      |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------------------------|-------------------------------------------------------|----------------------|------|

| Rating         Symbol         Value         Vol           Supply voltage         Vp0         +0.5 to +4.0         V           Maintum operating voltage         Vp0         +3.6         V           Minimum operating voltage         Vp0         +3.6         V           Storage temperature range         Vp         -0.5 to +5.5         V           Storage temperature range         Tag         -65 to 150         °C                                                                                       | Electr    | ical Character                                                 | ristic                                                | S                    |      |

| Supply voltage         Vpo         -0.3 to +4.0         V           Maximum operating voltage         Vpo         +3.6         V           Minimum operating voltage         Vpo         +3.6         V           Intrimum operating voltage         Vpo         +3.6         V           Intrimum operating voltage         Vpo         +3.6         V           Storage temperature range         Vp         -0.5 to +5.5         V           Storage temperature range         Teg         -65 to 150         °C |           |                                                                |                                                       | ~                    |      |

| Supply voltage         Vpo         -0.3 to +4.0         V           Maximum operating voltage         Vpo         +3.6         V           Minimum operating voltage         Vpo         +3.6         V           Intrimum operating voltage         Vpo         +3.6         V           Intrimum operating voltage         Vpo         +3.6         V           Storage temperature range         Vp         -0.5 to +5.5         V           Storage temperature range         Teg         -65 to 150         °C |           |                                                                |                                                       |                      |      |

| Supply voltage         Vpo         -0.3 to +4.0         V           Maximum operating voltage         Vpo         +3.6         V           Minimum operating voltage         Vpo         +3.6         V           Intinuum operating voltage         Vpo         +3.6         V           Intinuum operating voltage         Vpo         +3.6         V           Storage temperature range         Vp         -0.5 to +5.5         V           Storage temperature range         Tpg         -65 to 150         °C |           |                                                                |                                                       |                      |      |

| Supply voltage         Vpo         -0.3 to +4.0         V           Maximum operating voltage         Vpo         +3.6         V           Minimum operating voltage         Vpo         +3.6         V           Intinuum operating voltage         Vpo         +3.6         V           Intinuum operating voltage         Vpo         +3.6         V           Storage temperature range         Vp         -0.5 to +5.5         V           Storage temperature range         Tpg         -65 to 150         °C |           |                                                                |                                                       |                      |      |

| Supply voltage         Vpo         -0.3 to +4.0         V           Maximum operating voltage         Vpo         +3.6         V           Minimum operating voltage         Vpo         +3.6         V           Intinuum operating voltage         Vpo         +3.6         V           Intinuum operating voltage         Vpo         +3.6         V           Storage temperature range         Vp         -0.5 to +5.5         V           Storage temperature range         Tpg         -65 to 150         °C |           |                                                                |                                                       |                      |      |

| Supply voltage         Vpo         -0.3 to +4.0         V           Maximum operating voltage         Vpo         +3.6         V           Minimum operating voltage         Vpo         +3.6         V           Intinuum operating voltage         Vpo         +3.6         V           Intinuum operating voltage         Vpo         +3.6         V           Storage temperature range         Vp         -0.5 to +5.5         V           Storage temperature range         Tpg         -65 to 150         °C |           |                                                                |                                                       |                      |      |

| Maximum operating votage         V <sub>50</sub> 43.6         V           Minimum operating votage         V <sub>50</sub> 43.0         V           Input votage         V <sub>60</sub> 43.5 to 45.5         V           Storage temperature range         V <sub>60</sub> 43.5 to 150         °C                                                                                                                                                                                                                  |           | Rating                                                         | \$ymbol                                               | Value                | Unit |

| Moneum operating voltage         V <sub>DD</sub> +3.0         V           Input voltage         V <sub>In</sub> +0.5 to +5.5         V           Storage temperature range         T <sub>edp</sub> -45 to 150         °C                                                                                                                                                                                                                                                                                           |           | naki unitana                                                   | Vno                                                   | -0.3 to + 4.0        | V    |

| іяры voltage V <sub>in</sub> 40.5 to 45.5 V<br>Бтогаде інтерентине range T <sub>arg</sub> 45 to 150 °C                                                                                                                                                                                                                                                                                                                                                                                                              | Sup       | ppry vonage                                                    |                                                       |                      |      |

| Storage temperature range T <sub>arg</sub> -65 to 150 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |                                                                |                                                       | +3.6                 | v    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ma        | ximum operating voltage                                        | V <sub>DD</sub>                                       |                      |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ma        | kimum operating voltage                                        | V <sub>DD</sub><br>V <sub>DD</sub>                    | +3.0                 | v    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ma<br>Min | imum operating voltage<br>imum operating voltage<br>ut voltage | V <sub>DD</sub><br>V <sub>DD</sub><br>V <sub>in</sub> | +3.0<br>-0.5 to +5.5 | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ma<br>Min | imum operating voltage<br>imum operating voltage<br>ut voltage | V <sub>DD</sub><br>V <sub>DD</sub><br>V <sub>in</sub> | +3.0<br>-0.5 to +5.5 | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ma<br>Min | imum operating voltage<br>imum operating voltage<br>ut voltage | V <sub>DD</sub><br>V <sub>DD</sub><br>V <sub>in</sub> | +3.0<br>-0.5 to +5.5 | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ma<br>Min | imum operating voltage<br>imum operating voltage<br>ut voltage | V <sub>DD</sub><br>V <sub>DD</sub><br>V <sub>in</sub> | +3.0<br>-0.5 to +5.5 | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ma<br>Min | imum operating voltage<br>imum operating voltage<br>ut voltage | V <sub>DD</sub><br>V <sub>DD</sub><br>V <sub>in</sub> | +3.0<br>-0.5 to +5.5 | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ma<br>Min | imum operating voltage<br>imum operating voltage<br>ut voltage | V <sub>DD</sub><br>V <sub>DD</sub><br>V <sub>in</sub> | +3.0<br>-0.5 to +5.5 | V    |